54ac11533, 74ac11533

octal d-类型 transparent latches

和 3-状态 输出

scas004 – d2957, july 1987 – 修订 april 1993

邮递 办公室 盒 655303

•

达拉斯市, 德州 75265

版权

1993, 德州 器械 组成公司的

2–1

•

8-latches 在 一个 单独的 包装

•

3-状态 总线-驱动 反相的 输出

•

全部 并行的 进入 为 加载

•

缓冲 控制 输入

•

流动-通过 architecture optimizes

pcb 布局

•

中心-管脚 v

CC

和 地 配置

降低 高-速 切换 噪音

•

EPIC

t

(增强-效能 implanted

cmos) 1-

m

m 处理

•

500-毫安 典型 获得-向上 免除 在 125

°

C

•

包装 选项 包含 塑料

小-外形 包装, 陶瓷的 碎片

carriers, 和 标准 塑料 和 陶瓷的

300-mil dips

描述

这些 8-位 latches 特性 3-状态 输出

设计 specifically 为 驱动 高级地 电容的

或者 相当地 低-阻抗 负载. 它们 是

特别 合适的 为 implementing 缓存区

寄存器, i/o 端口, 双向的 总线 驱动器, 和

working 寄存器.

这 第八 latches 的 这

′

ac11533 是 transparent

d-类型 latches. 当 这 使能 (c) 是 高, 这

Q

输出 将 follow 这 complements 的 这 (d)

输入. 当 这 输出 控制 oc是 带去 低,

这 q输出 将 是 latched. 这

′

ac11533 是

functionally 相等的 至 这

′

ac11373 除了 为

having inverted 输出.

一个 缓冲 输出-控制 (oc) 输入 能 是 使用

至 放置 这 第八 输出 在 也 一个 正常的 逻辑

状态 (高 或者 低 逻辑 水平) 或者 一个 高-

阻抗 状态. 在 这 高-阻抗 状态,

这 输出 neither 加载 也不 驱动 这 总线 线条 significantly. 这 高-阻抗 第三 状态 和 增加 驱动

提供 这 能力 至 驱动 这 总线 线条 在 一个 总线-有组织的 系统 没有 需要 为 接口 或者 拉-向上

组件.

这 输出 控制 (oc

) 做 不 影响 这 内部的 行动 的 这 latches. old 数据 能 是 retained 或者 新

数据 能 是 entered 当 这 输出 是 止.

这 54ac11533 是 典型 为 运作 在 这 全部 军队 温度 范围 的 –55

°

c 至 125

°

c. 这

74ac11533 是 典型 为 运作 从 – 40

°

c 至 85

°

c.

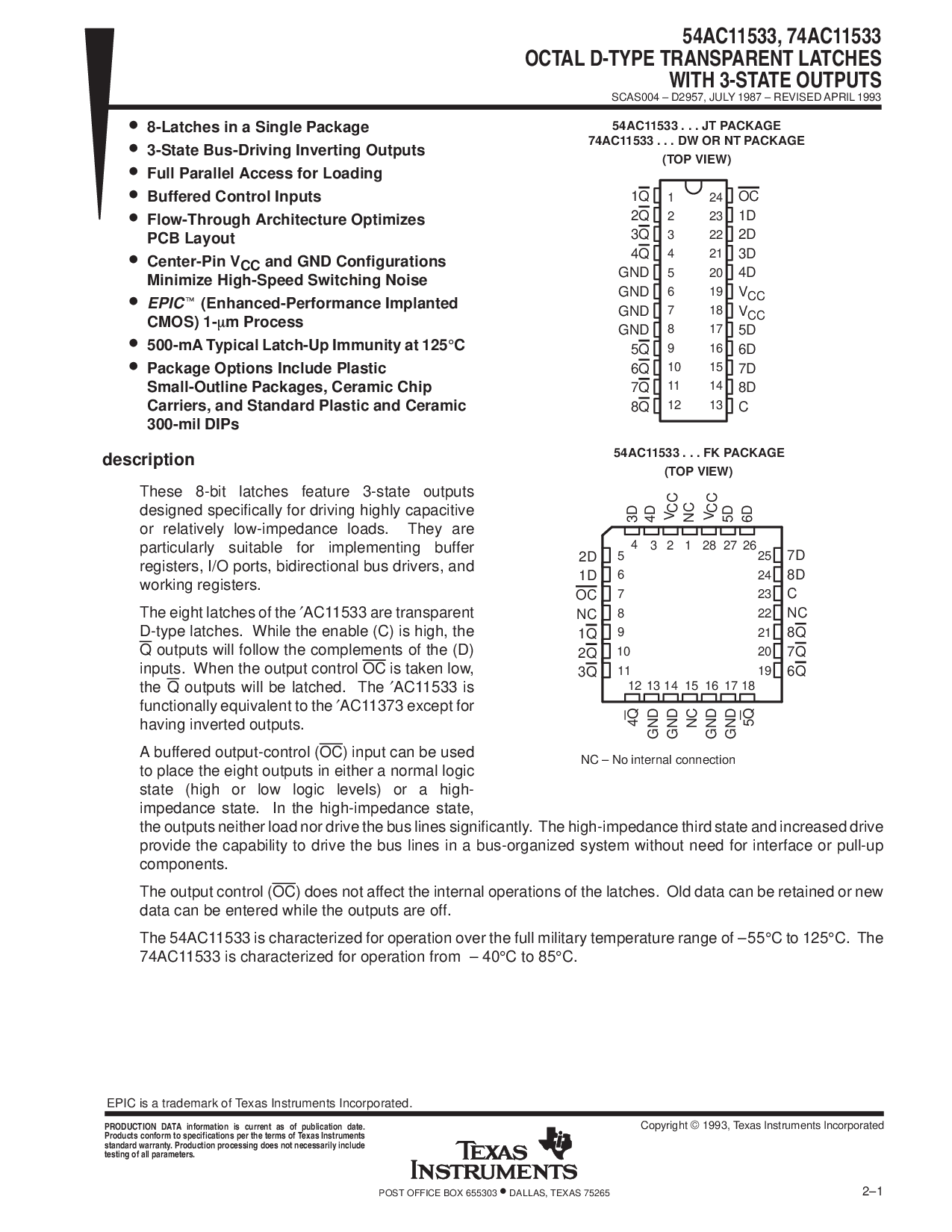

1

2

3

4

5

6

7

8

9

10

11

12

24

23

22

21

20

19

18

17

16

15

14

13

1Q

2Q

3Q

4Q

地

地

地

地

5Q

6Q

7Q

8Q

OC

1D

2D

3D

4D

V

CC

V

CC

5D

6D

7D

8D

C

54AC11533 . . . jt 包装

74AC11533 . . . dw 或者 nt 包装

(顶 视图)

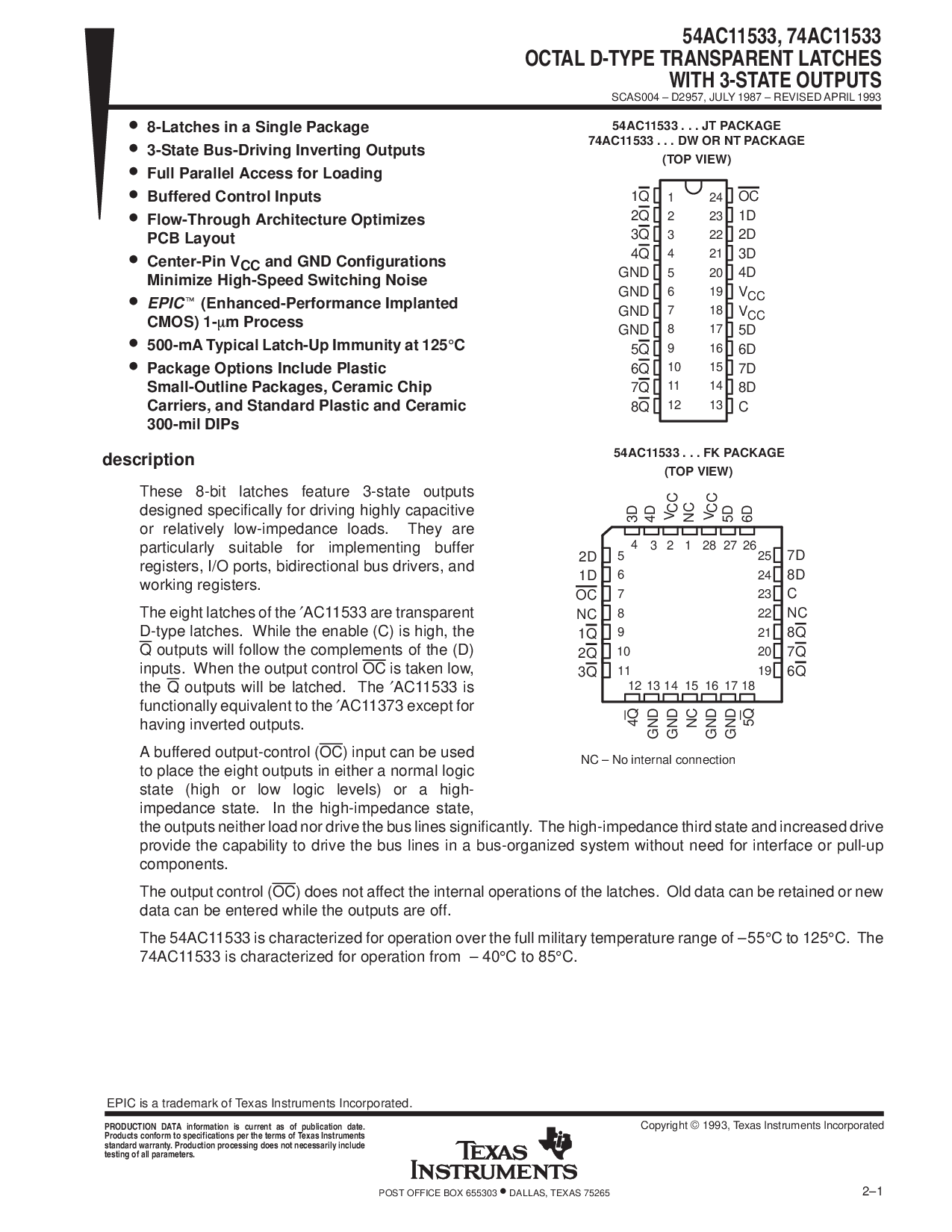

321

13 14

5

6

7

8

9

10

11

7D

8D

C

NC

8Q

7Q

6Q

2D

1D

OC

NC

1Q

2Q

3Q

4

15 16 17 18

地

地

NC

地

地

5Q

3D

4D

NC

54AC11533 . . . fk 包装

(顶 视图)

28 27 26

25

24

23

22

21

20

19

12

4Q

5D

6D

CC

V

CC

V

nc – 非 内部的 连接

生产 数据 信息 是 电流 作 的 发行 日期.

产品 遵从 至 规格 每 这 条款 的 德州 器械

标准 保用单. 生产 处理 做 不 必然地 包含

测试 的 所有 参数.

epic 是 一个 商标 的 德州 器械 组成公司的.