rev. B

信息 陈设 用 相似物 设备 是 相信 至 是 精确 和

可依靠的. 不管怎样, 非 责任 是 assumed 用 相似物 设备 为 它的

使用, 也不 为 任何 infringements 的 专利权 或者 其它 权利 的 第三 部

这个将结果从它的使用.非执照是准予用牵涉或者

否则 下面 任何 专利权 或者 专利权 权利 的 相似物 设备.

一个

adsp-21065l

一个 技术 方法, p.o. 盒 9106, norwood, 毫安 02062-9106, 美国

电话: 781/329-4700 world 宽 网 站点: http://www.相似物.com

传真: 781/326-8703 © 相似物 设备, inc., 2000

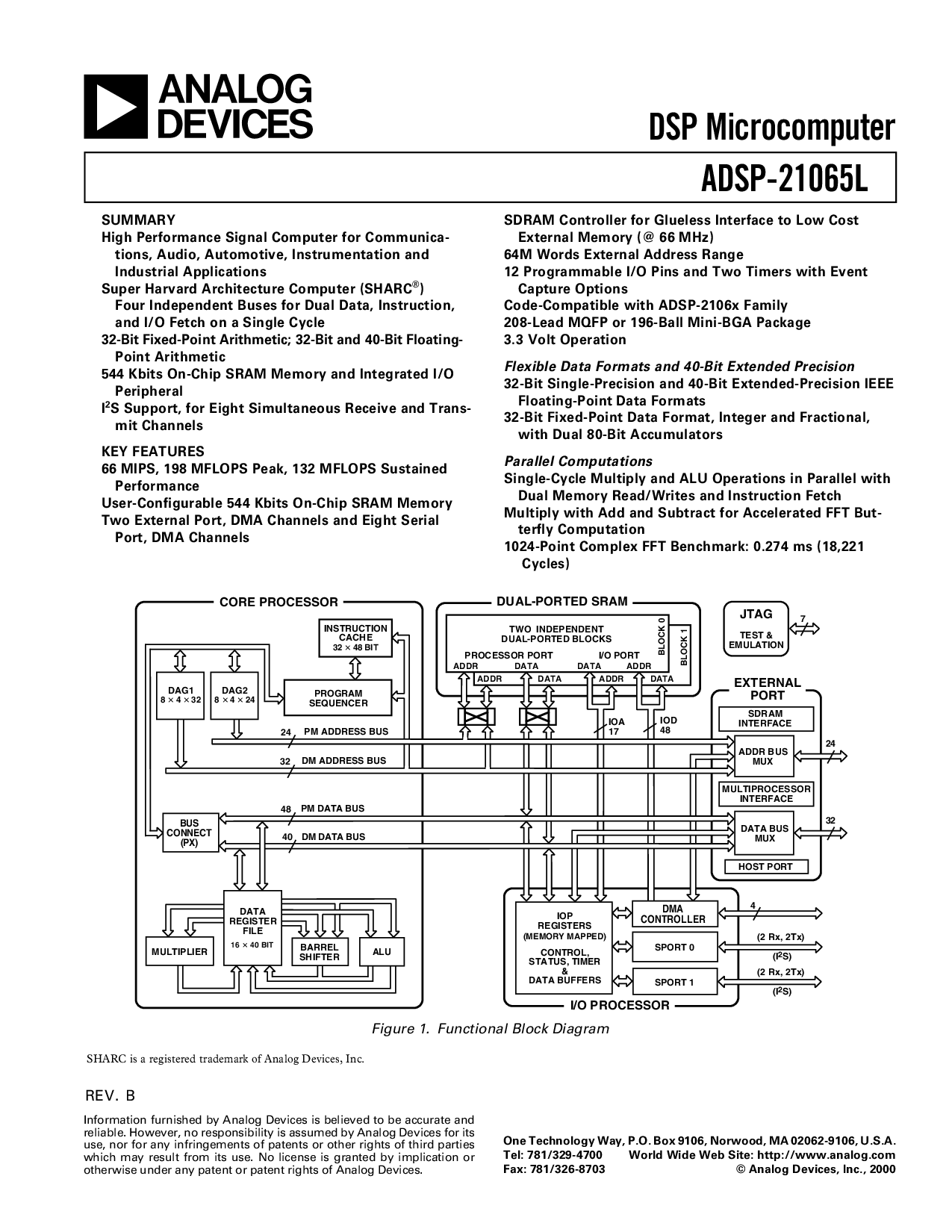

dsp microcomputer

SUMMARY

高 效能 信号 计算机 为 communica-

tions, 音频的, automotive, 仪器 和

工业的 产品

超级的 harvard architecture 计算机 (sharc

®

)

四 独立 buses 为 双 数据, 操作指南,

和 i/o fetch 在 一个 单独的 循环

32-位 fixed-要点 arithmetic; 32-位 和 40-bit floating-

要点 arithmetic

544 kbits 在-碎片 sram 记忆 和 整体的 i/o

附带的

I

2

s 支持, 为 第八 同时发生的 receive 和 trans-

mit 途径

关键 特性

66 mips, 198 mflops 顶峰, 132 mflops sustained

效能

用户-configurable 544 kbits 在-碎片 sram 记忆

二 外部 端口, dma 途径 和 第八 串行

端口, dma 途径

sdram 控制 为 glueless 接口 至 低 费用

外部 记忆 (@ 66 mhz)

64m words 外部 地址 范围

12 可编程序的 i/o 管脚 和 二 计时器 和 事件

俘获 选项

代号-兼容 和 adsp-2106x 家族

208-含铅的 mqfp 或者 196-球 迷你-bga 包装

3.3 volt 运作

有伸缩性的 数据 formats 和 40-位 扩展 精确

32-位 单独的-精确 和 40-位 扩展-精确 ieee

floating-要点 数据 formats

32-位 fixed-要点 数据 format, integer 和 fractional,

和 双 80-位 accumulators

并行的 computations

单独的-循环 乘以 和 alu 行动 在 并行的 和

双 记忆 读/写 和 操作指南 fetch

乘以 和 增加 和 减去 为 accelerated fft 但是-

terfly computation

1024-要点 complex fft benchmark: 0.274 ms (18,221

循环)

sport 1

4

IOP

寄存器

(记忆 编排)

控制,

状态, 计时器

&放大;

数据 缓存区

i/o 处理器

操作指南

CACHE

32

48 位

数据

地址

二 独立

双-ported blocks

处理器 端口 i/o 端口

块 0

块 1

JTAG

测试 &放大;

EMULATION

7

host 端口

地址 总线

MUX

IOA

17

IOD

48

MULTIPROCESSOR

接口

双-ported sram

外部

端口

数据 总线

MUX

32

24

24

pm 地址 总线

dm 地址 总线

pm 数据 总线

dm 数据 总线

总线

连接

(px)

数据

寄存器

文件

16

40 位

BARREL

SHIFTER

ALU乘法器

32

48

40

核心 处理器

DMA

控制

程序

SEQUENCER

DAG2

8

4

24

SDRAM

接口

(i

2

s)

(2 rx, 2tx)

(2 rx, 2tx)

(i

2

s)

sport 0

DAG1

8

4

32

数据 数据

数据

地址

地址

地址

图示 1. 函数的 块 图解

sharc 是 一个 注册 商标 的 相似物 设备, 公司