m54/74hc563

M54/74hc573

October 1993

HC563 反相的 - HC573 非 反相的

OCTAL d-类型 获得 和 3 状态 输出

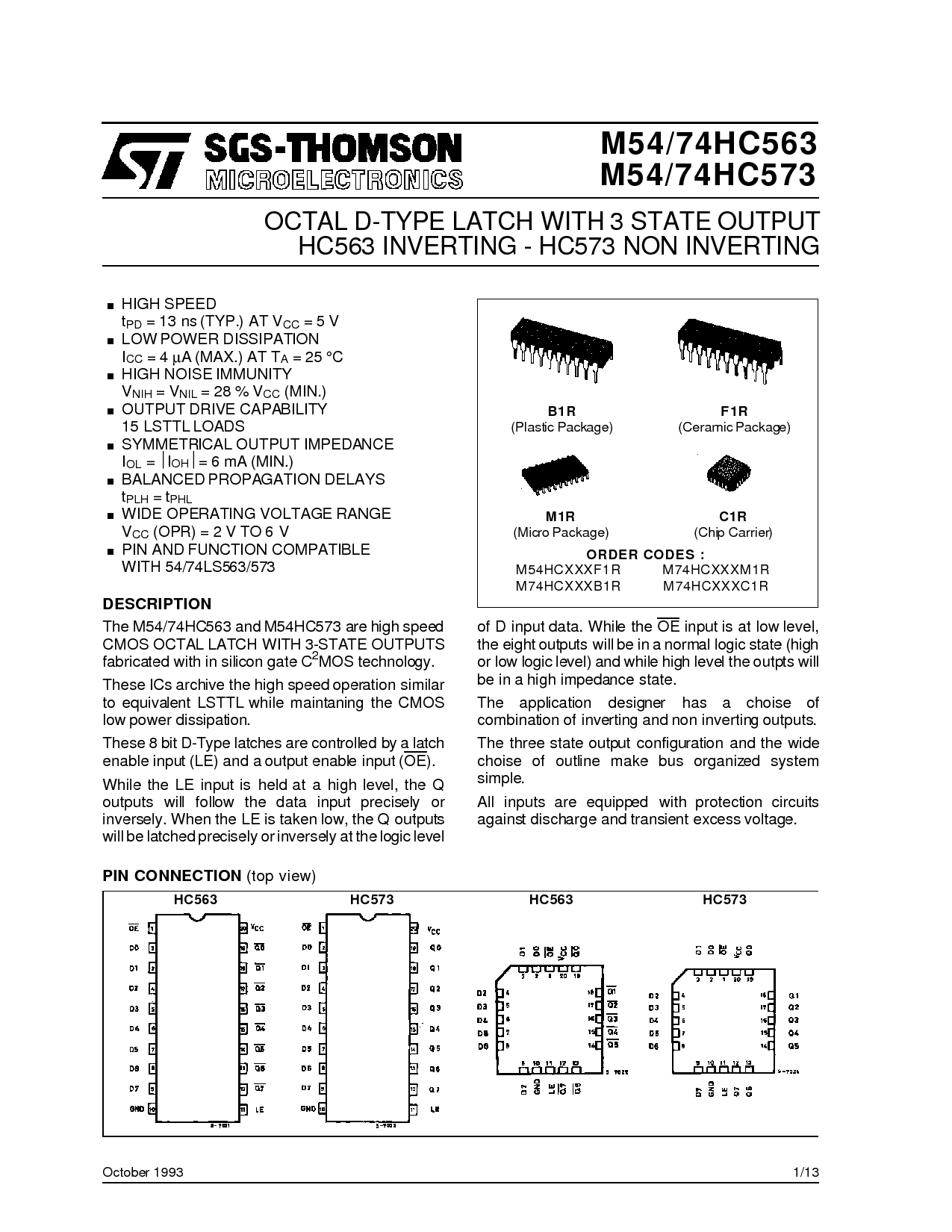

B1R

(塑料 包装)

顺序 代号 :

M54HCXXXF1R M74HCXXXM1R

M74HCXXXB1R M74HCXXXC1R

F1R

(陶瓷的 包装)

M1R

(微观的 包装)

C1R

(碎片 运输车)

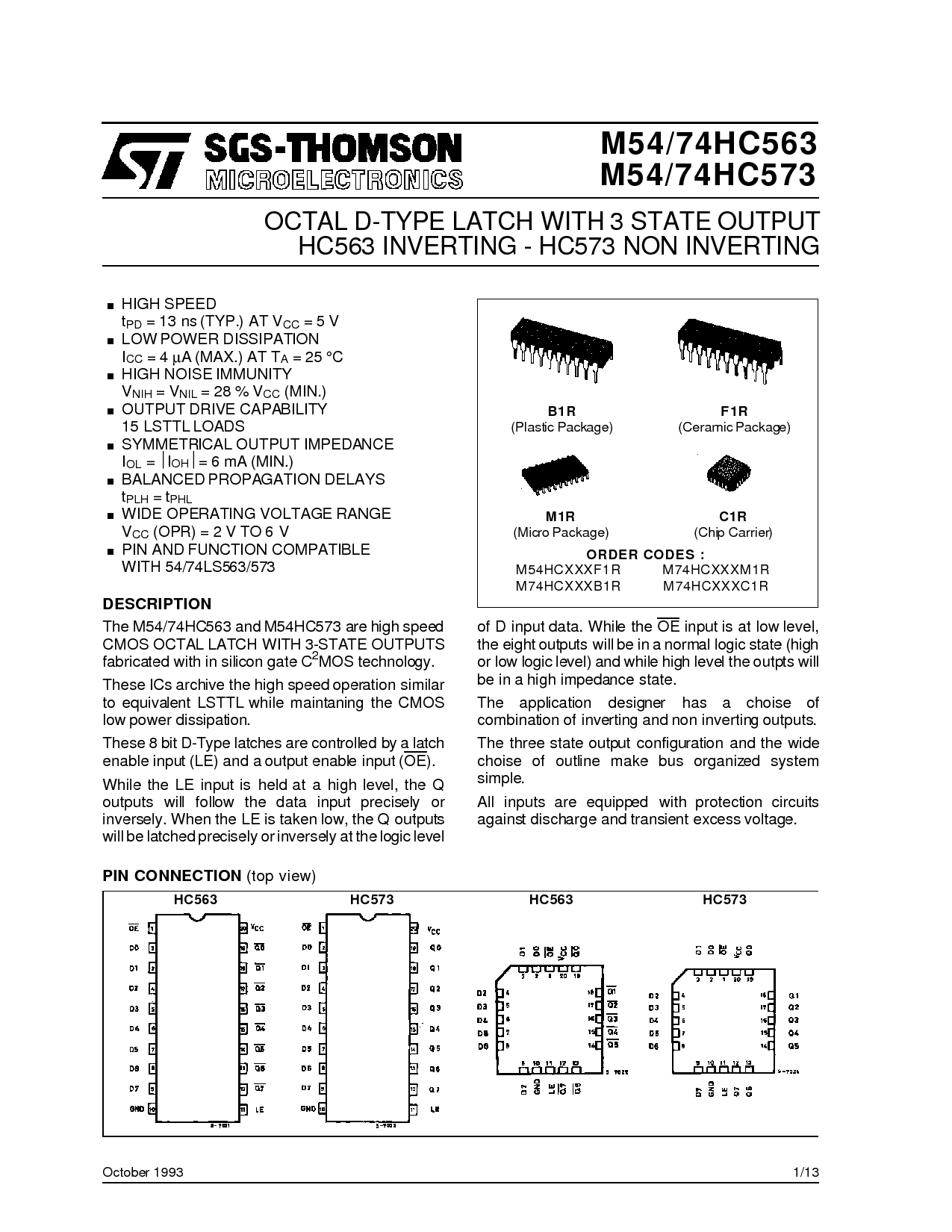

管脚 CONNECTI在

(顶 视图)

.

高 速

t

PD

= 13 ns (典型值.) 在 V

CC

=5V

.

低 电源 消耗

I

CC

=4

µ

一个 (最大值.) 在 T

一个

=25

°

C

.

高 噪音 免除

V

NIH

=V

NIL

=28%V

CC

(最小值.)

.

输出 驱动 能力

15 LSTTL 负载

.

对称的 输出 阻抗

I

OL

=

I

OH

= 6 毫安 (最小值.)

.

保持平衡 传播 延迟

t

PLH

=t

PHL

.

宽 运行 电压 范围

V

CC

(opr) = 2 V 至 6 V

.

管脚 和 函数 兼容

和 54/74ls563/573

DESCRIPTI在

这 m54/74hc563 和 M54HC573 是 高 速

CMOS OCTAL 获得 和 3-状态 输出

fabricated 和 在 硅 门 C

2

MOS 技术.

这些 ICs archive 这 高 速 运作 类似的

至 相等的 LSTTL 当 maintaning 这 CMOS

低 电源 消耗.

这些 8 位 d-类型 latches 是 控制 用 一个 获得

使能 输入 (le) 和 一个 输出 使能 输入 (oe).

当 这 LE 输入 是 使保持 在 一个 高 水平的, 这 Q

输出 将 follow 这 数据 输入 precisely 或者

inversely. 当 这 LE 是 带去 低, 这 Q 输出

将 是 latched precisely 或者 inversely 在 这 逻辑 水平的

的 D 输入 数据. 当 这 OE 输入 是 在 低 水平的,

这 第八 输出 将 是 在 一个 正常的 逻辑 状态 (高

或者 低 逻辑 水平的) 和 当 高 水平的 这 outpts 将

是 在 一个 高 阻抗 状态.

这 应用 设计者 有 一个 choise 的

结合体 的 反相的 和 非 反相的 输出.

这 三 状态 输出 配置 和 这 宽

choise 的 外形 制造 总线 有组织的 系统

简单的.

所有 输入 是 配备 和 保护 电路

相反 释放 和 瞬时 excess 电压.

HC563 HC573 HC563 HC573

1/13