整体的

电路

系统, 公司

ICS93705

0418c—08/08/02

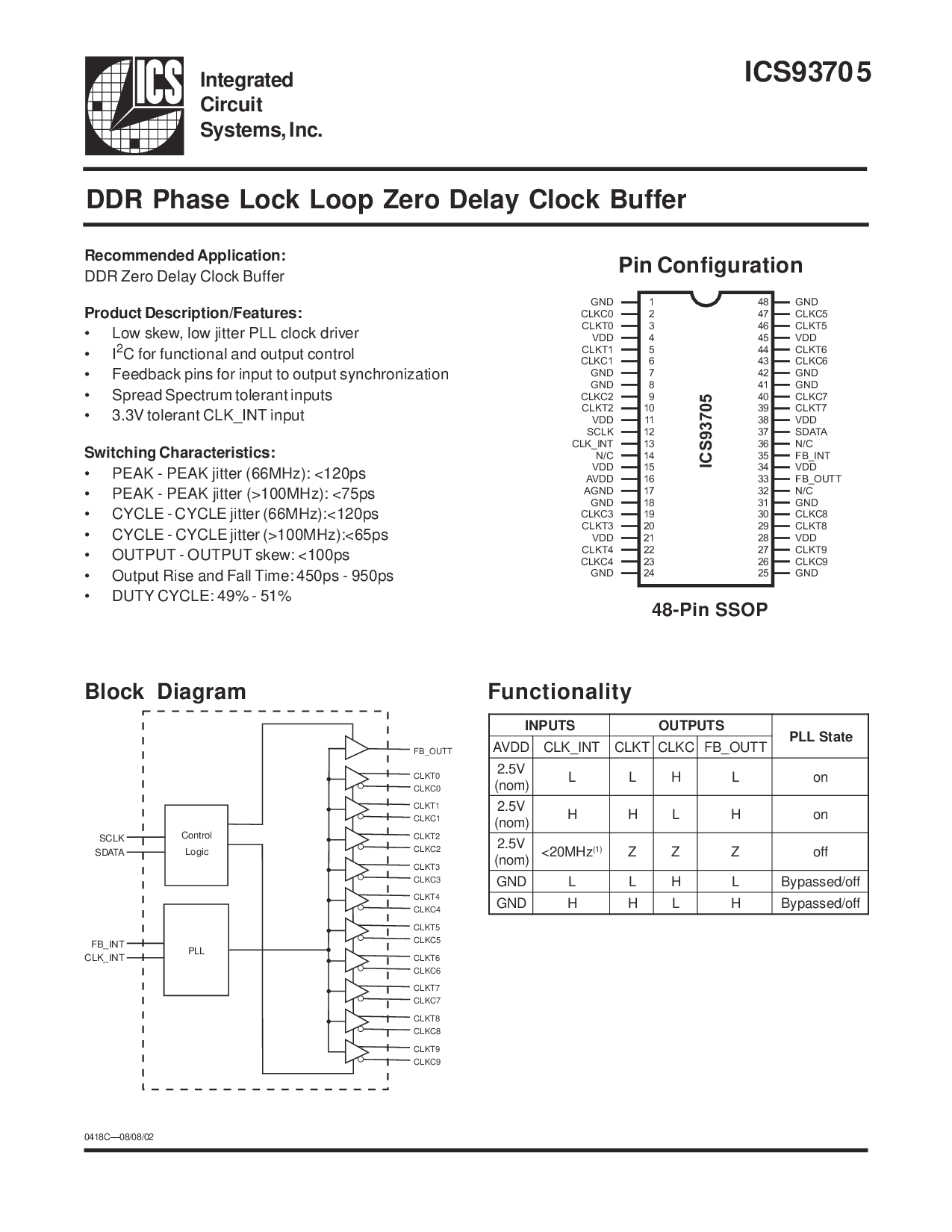

块 图解

ddr 阶段 锁 循环 零 延迟 时钟 缓存区

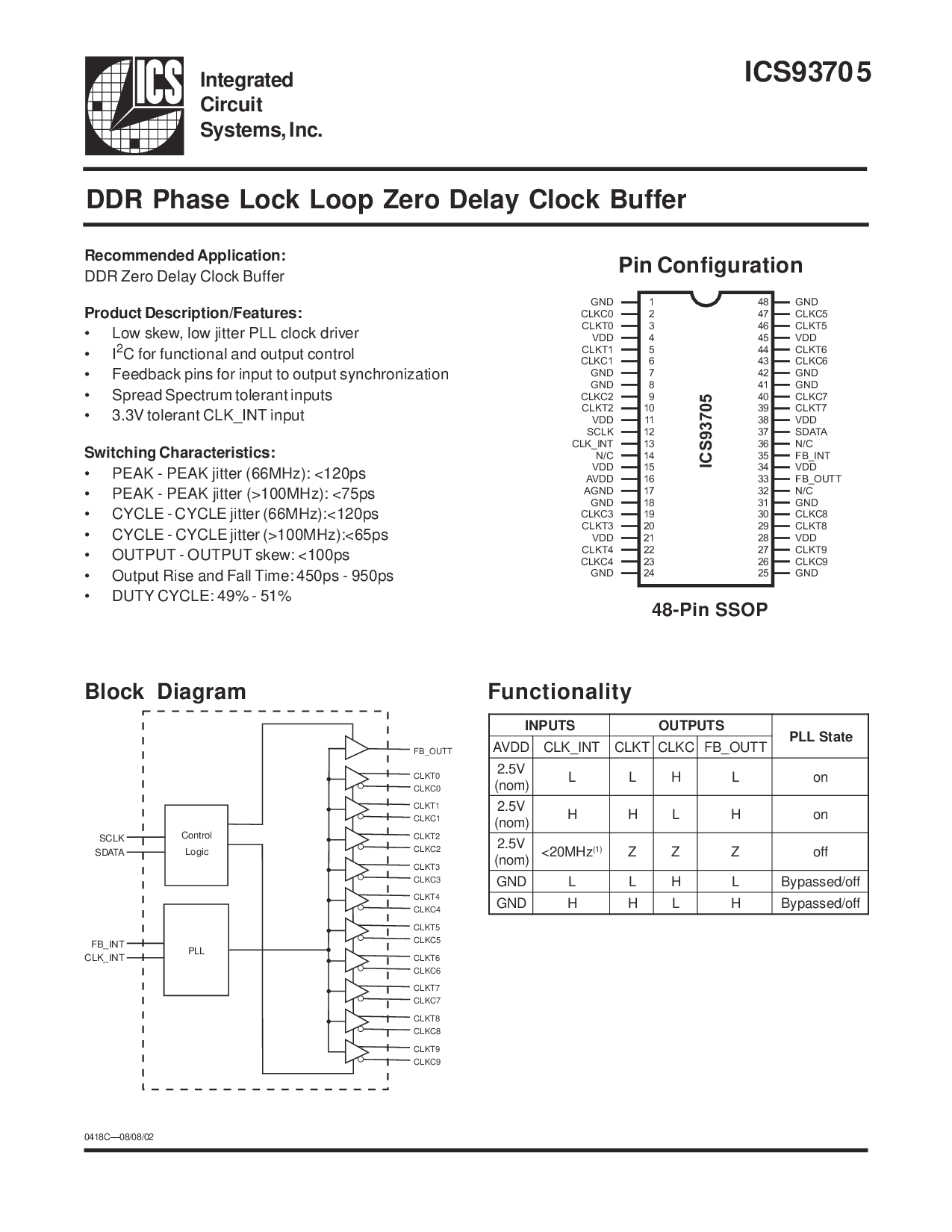

管脚 配置

48-管脚 ssop

推荐 应用:

ddr 零 延迟 时钟 缓存区

产品 描述/特性:

• 低 skew, 低 jitter pll 时钟 驱动器

•I

2

c 为 函数的 和 输出 控制

• 反馈 管脚 为 输入 至 输出 同步

• 展开 spectrum tolerant 输入

• 3.3v tolerant clk_int 输入

切换 特性:

• 顶峰 - 顶峰 jitter (66mhz): <120ps

• 顶峰 - 顶峰 jitter (>100mhz): <75ps

• 循环 - 循环 jitter (66mhz):<120ps

• 循环 - 循环 jitter (>100mhz):<65ps

• 输出 - 输出 skew: <100ps

• 输出 上升 和 下降 时间: 450ps - 950ps

• 职责 循环: 49% - 51%

地

CLKC0

CLKT0

VDD

CLKT1

CLKC1

地

地

CLKC2

CLKT2

VDD

SCLK

clk_int

n/c

AVDD

AGND

地

CLKC3

CLKT3

VDD

CLKT4

CLKC4

地

VDD

地

CLKC5

CLKT5

VDD

CLKT6

CLKC6

地

地

CLKC7

CLKT7

VDD

SDATA

n/c

VDD

fb_outt

n/c

地

CLKC8

CLKT8

VDD

CLKT9

CLKC9

地

fb_int

ICS93705

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

符合实际

fb_int

clk_int

PLL

SCLK

S 数据

控制

逻辑

fb_outt

CLKT0

CLKT1

CLKT2

CLKT3

CLKT4

CLKT5

CLKT6

CLKT7

CLKT8

CLKT9

CLKC0

CLKC1

CLKC2

CLKC3

CLKC4

CLKC5

CLKC6

CLKC7

CLKC8

CLKC9

STUPN是TUPTUO

etatSLLP

DDV在ni_klCTKLCCKLCTtuo_bf

v5.2

)mon(

LLHL no

v5.2

)mon(

HHLH no

v5.2

)mon(

zhm02<

)1(

ZZ Z ffo

DNGLLHL

ffo/dessapyb

DNGHHLH

ffo/dessapyb