修订 3.01/october 2003 © semtech corp. 页 1 www.semtech.com

acs8520 sets

先进的 communications 最终

同步的 equipmenttiming 源 为

Stratum 3/4e/4 和 smc 系统

先进的 communications 最终 数据手册

这 acs8520 是 一个 高级地 integrated, 单独的-碎片 解决方案

为 这 同步的 设备 定时 源 (sets)

函数 在 一个 sonet 或者 sdh 网络 元素. 这 设备

发生 sonet 或者 sdh 设备 clocks (秒) 和

框架 同步 clocks. 这 acs8520 是 全部地

一致的 和 这 必需的 国际的 规格

和 standards.

这 设备 支持 自由-run, 锁 和 holdover

模式. 它 也 支持 所有 三 类型 的 涉及 时钟

源: recovered 线条 时钟, pdh 网络, 和 node

同步. 这 acs8520 发生 独立

秒 和 位/ssu clocks, 一个 8 khz 框架

同步 时钟 和 一个 2 khz multi-框架

同步 时钟.

二 acs8520 设备 能 是 使用 一起 在 一个 主控/

从动装置 配置 模式 准许 系统 保护

相反 一个 单独的 acs8520 失败.

一个 微处理器 端口 是 组成公司的, 供应 进入 至

这 配置 和 状态 寄存器 为 设备 建制

和 monitoring. 这 acs8520 支持 ieee 1149.1

[5]

jtag boundary scan.

这 用户 能 choose 在 ocxo 或者 tcxo 至 定义 这

stratum 和/或者 holdover 效能 必需的.

合适的 为 stratum 3, 4e, 4 和 sonet 最小

时钟 (smc) 或者 sonet/sdh 设备 时钟 (秒)

产品

满足 telcordia 1244-核心

[19]

stratum 3 和

gr-253

[17]

, 和 itu-t g.813

[11]

选项

Ι

和

ΙΙ

规格

accepts 14 单独的 输入 涉及 clocks, 所有 和

强健的 输入 时钟 源 质量 monitoring.

同时发生地 发生 nine 输出 clocks, 加

二 同步 脉冲波 输出

绝对 holdover 精度 更好的 比 3 x 10

-10

(手工的), 7.5 x 10

-14

(instantaneous); holdover

稳固 定义 用 选择 的 外部 xo

可编程序的 pll 带宽, 为 wander 和 jitter

追踪/attenuation, 0.1 hz 至 70 hz 在 10 步伐

自动 hit-较少 源 switchover 在 丧失 的 输入

微处理器 接口 - intel, motorola, 串行,

多路复用, 或者 激励 从 非易失存储器

输出 阶段 调整 在 6 ps 步伐 向上 至 ±200 ns

ieee 1149.1 jtag boundary scan

单独的 3.3 v 运作. 5 v tolerant

有 在 lqfp 100 包装

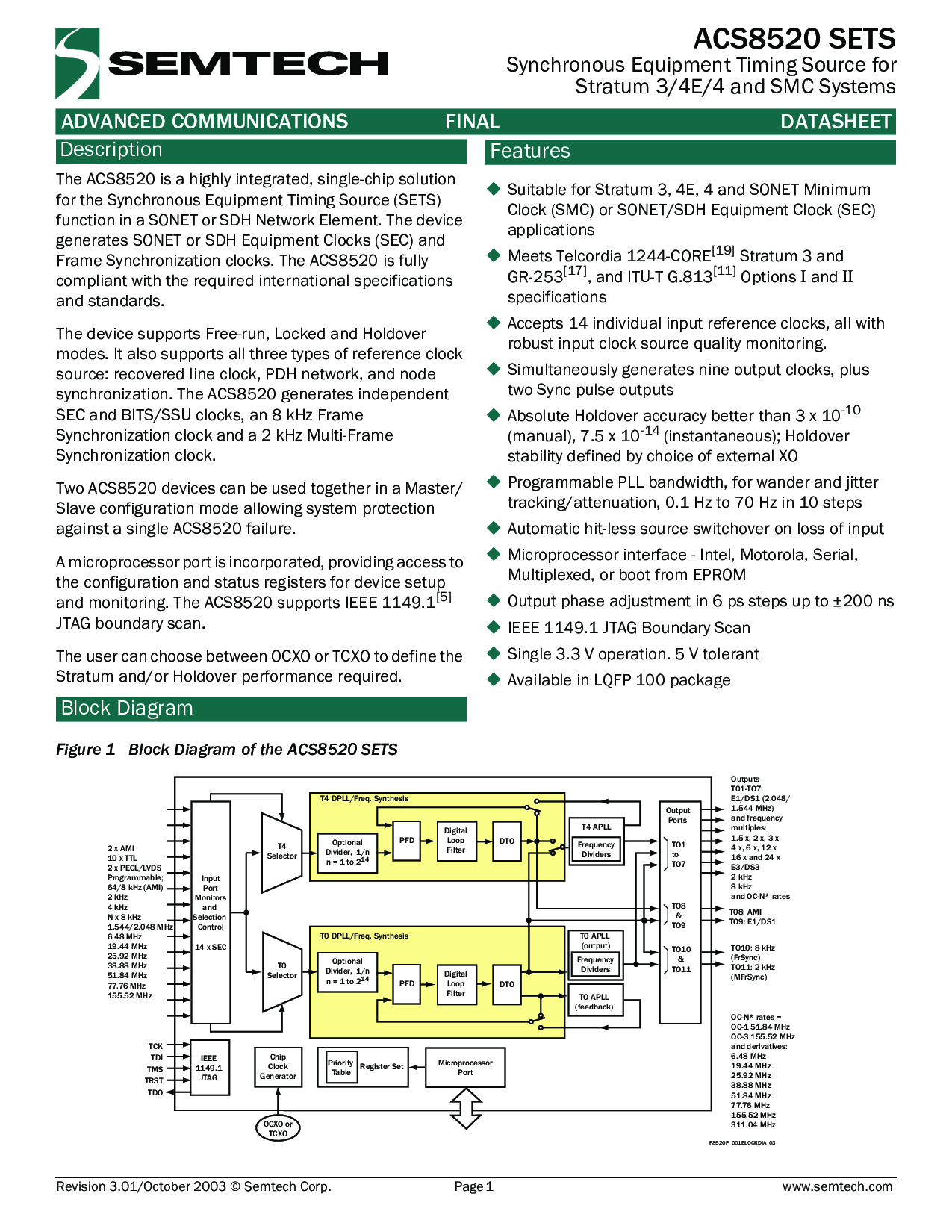

图示 1 块 图解 的 这 acs8520 sets

块 图解

描述

特性

IEEE

1149.1

JTAG

输入

端口

Monitors

和

选择

控制

14 x 秒

Optional

分隔物, 1/n

n = 1 至 2

14

Optional

分隔物, 1/n

n = 1 至 2

14

PFD

数字的

循环

过滤

碎片

时钟

发生器

DTO

TCK

TDI

TMS

TRST

TDO

f8520p_001blockdia_03

T4

选择

T0

选择

PFD

数字的

循环

过滤

DTO

t4 apll

频率

Dividers

t0 apll

(输出)

频率

Dividers

至 apll

(反馈)

TO8

&放大;

TO9

TO10

&放大;

TO11

TO1

至

TO7

输出

t01-to7:

e1/ds1 (2.048/

1.544 mhz)

和 频率

multiples:

1.5 x, 2 x, 3 x

4 x, 6 x, 12 x

16 x 和 24 x

e3/ds3

2 khz

8 khz

和 oc-n* 比率

oc-n* 比率 =

oc-1 51.84 mhz

oc-3 155.52 mhz

和 derivatives:

6.48 mhz

19.44 mhz

25.92 mhz

38.88 mhz

51.84 mhz

77.76 mhz

155.52 mhz

311.04 mhz

t08: ami

to9: e1/ds1

2 x ami

10 x ttl

2 x pecl/lvds

可编程序的;

64/8 khz (ami)

2 khz

4 khz

n x 8 khz

1.544/2.048 mhz

6.48 mhz

19.44 mhz

25.92 mhz

38.88 mhz

51.84 mhz

77.76 mhz

155.52 mhz

to10: 8 khz

(frsync)

to11: 2 khz

(mfrsync)

输出

端口

Priority

表格

寄存器 设置

微处理器

端口

ocxo 或者

TCXO

t4 dpll/freq. 综合

t0 dpll/freq. 综合