pll500-17

低 阶段 噪音 vcxo (17mhz 至 36mhz)

47745 fremont blvd., fremont, 加利福尼亚 94538 电话 (510) 492-0990 传真 (510) 492-0991

www.phaselink.com

rev 03/29/05 页 1

特性

•

vcxo 输出 为 这 17mhz 至 36mhz 范围

•

低 阶段 噪音 (-130 dbc @ 10khz 补偿 在

35.328mhz).

•

cmos 输出 和 oe 触发-状态 控制.

•

17 至 36mhz fundamental 结晶 输入.

•

整体的 高 线性 能变的 电容.

•

12ma 驱动 能力 在 ttl 输出.

•

+/- 150 ppm 拉 范围, 最大值 5% 线性.

•

低 jitter (rms): 2.5ps 时期 jitter.

•

2.5 至 3.3v 运作.

•

有 在 8-管脚 soic, 6-管脚 sot23 包装,

或者 消逝.

描述

这 pll500-17 是 一个 低 费用, 高 效能 和

低 阶段 噪音 vcxo 为 这 17 至 36mhz 范围,

供应 较少 比 -130dbc 在 10khz 补偿 在

35.328mhz. 这 非常 低 jitter (2.5 ps rms 时期

jitter) 制造 这个 碎片 完美的 为 产品 需要

电压 控制 频率来源. 输入 结晶

能 范围 从 17 至 36mhz (基本的 resonant

模式).

频率 范围

乘法器 频率

输出

缓存区

非 pll 17 – 36 mhz CMOS

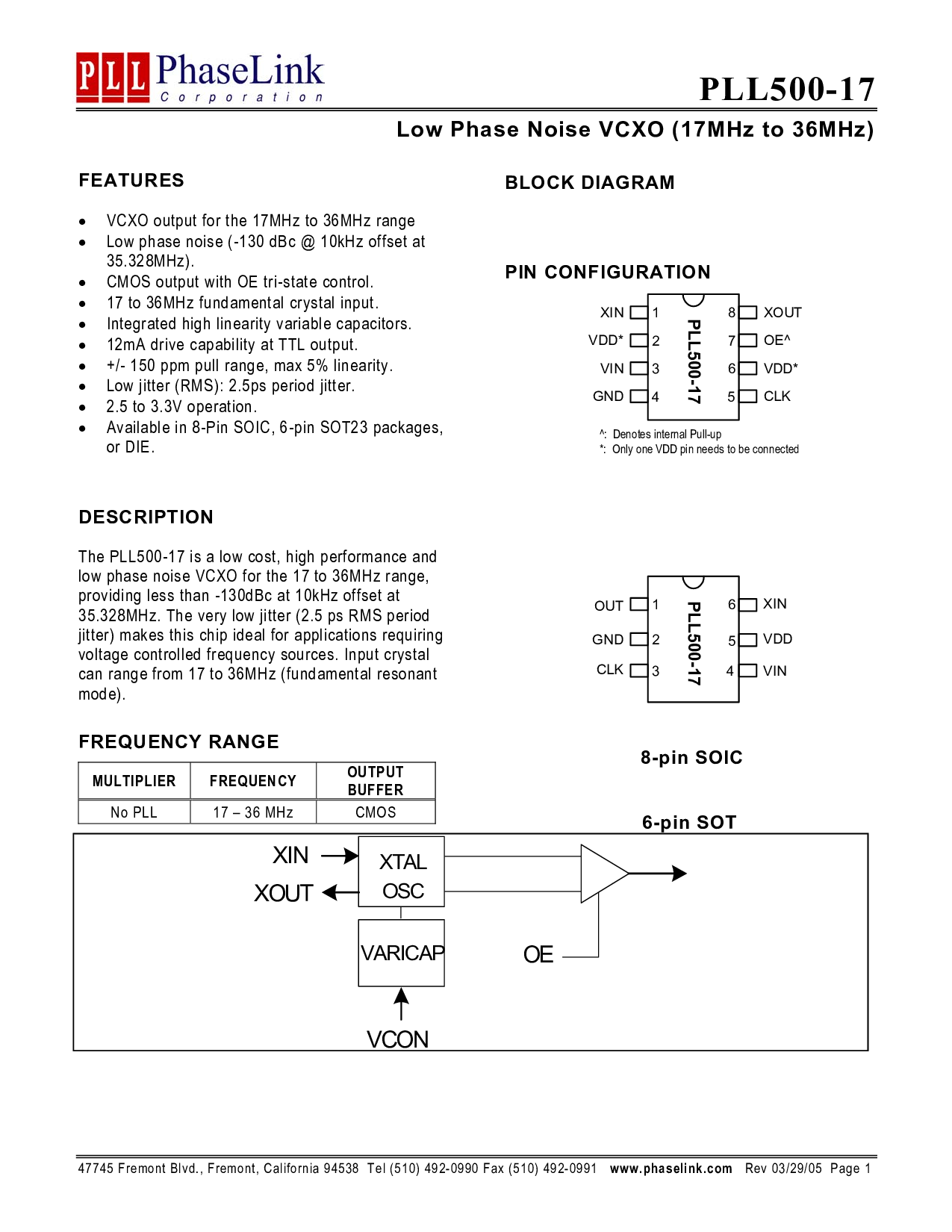

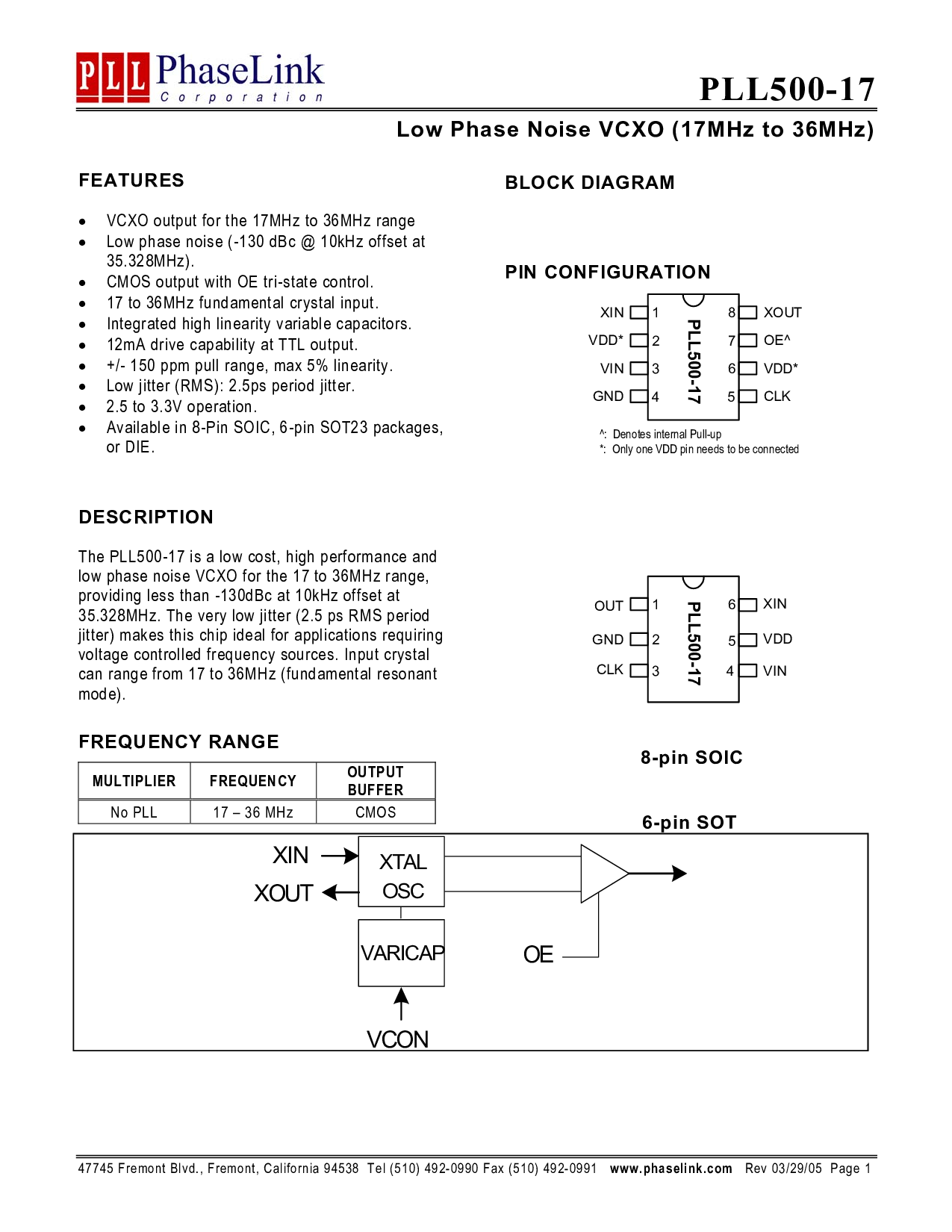

块 图解

管脚 配置

8-管脚 soic

6-管脚 sot

XTAL

OSC

OE

XIN

XOUT

VCON

VARICAP

pll500-17

1

2

3

45

6

7

8

XIN

VDD*

VIN

地

XOUT

VDD*

CLK

OE^

^: denotes 内部的 拉-向上

*: 仅有的 一个 vdd 管脚 needs 至 是 连接

pll500-17

1

2

3

5

6

输出

地

CLK

XIN

VDD

VIN

4