4-mbit (128k x 36) pipelined 同步 sram

CY7C1347F

Cypress 半导体 公司

• 3901 北 第一 街道 • San Jose

,

ca 95134 • 408-943-2600

文档 #: 38-05213 rev. *d 修订 april 9, 2004

特性

• 全部地 注册 输入 和 输出 为 pipelined oper-

ation

• 128k 用 36 一般 i/o architecture

• 3.3v 核心 电源 供应

• 2.5v/3.3v i/o 运作

• 快 时钟-至-输出 时间

— 2.6 ns (为 250-mhz 设备)

— 2.6 ns (为 225-mhz 设备)

— 2.8 ns (为 200-mhz 设备)

— 3.5 ns (为 166-mhz 设备)

— 4.0 ns (为 133-mhz 设备)

• 用户-可选择的 burst 计数器 支承的 intel

Pentium

interleaved 或者 直线的 burst sequences

• 独立的 处理器 和 控制 地址 strobes

• 同步的 自-安排时间 写

• 异步的 输出 使能

• 电子元件工业联合会-标准 100-管脚 tqfp, 119-管脚 bga 和

165-管脚 fbga 包装

• “zz” 睡眠 模式 选项 和 停止 时钟 选项

• 有 在 工业的 和 商业的 温度

范围

函数的 描述

[1]

这 cy7c1347f 是 一个 3.3v, 128k 用 36 同步的-pipelined

sram 设计 至 支持 零-wait-状态 secondary cache

和 minimal glue 逻辑.

cy7c1347f i/o 管脚 能 运作 在 也 这 2.5v 或者 这 3.3v

水平的, 这 i/o 管脚 是 3.3v tolerant 当 v

DDQ

= 2.5v.

所有 同步的 输入 通过 通过 输入 寄存器 控制

用 这 rising 边缘 的 这 时钟. 所有 数据 输出 通过 通过

输出 寄存器 控制 用这 rising 边缘 的 这 时钟.

最大 进入 延迟 从 这 时钟 上升 是 2.6 ns (250-mhz

设备)

cy7c1347f 支持 也 the interleaved burst sequence

使用 用 这 intel pentium processor 或者 一个 直线的 burst sequence

使用 用 processors 此类 作 这 powerpc

®

. 这 burst

sequence 是 选择 通过 这 模式 管脚. accesses 能 是

initiated 用 asserting 也 这 地址 strobe 从

处理器 (adsp

) 或者 这 地址 strobe 从 控制

(adsc

) 在 时钟 上升. 地址 advancement 通过 这 burst

sequence 是 控制 用 这 adv

输入. 一个 2-位 在-碎片

wraparound burst 计数器 俘获 这 第一 地址 在 一个 burst

sequence 和 automatically increments 这 地址 为 这

rest 的 这 burst 进入.

字节 写 行动 是 qualified 和 这 四 字节 写

选择 (bw

[a:d]

) 输入. 一个 global 写 使能 (gw) overrides

所有 字节 写 输入 和 写 数据 至 所有 四 字节. 所有 写

是 安排 和 在-碎片 synchronous 自-安排时间 写

电路系统.

三 同步的 chip 选择 (ce

1

, ce

2

, ce

3

) 和 一个

异步的 输出 使能 (oe

) 提供 为 容易 bank

选择 和 输出 三-状态 控制. 在 顺序 至 提供

恰当的 数据 在 depth expansion, oe 是 masked 在 这

第一 时钟 的 一个 读 循环 当 emerging 从 一个 deselected

状态.

便条:

1. 为 最好的-practices recommendations, 请 谈及 至 这 cypress 应用 便条

系统 设计 指导原则

在 www.cypress.com.

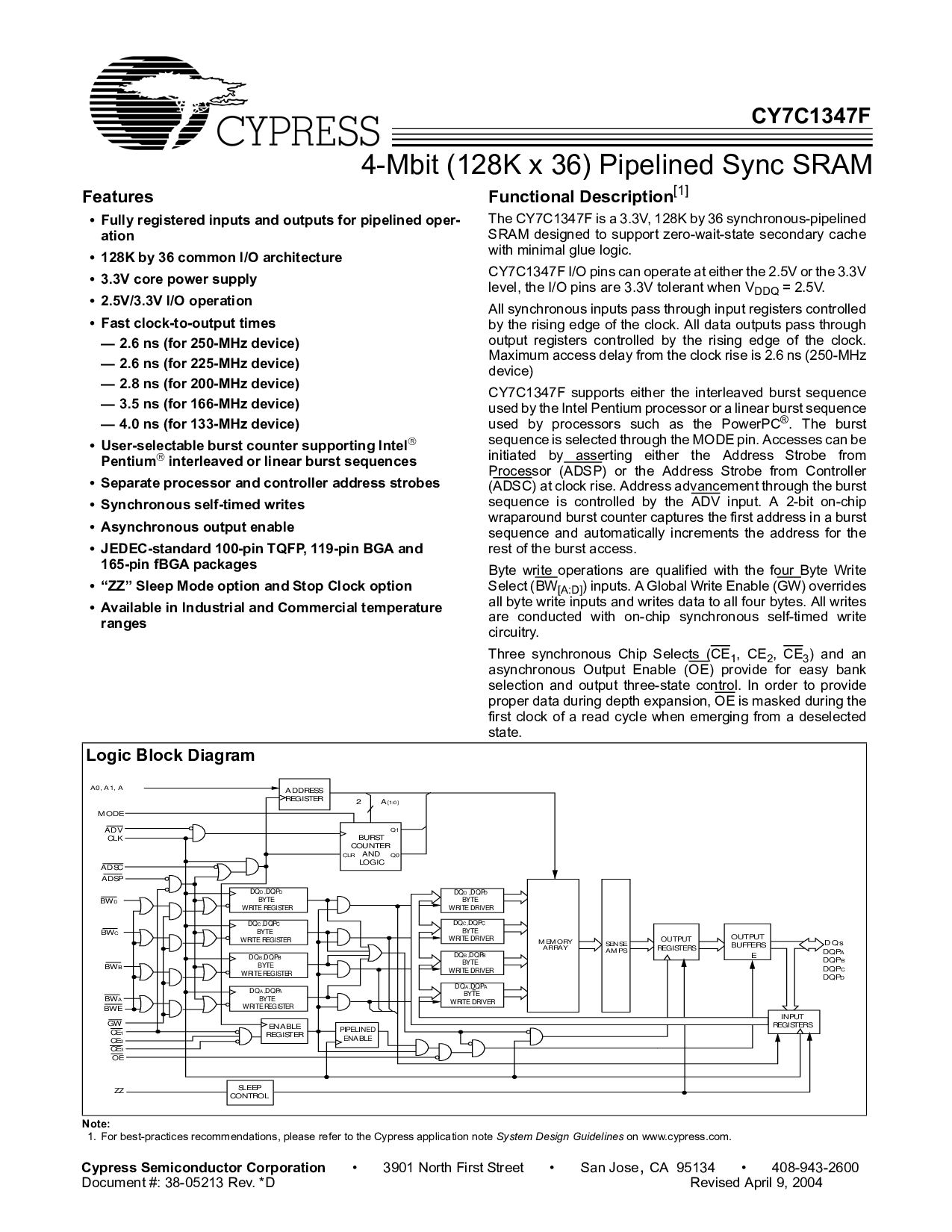

逻辑 块 图解

地址

寄存器

ADV

CLK

BURST

计数器

和

逻辑

CLR

Q1

Q0

ADSP

ADSC

模式

BWE

GW

CE

1

CE

2

CE

3

OE

使能

寄存器

输出

寄存器

SENSE

放大器

输出

缓存区

E

PIPELINED

使能

输入

寄存器

a0, a1, 一个

BW

B

BW

C

BW

D

BW

一个

记忆

排列

DQs

DQP

一个

DQP

B

DQP

C

DQP

D

睡眠

控制

ZZ

一个

[1:0]

2

DQ

一个 ,

DQP

一个

字节

写 寄存器

DQ

b ,

DQP

B

字节

写 寄存器

DQ

c ,

DQP

C

字节

写 寄存器

DQ

d ,

DQP

D

字节

写 寄存器

DQ

一个 ,

DQP

一个

字节

写 驱动器

DQ

b ,

DQP

B

字节

写 驱动器

DQ

c ,

DQP

C

字节

写 驱动器

DQ

D

,dqp

D

字节

写 驱动器