GAL20RA10

高-速 异步的 e

2

cmos pld

generic 排列 logic™

1

1

12

13

24

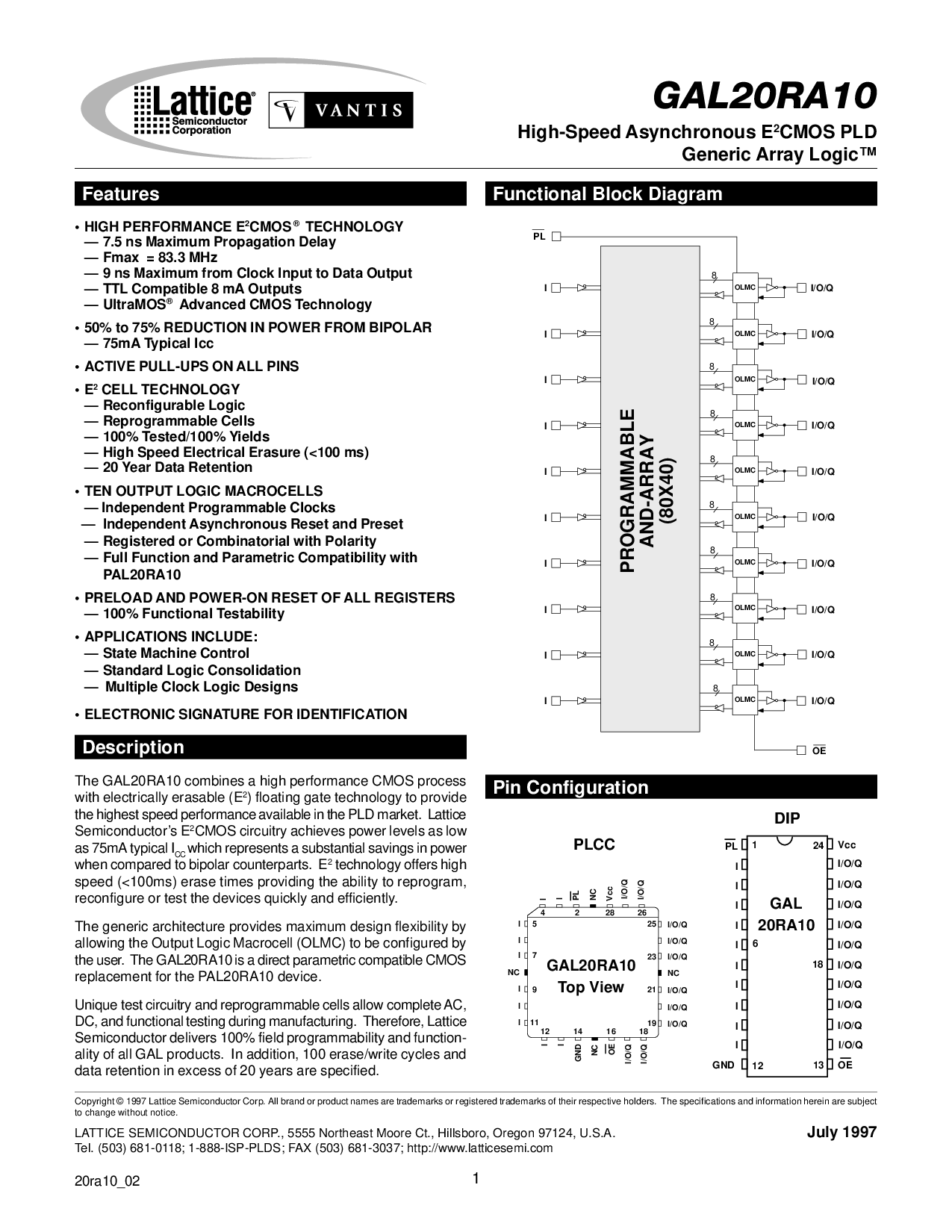

PL

I

I

I

I

I

I

I

I

I

I

地

Vcc

i/o/q

i/o/q

i/o/q

i/o/q

i/o/q

i/o/q

i/o/q

i/o/q

i/o/q

i/o/q

OE

6

18

插件

PLCC

228

NC

PL

I

I

I

I

I

I

I

I

NC

NC

NC

地

I

I

OE

i/o/q

i/o/q

i/o/q

i/o/q

i/o/q

i/o/q

i/o/q

Vcc

i/o/q

i/o/q

i/o/q

4

7

5

9

11

12 14 16 18

19

21

23

25

26

GAL

20RA10

特性

•

高 效能 e

2

CMOS

®

技术

—

7.5 ns 最大 传播 延迟

—

fmax = 83.3 mhz

—

9 ns 最大 从 时钟 输入 至 数据 输出

—

ttl 兼容 8 毫安 输出

—

UltraMOS

®

先进的 cmos 技术

•

50% 至 75% 减少 在 电源 从 双极

—

75ma 典型 icc

•

起作用的 拉-ups 在 所有 管脚

•

E

2

cell 技术

—

reconfigurable 逻辑

—

reprogrammable cells

—

100% 测试/100% 产量

—

高 速 电的 erasure (<100 ms)

—

20 年 数据 保持

•

ten 输出 逻辑 macrocells

—

独立 可编程序的 clocks

—

独立 异步的 重置 和 preset

—

注册 或者 combinatorial 和 极性

—

全部 函数 和 参数 兼容性 和

PAL20RA10

•

preload 和 电源-在 重置 的 所有 寄存器

—

100% 函数的 testability

•

产品 包含:

—

状态 机器 控制

—

标准 逻辑 consolidation

—

多样的 时钟 逻辑 设计

•

电子的 signature 为 identification

GAL20RA10

顶 视图

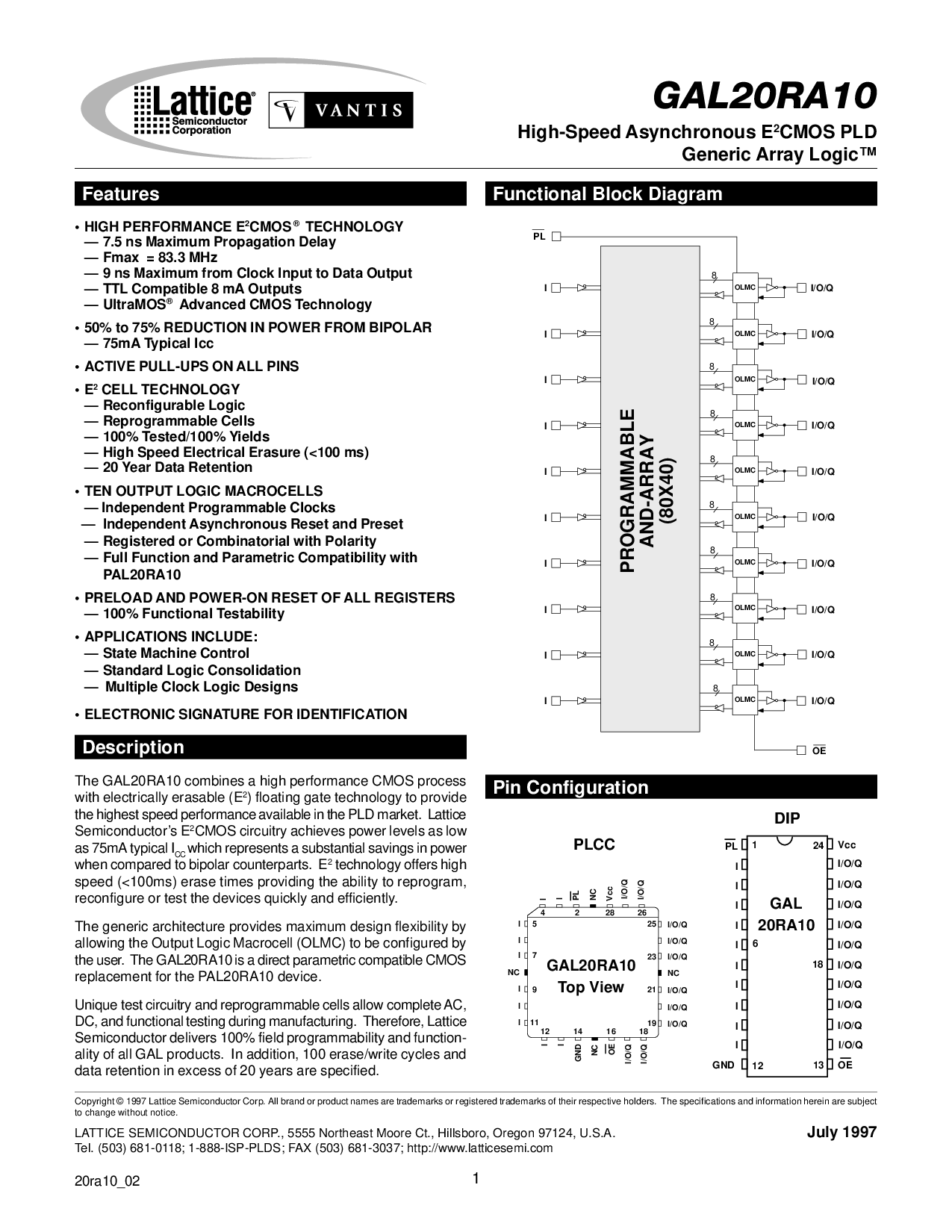

可编程序的

和-排列

(80x40)

OE

PL

I

i/o/q

8

OLMC

i/o/q

8

OLMC

i/o/q

8

OLMC

i/o/q

8

OLMC

i/o/q

8

OLMC

i/o/q

8

OLMC

i/o/q

8

OLMC

i/o/q

8

OLMC

i/o/q

8

OLMC

i/o/q

8

OLMC

I

I

I

I

I

I

I

I

I

版权 © 1997 lattice 半导体 corp. 所有 brand 或者 产品 names 是 商标 或者 注册 商标 的 它们的 各自的 holders. 这 规格 和 信息 在此处 是 主题

至 改变 没有 注意.

lattice 半导体 corp., 5555 northeast moore ct., hillsboro, oregon 97124, 美国

july 1997

电话. (503) 681-0118; 1-888-isp-plds; 传真 (503) 681-3037; http://www.latticesemi.com

20ra10_02

描述

这 gal20ra10 结合 一个 高 效能 cmos 处理

和 用电气 可擦掉的 (e

2

) floating 门 技术 至 提供

这 最高的 速 效能 有 在 这 pld market. lattice

半导体’s e

2

cmos 电路系统 achieves 电源 水平 作 低

作 75ma 典型 i

CC

这个 代表 一个 substantial savings 在 电源

当 对照的 至 双极 counterparts. e

2

技术 提供 高

速 (<100ms) 擦掉 时间 供应 这 能力 至 reprogram,

reconfigure 或者 测试 这 设备 quickly 和 efficiently.

这 generic architecture 提供 最大 设计 flexibility 用

准许 这 输出 逻辑 macrocell (olmc) 至 是 配置 用

这 用户. 这 gal20ra10 是 一个 直接 参数 兼容 cmos

替换 为 这 pal20ra10 设备.

唯一的 测试 电路系统 和 reprogrammable cells 准许 完全 交流,

直流, 和 函数的 测试 在 制造. 因此, lattice

半导体 delivers 100% 地方 programmability 和 函数-

ality 的 所有 gal 产品. 在 增加, 100 擦掉/写 循环 和

数据 保持 在 excess 的 20 年 是 指定.

函数的 块 图解

管脚 配置