半导体 组件 industries, llc, 2000

将, 2000 – rev. 1

1

发行 顺序 号码:

mc100lvep14/d

MC100LVEP14

低-电压 1:5 差别的

lvecl/lvpecl/lvepecl/hstl

时钟 驱动器

这 mc100lvep14 是 一个 低 skew 1–to–5 差别的 驱动器, 设计

和 时钟 分发 在 mind, accepting 二 时钟 来源 在 一个 输入

多路调制器. 这 lvecl/lvpecl 输入 信号 能 是 也 差别的

或者 single–ended (如果 这 v

BB

输出 是 使用). hstl 输入 能 是 使用

当 这 lvep14 是 运行 下面 lvpecl 情况.

这 lvep14 specifically guarantees 低 output–to–output skew.

最优的 设计, 布局, 和 处理 降低 skew 在里面 一个 设备 和

从 lot 至 lot.

至 确保 那 这 tight skew 规格 是 认识到, 两个都 sides 的

任何 差别的 输出 需要 至 是 terminated 相(恒)等 在 50

W

甚至

如果 仅有的 一个 一侧 是 正在 使用. 当 更少的 比 所有 five pairs 是 使用,

相(恒)等 terminate 所有 这 输出 pairs 在 这 一样 包装 一侧

whether 使用 或者 unused. 如果 非 输出 在 一个 单独的 一侧 是 使用, 然后

leave 这些 输出 打开 (unterminated). 这个 将 维持 最小

输出 skew. 失败 至 做 这个 将 结果 在 一个 10–20ps 丧失 的 skew

余裕 (传播 延迟) 在 这 输出(s) 在 使用.

这 一般 使能 (en

) 是 同步的, 输出 是 使能/

无能 在 这 低 状态. 这个 避免 一个 runt 时钟 脉冲波 当 这

设备 是 使能/无能 作 能 发生 和 一个 异步的

控制. 这 内部的 flip flop 是 clocked 在 这 下落 边缘 的 这 输入

时钟, 因此 所有 有关联的 规格 限制 是 关联 至 这

负的 边缘 的 这 时钟 输入.

这 mc100lvep14, 作 和 大多数 其它 lvecl 设备, 能 是

运作 从 一个 积极的 v

CC

供应 在 lvpecl 模式. 这个 准许

这 lvep14 至 是 使用 为 高 效能 时钟 分发 在

+3.3v 或者 +2.5v 系统. 单独的 结束 输入 运作 是 限制 至 一个

V

CC

≥

3.0v 在 lvpecl 模式, 或者 v

EE

≤

–3.0v 在 lvecl 模式.

designers 能 引领 有利因素 的 这 lvep14’s 效能 至

distribute 低 skew clocks 横过 这 backplane 或者 这 板. 为 更多

信息, 谈及 至 应用 便条 an1406/d.

•

100ps part–to–part skew

•

25ps output–to–output skew

•

差别的 设计

•

400ps 典型 传播 延迟

•

高 带宽 至 1.5 ghz 典型

•

lvpecl 和 hstl 模式: +2.375v 至 +3.8v v

CC

和 v

EE

= 0v

•

lvecl 模式: 0v v

CC

和 v

EE

= –2.375v 至 –3.8v

•

75k

Ω

内部的 pulldown clks, 拉 向上 &放大; pulldown clks

•

静电释放 保护: >2kv hbm; >100v mm

•

潮气 敏锐的 水平的 2

为 额外的 信息, 看 应用 便条 and8003/d

•

flammability 比率: ul–94 代号 v–0 @ 1/8”, oxygen index 28 至 34

•

晶体管 计数 = 357 设备

http://onsemi.com

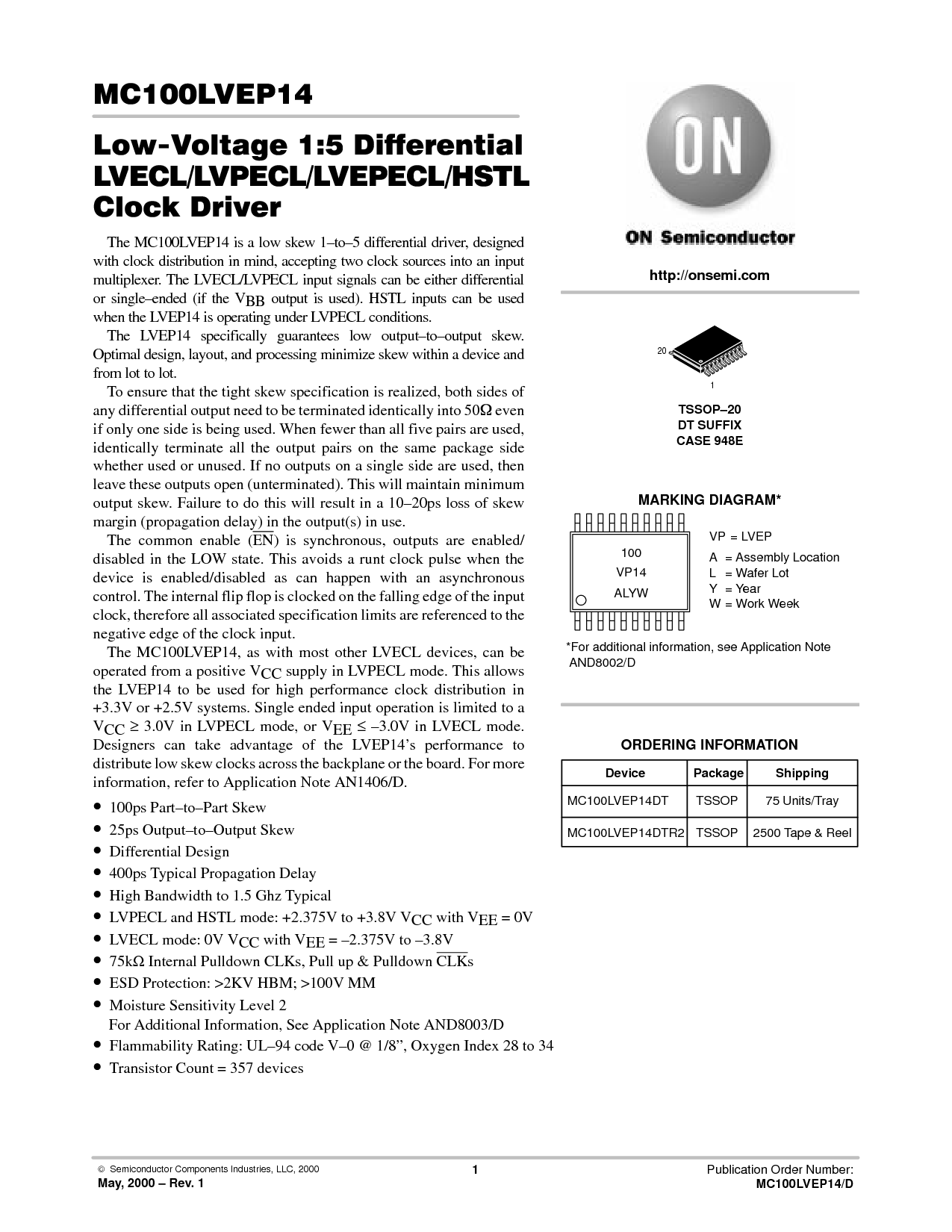

设备 包装 Shipping

订货 信息

MC100LVEP14DT TSSOP 75 单位/tray

MC100LVEP14DTR2 TSSOP 2500 录音带 &放大; 卷轴

TSSOP–20

dt 后缀

情况 948e

标记 diagram*

一个 = 组装 location

L = 薄脆饼 lot

Y = 年

W = 工作 week

*for 额外的 信息, 看 应用 便条

and8002/d

100

VP14

ALYW

20

1

VP = lvep