半导体 组件 industries, llc, 2005

二月, 2005 − rev. 12

1

发行 顺序 号码:

mc100lvelt23/d

MC100LVELT23

3.3 vdual 差别的

lvpecl/lvds 至 lvttl

翻译

这 mc100lvelt23 是 一个 双 差别的 lvpecl/lvds 至

lvttl 翻译. 因为 lvpecl (积极的 ecl) 或者 lvds 水平

是 使用 仅有的 +3.3 v 和 地面 是 必需的. 这 小 外形 8-含铅的

包装 和 这 双 门 设计 的 这 lvelt23 制造 它 完美的 为

产品 这个 需要 这 转变 的 一个 时钟 和 一个 数据 信号.

这 lvelt23 是 有 在 仅有的 这 ecl 100k 标准. 自从

那里 是 非 lvpecl 输出 或者 一个 外部 v

BB

涉及, 这

lvelt23 做 不 需要 两个都 ecl 标准 版本. 这 lvpecl

输入是 差别的. 因此, 这 mc100lvelt23 能 接受 任何

标准 差别的 lvpecl 输入 关联 从 一个 v

CC

的 +3.3 v.

•

2.0 ns 典型 传播 延迟

•

最大 频率 > 180 mhz

•

差别的 lvpecl 输入

•

pecl 模式 运行 范围:v

CC

= 3.0 v 至 3.8 v

和 地 = 0 v

•

24 毫安 lvttl 输出

•

流动 通过 pinouts

•

内部的 pulldown 和 pullup 电阻器

•

pb−free 包装 是 有

*for 额外的 标记 信息, 谈及 至

应用 便条 and8002/d.

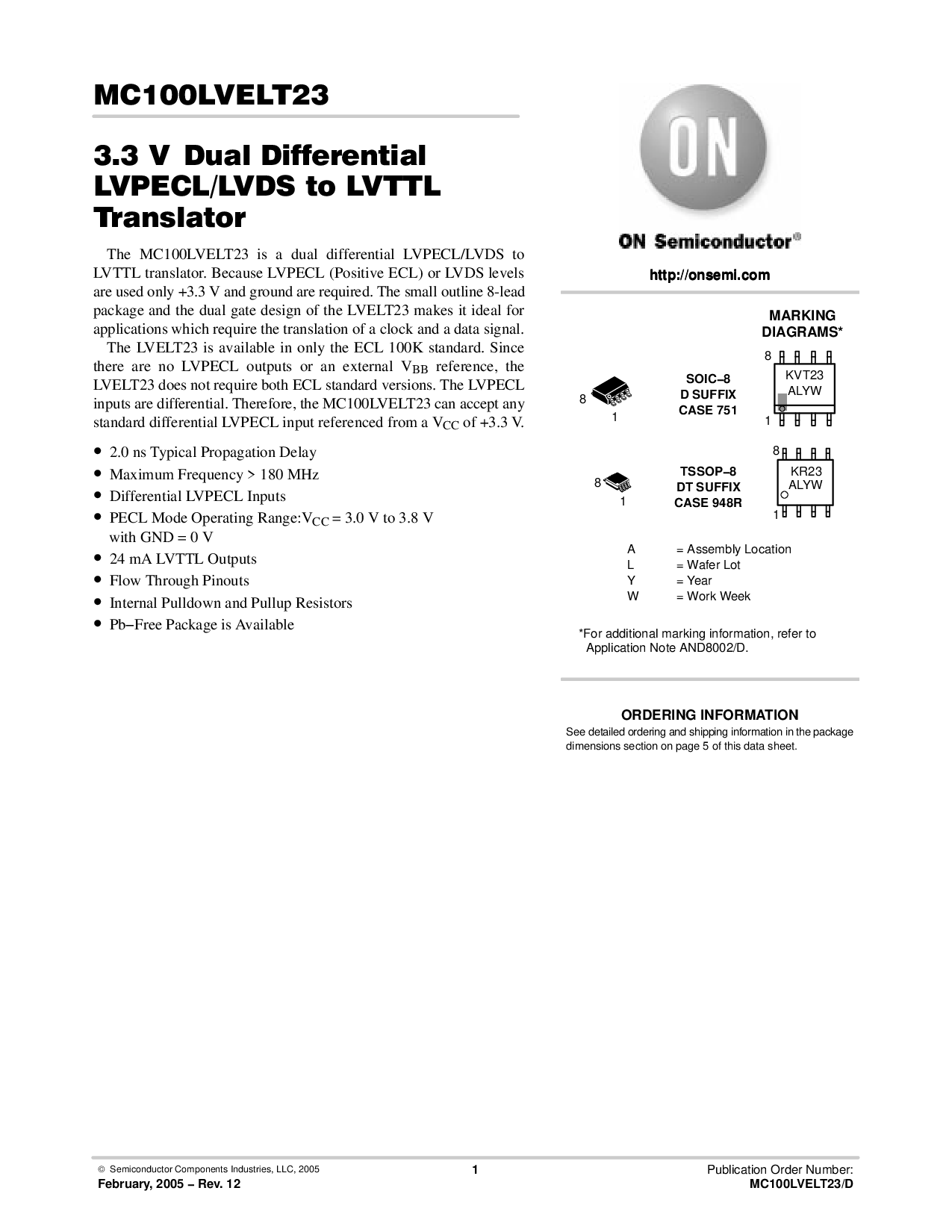

SOIC−8

d 后缀

情况 751

标记

DIAGRAMS*

TSSOP−8

dt 后缀

情况 948r

一个 = 组装 location

L = 薄脆饼 lot

Y = 年

W = 工作 week

1

8

1

8

ALYW

KR23

1

8

http://onsemi.com

看 详细地 订货 和 shipping 信息 在 这 包装

维度 部分 在 页 5 的 这个 数据 薄板.

订货 信息

http://onsemi.com

KVT23

ALYW

1

8