摩托罗拉

半导体 技术类 数据

1

rev 0

摩托罗拉, 公司 1997

6/97

八进制 总线 缓冲区

反转

这 mc74vhc540 是 一个 高级 高 速度 cmos 反转 八进制 总线

缓冲区 预制 与 硅 闸门 cmos 技术. 它 达到 高 速度

操作 类似 至 等效 双极性 肖特基 ttl 同时 维护

cmos 低 电源 耗散.

这 mc74vhc540 特点 输入 和 产出 开启 对面 侧面 的 这

包装 和 两个 and–ed 低电平有效 输出 启用. 当 要么 oe1

或

OE2

是 高, 这 终端 产出 是 入点 这 高 阻抗 州.

这 内部 电路 是 组成 的 三个 阶段, 包括 一个 缓冲区 输出

哪个 提供 高 噪声 免疫 和 稳定 输出. 这 输入 容忍

电压 向上 至 7v, 允许 这 接口 的 5v 系统 至 3v 系统.

•

高 速度: t

pd

= 3.7ns (典型值) 在 v

抄送

= 5v

•

低 电源 耗散: 我

抄送

= 4

µ

一个 (最大值) 在 t

一个

= 25

°

c

•

高 噪声 免疫: v

NIH

= v

NIL

= 28% v

抄送

•

电源 向下 保护 提供 开启 输入

•

平衡式 传播 延误

•

设计 用于 2v 至 5.5v 操作 范围

•

低 噪声: v

olp

= 1.2v (最大值)

•

管脚 和 功能 兼容 与 其他 标准 逻辑 家庭

•

latchup 业绩 超过 300ma

•

esd 业绩: hbm > 2000v; 机器 型号 > 200v

•

芯片 复杂性: 124 fets 或 31 等效 盖茨

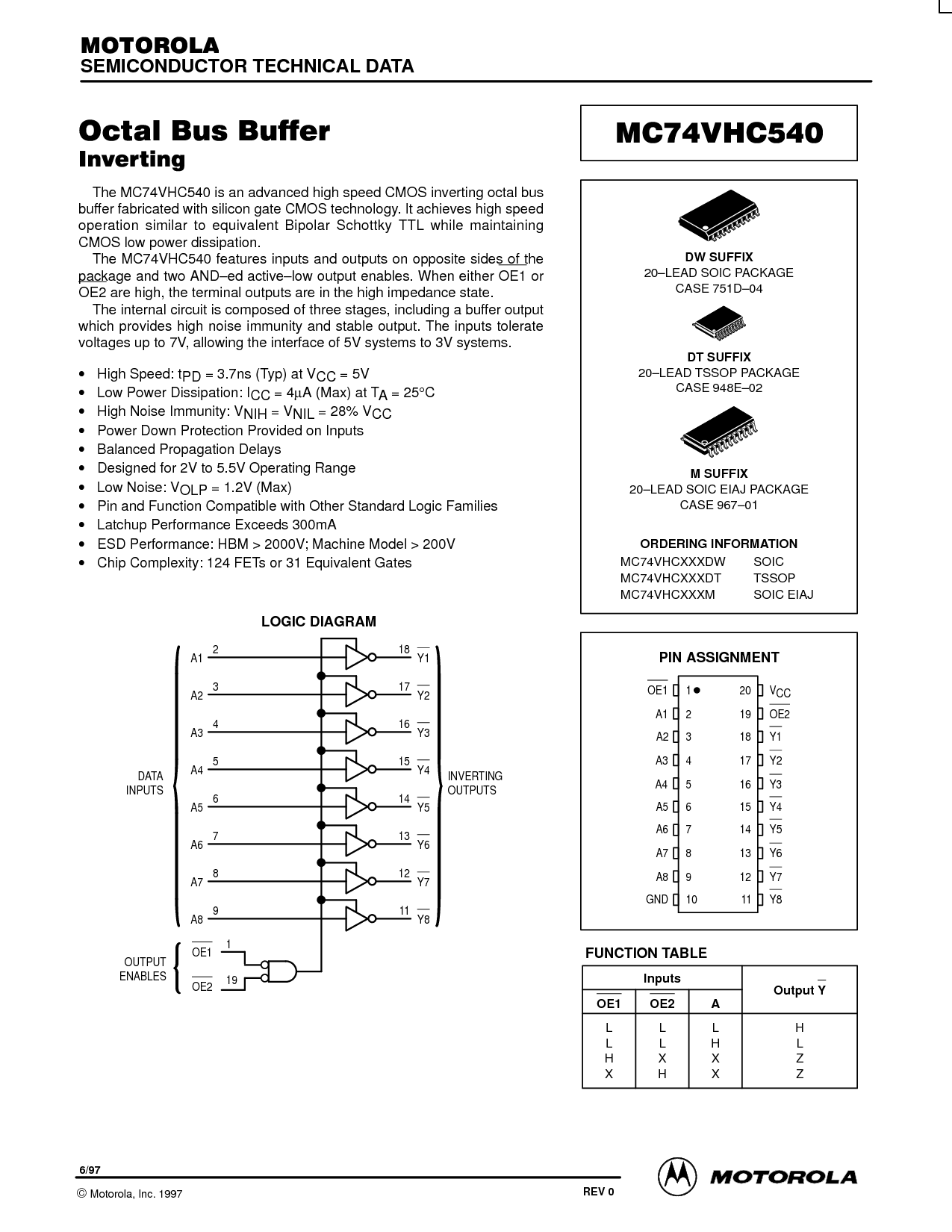

18

Y1

2

A1

17

Y2

3

A2

16

Y3

4

A3

15

Y4

5

A4

14

Y5

6

A5

13

Y6

7

A6

12

Y7

8

A7

11

Y8

9

A8

OE1

OE2

1

19

输出

启用

数据

输入

反转

产出

逻辑 图表

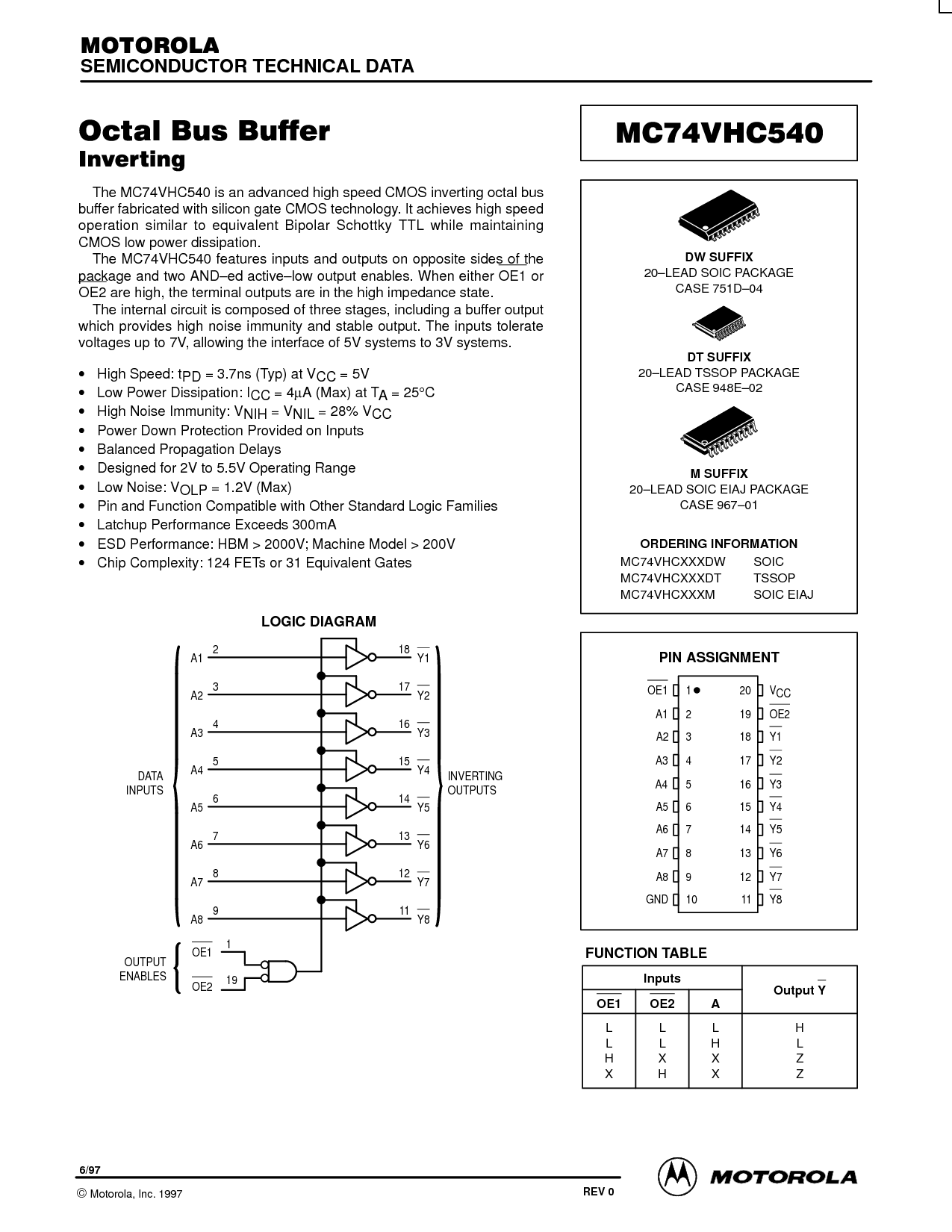

MC74VHC540

管脚 分配

A5

A3

A2

A1

OE1

地

A8

A7

A6

A4 5

4

3

2

1

10

9

8

7

6

14

15

16

17

18

19

20

11

12

13

Y3

Y2

Y1

OE2

v

抄送

Y8

Y7

Y6

Y5

Y4

dw 后缀

20–lead soic 包装

案例 751d–04

订购 信息

MC74VHCXXXDW

MC74VHCXXXDT

MC74VHCXXXM

SOIC

TSSOP

soic eiaj

dt 后缀

20–lead tssop 包装

案例 948e–02

m 后缀

20–lead soic eiaj 包装

案例 967–01

l

l

h

x

l

l

x

h

l

h

x

x

功能 表

输入

输出 y

OE1 OE2 一个

h

l

z

z