mc56f8346/d

rev. 8.0, 6/2004

© 摩托罗拉, 股份有限公司., 2004. 全部 权利 保留.

56F8346

初步 技术类 数据

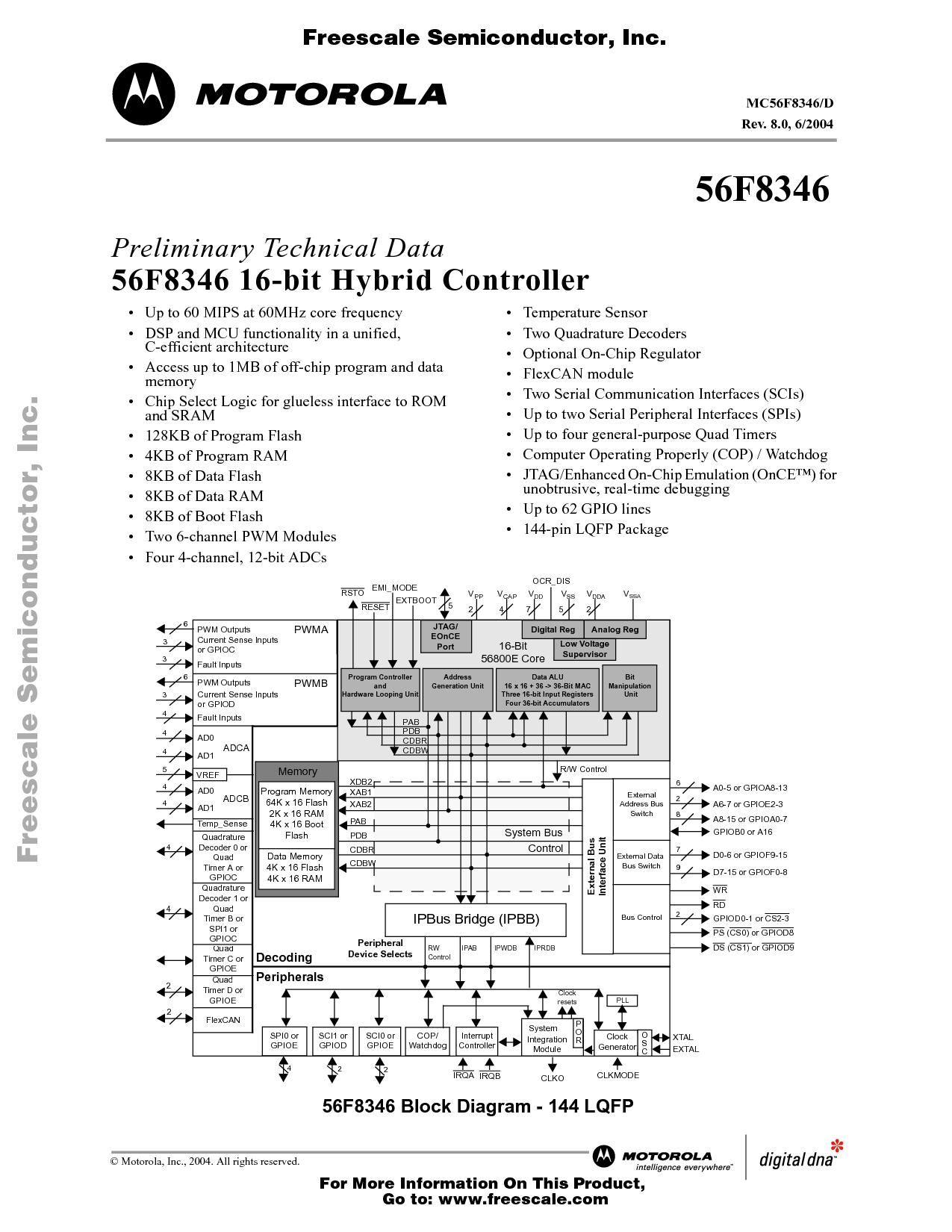

56f8346 16-有点 混合动力 控制器

• 向上 至 60 mips 在 60mhz 核心 频率

• dsp 和 mcu 功能 入点 一个 统一,

c-高效 体系结构

• 访问权限 向上 至 1mb 的 片外 程序 和 数据

记忆

• 芯片 选择 逻辑 用于 无胶 接口 至 rom

和 sram

• 128kb 的 程序 闪光灯

• 4kb 的 程序 ram

• 8kb 的 数据 闪光灯

• 8kb 的 数据 ram

• 8kb 的 引导 闪光灯

• 两个 6-频道 pwm 模块

• 四 4-频道, 12-有点 adcs

• 温度 传感器

• 两个 正交 解码器

• 可选 片上 调节器

• flexcan 模块

• 两个 串行 通信 接口 (scis)

• 向上 至 两个 串行 外围设备 接口 (spis)

• 向上 至 四 通用 四边形 计时器

• 计算机 操作 适当地 (cop) / 看门狗

• jtag/增强型 片上 仿真 (once™) 用于

unobtrusive, 实时 调试

• 向上 至 62 gpio 线条

• 144-管脚 lqfp 包装

56f8346 块 图表 - 144 lqfp

程序 控制器

和

硬件 循环 单位

数据 alu

16 x 16 + 36 -> 36-有点 mac

三个 16-有点 输入 寄存器

四 36-有点 蓄能器

地址

世代 单位

有点

操纵

单位

PLL

时钟

发电机

EXTAL

中断

控制器

cop/

看门狗

sci1 或

GPIOD

4

外部

地址 总线

开关

外部 总线

接口 单位

2

CLKMODE

IRQA

IRQB

外部 数据

总线 开关

PDB

PDB

XAB1

XAB2

XDB2

CDBR

sci0 或

GPIOE

spi0 或

GPIOE

ipbus 桥梁 (ipbb)

集成

模块

系统

p

o

右

o

s

c

解码

外围设备

外围设备

设备 选择

rw

控制

IPAB IPWDB IPRDB

2

系统 总线

右/w 控制

PAB

PAB

CDBW

CDBR

CDBW

时钟

重置

jtag/

EOnCE

港口

数字 注册

模拟 注册

低 电压

主管

v

盖

v

dd

v

ss

v

DDA

v

SSA

5

47 52

v

pp

2

ocr_dis

重置

EXTBOOT

emi_模式

RSTO

4

3

6

pwm 产出

故障 输入

PWMA

电流 感觉 输入

或 gpioc

3

4

6

pwm 产出

故障 输入

PWMB

电流 感觉 输入

或 gpiod

3

四边形

计时器 d 或

GPIOE

四边形

计时器 c 或

GPIOE

AD0

AD1

ADCA

2

5

正交

解码器 0 或

四边形

计时器 一个 或

GPIOC

FlexCAN

2

4

AD0

AD1

4

4

4

温度_感觉

正交

解码器 1 或

四边形

计时器 b 或

spi1 或

GPIOC

4

CLKO

总线 控制

6

2

8

7

9

2

XTAL

ds(cs1)或 gpiod9

ps(cs0)或 gpiod8

gpiod0-1 或 cs2-3

rd

wr

d7-15 或 gpiof0-8

d0-6 或 gpiof9-15

gpiob0 或 a16

a8-15 或 gpioa0-7

a0-5 或 gpioa8-13

a6-7 或 gpioe2-3

VREF

ADCB

16-有点

56800e 核心

数据 记忆

4k x 16 闪光灯

4k x 16 ram

记忆

程序 记忆

64k x 16 闪光灯

2k x 16 ram

4k x 16 引导

闪光灯

控制

f

右

e?

e?

s

c

一个

l

e?

s

e?

m

我

c

o

n

d

u

c

t

o

右

,

我

飞思卡尔 半导体, 公司

用于 更多 信息 开启 这个 产品,

走 至: www.飞思卡尔.com

n

c

.

.

.