512k x 8 静态 ram

CY7C1049V33

柏树 半导体 公司

• 3901 北 第一 街道 • San Jose • ca 95134 • 408-943-2600

六月 2, 1999

3

特点

• 高 速度

—t

AA

= 15 ns

• 低 活动 电源

— 504 mw (最大值.)

• 低 cmos 备用 电源 (商业 l 版本)

— 1.8 mw (最大值.)

• 2.0v 数据 保留 (660

µ

w 在 2.0v 保留)

• 自动 掉电 当 取消选择

• ttl-兼容 输入 和 产出

• 容易 记忆 扩展 与 ce

和 oe特点

功能 描述

这 cy7c1049v33 是 一个 高性能 cmos 静态 ram

有组织的 作为 524,288 字词 由 8 比特. 容易 记忆 expan-

锡宁 是 提供 由 一个 活动 低 芯片 启用 (ce

), 一个 活动

低 输出 启用 (oe

), 和 三态 驱动程序. 写作 至

这 设备 是 已完成 由 服用 芯片 启用 (ce

) 和

写 启用 (我们

) 输入 低. 数据 开启 这 八 我/o 针脚 (我/o

0

通过 我/o

7

) 是 然后 书面 进入 这 位置 指定 开启 这

地址 针脚 (一个

0

通过 一个

18

).

阅读 从 这 设备 是 已完成 由 服用 芯片

启用 (ce

) 和 输出 启用 (oe) 低 同时 强迫 写

启用 (我们

) 高. 下 这些 条件, 这 内容 的

这 记忆 位置 指定 由 这 地址 针脚 将 出现

开启 这 我/o 针脚.

这 八 输入/输出 针脚 (我/o

0

通过 我/o

7

) 是 已放置 入点 一个

高阻抗 州 当 这 设备 是 取消选择 (ce

高), 这 产出 是 已禁用 (oe高), 或 期间 一个 写

操作 (ce

低, 和 我们 低).

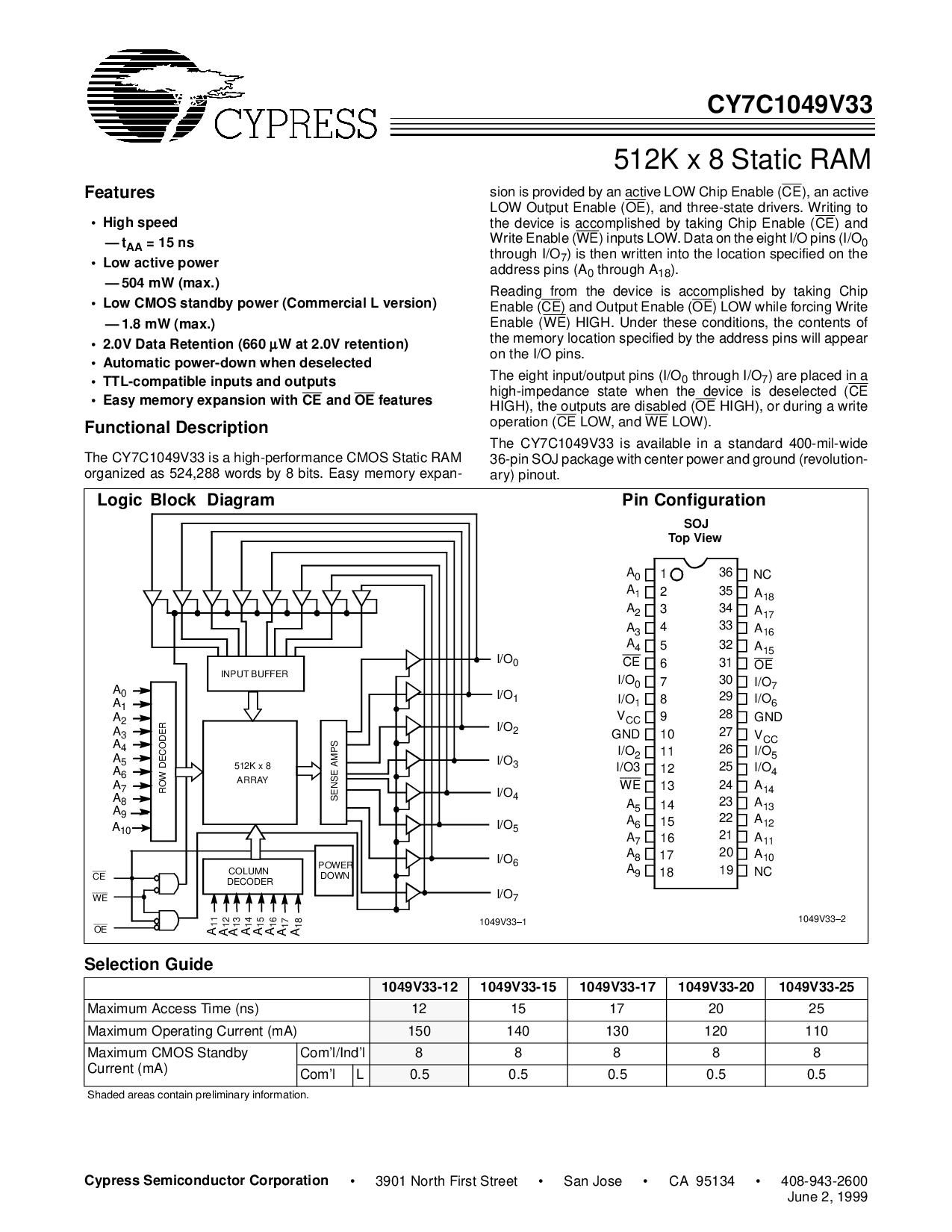

这 cy7c1049v33 是 可用 入点 一个 标准 400-密耳-宽

36-管脚 soj 包装 与 中心 电源 和 接地 (革命-

ary) 引出线.

14

15

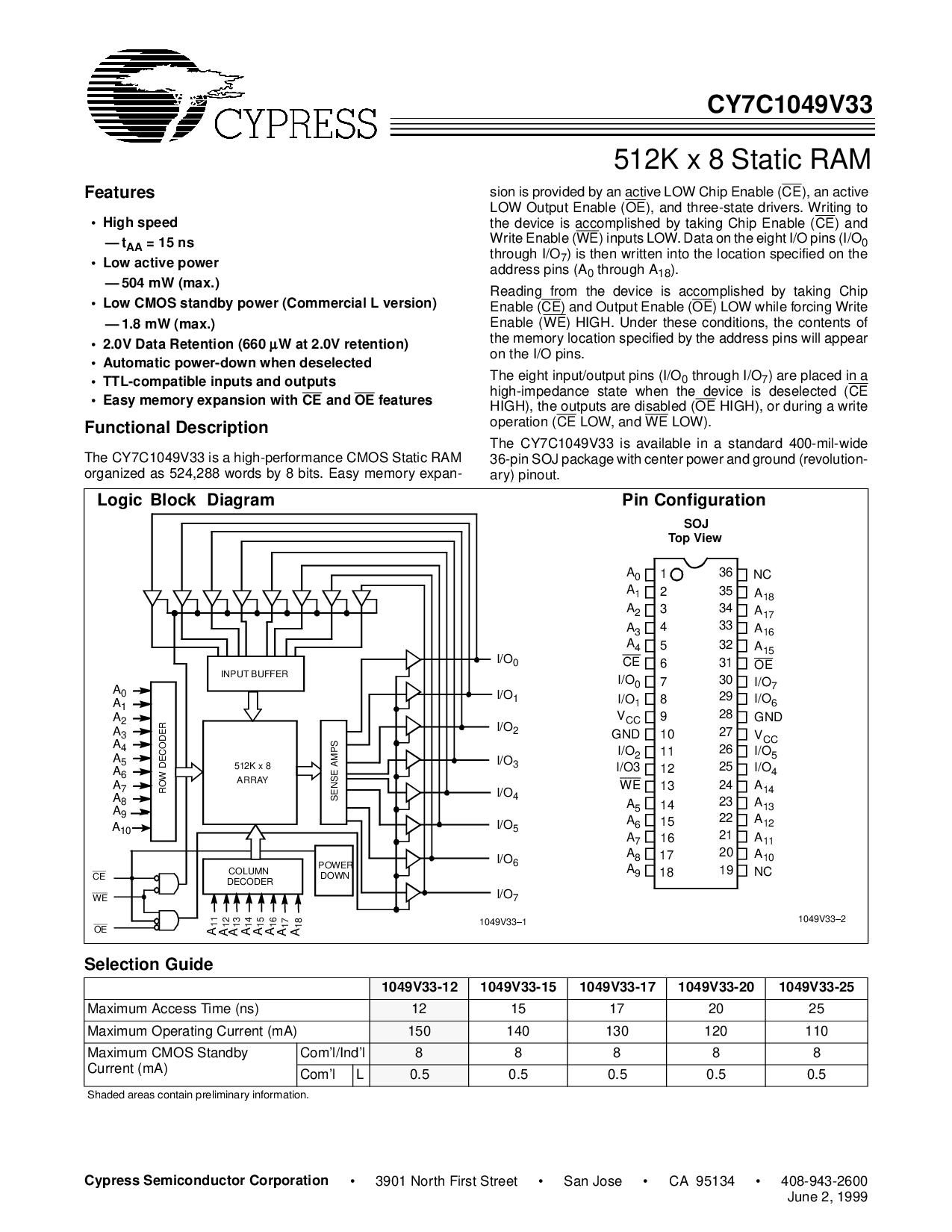

逻辑 块 图表 管脚 配置

一个

1

一个

2

一个

3

一个

4

一个

5

一个

6

一个

7

一个

8

色谱柱

解码器

行 解码器

感觉 安培数

输入 缓冲区

电源

向下

我们

oe

我/o

0

我/o

1

我/o

2

我/o

3

512k x 8

阵列

我/o

7

我/o

6

我/o

5

我/o

4

一个

0

一个

11

一个

13

一个

12

一个

ce

一个

一个

16

一个

17

1

2

3

4

5

6

7

8

9

10

11

14

23

24

28

27

26

25

29

32

31

30

顶部view

SOJ

12

13

33

36

35

34

16

15

21

22

地

一个

1

一个

2

一个

3

一个

4

一个

5

一个

6

一个

7

一个

8

我们

v

抄送

一个

18

一个

15

一个

12

一个

14

我/o

5

我/o

4

1049V33–1

一个

9

一个

0

我/o

0

我/o

1

我/o

2

oe

一个

17

一个

16

一个

13

ce

1049V33–2

一个

9

一个

18

18

17

19

20

地

我/o

7

我/o3

我/o

6

v

抄送

一个

10

一个

11

nc

nc

一个

10

选择 指南

1049v33-12 1049v33-15 1049v33-17 1049v33-20 1049v33-25

最大值 访问权限 时间 (ns) 12 15 17 20 25

最大值 操作 电流 (ma) 150 140 130 120 110

最大值 cmos 备用

电流 (ma)

com’l/指示’l 8888 8

Com’l l 0.5 0.5 0.5 0.5 0.5

阴影 区域 包含 初步 信息.