初步

3.3v 四边形 sonet 收发器

CY7B9514V

柏树 半导体 公司

• 3901 北 第一 街道 • San Jose • ca 95134 • 408-943-2600

九月 8

,1998

18,

4V

特点

• sonet/sdh 和 atm 兼容

• 时钟 和 数据 回收 从 51.84- 或 155.52-mhz

数据流

• 155.52-mhz 时钟 乘法 从 19.44-mhz 来源

• 51.84-mhz 时钟 乘法 从 6.48-mhz 来源

• ±1% 频率 agility

• 线 接收器 输入: 否 外部 缓冲 必填项

• 差速器 输出 缓冲

• 100k pecl 兼容 我/o

• 否 输出 时钟 “drift” 无 数据 过渡

• 链接 状态 指示

• 环回 测试

•

双 参考 时钟 输入 和 参考 时钟 输出

• 过渡 之间 refclks 是 减速 至 防止 数据

回收 错误

• 单独 +3.3v ±10% 供应

• 100-管脚 tqfp

• 兼容 与 光纤 模块, 同轴 电缆, 和

扭曲 对 媒体

• 掉电 选项 至 最小化 电源 或 串扰

• 低 操作 电流: &指示灯;400 ma

•

0.8

µ

BiCMOS

功能 描述

这 四边形 pmd atm 收发器 是 已使用 入点 sonet/sdh 和

atm 应用程序 至 恢复 时钟 和 数据 信息 从 一个

155.52-mhz 或 51.84-mhz nrz 或 nrzi 串行 数据 溪流

和 至 提供 差速器 数据 缓冲 用于 这 发送 侧面

的 这 系统.

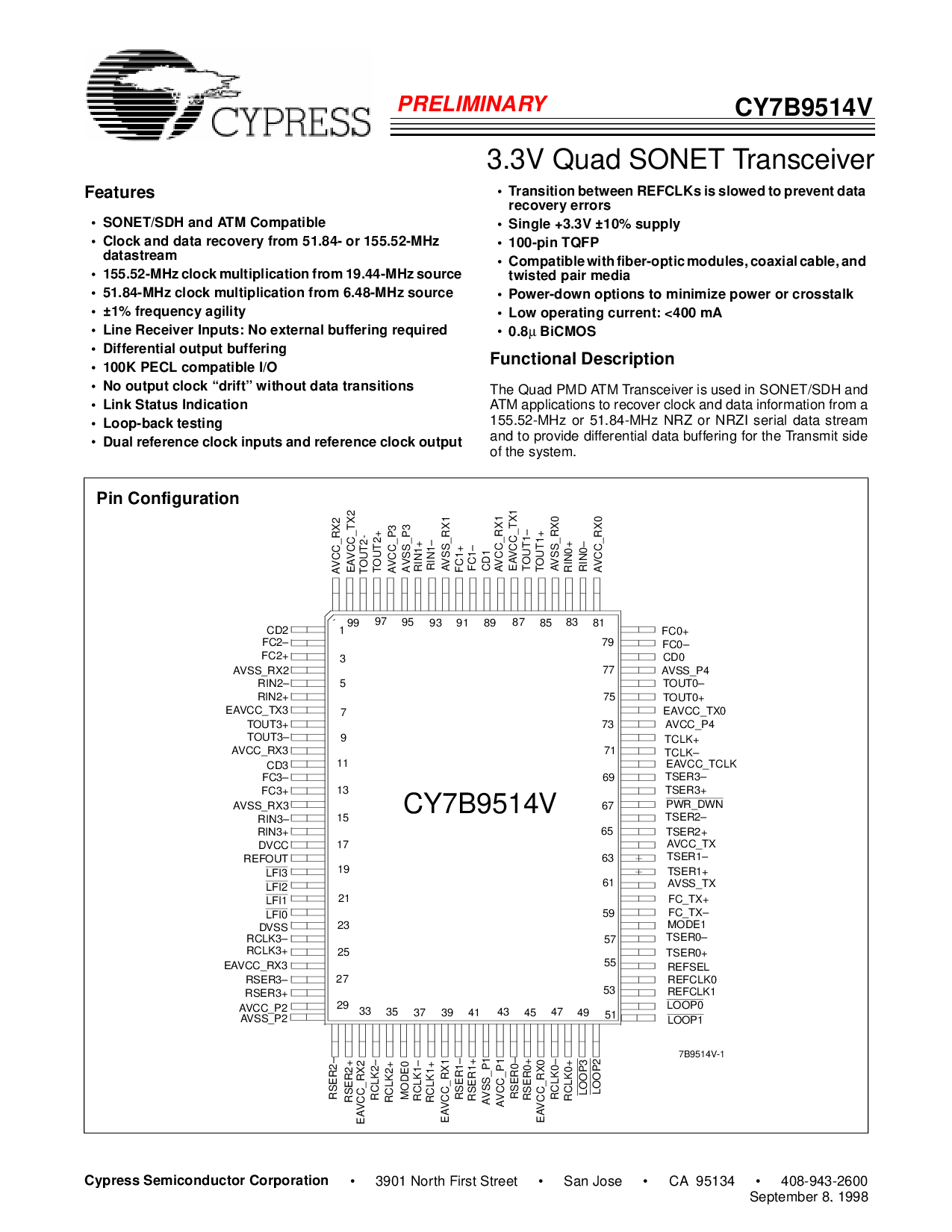

RIN2–

RIN2+

avss_rx2

FC2–

FC2+

CD2

eavcc_tx3

至UT3+

TOUT3–

avcc_rx3

RIN3–

RIN3+

avss_rx3

FC3–

FC3+

CD3

REFOUT

LFI3

RCLK3–

eavcc_rx3

RSER3–

avcc_p2

AVSs_p2

LOOP0

LOOP1

RSER2–

RCLK2–

eavcc_rx2

RSER2+

avcc_rx0

RIN0+

RIN0–

eavcc_tx0

至UT0–

至UT0+

TCLK+

TCLK–

REFCLK0

REFCLK1

REFSEL

LFI2

LFI1

LFI0

设计验证抄送

DVSs

RCLK3+

RSER3+

eavcc_tclk

TSER3–

pwr_dwn

TSER1–

TSER1+

avss_tx

TSER0–

TSER0+

MODE1

avcc_p4

avss_p4

TSER3+

TSER2–

TSER2+

avcc_tx

RCLK2+

RCLK1+

RCLK1–

MODE0

eavcc_rx1

avss_p1

RSER1+

RSER1–

avcc_p1

eavcc_rx0

RSER0+

RSER0–

RCLK0–

LOOP2

LOOP3

RCLK0+

avcc_rx2

TOUT2+

至ut2-

eavcc_tx2

avcc_p3

FC1+

CD1

AVSs_p3

FC1–

RIN1–

RIN1+

avss_rx1

avcc_rx1

eavcc_tx1

至UT1+

TOUT1–

avss_rx0

FC0–

FC0+

CD0

3

5

7

9

11

13

15

17

19

21

23

25

27

29

73

71

69

67

65

63

61

59

57

55

53

51

79

77

75

1

33

35

37 39 41

43

45

47

49

97

95

93 91 89

87

85

83

8199

fc_tx+

fc_tx–

7b9514v-1

CY7B9514V

管脚 配置