2k x 16 双port 静态 ram

CY7C133

CY7C143

柏树 半导体 公司

• 3901 北 第一 街道 • San Jose • ca 95134 • 408-943-2600

october 14, 1999

特点

• 真 双端口 记忆 细胞 哪个 允许

同时 读取 的 这 相同 记忆 位置

• 2k x 16 组织机构

• 0.65-微米 cmos 用于 最佳 速度/电源

• 高速 访问权限: 25/35/55 ns

• 低 操作 电源: 我

抄送

= 150 ma (典型值.)

• 完全 异步 操作

• 主人 cy7c133 展开 数据 总线 宽度 至 32 比特 或

更多 使用 奴隶 cy7c143

• 忙 输入 旗子 开启 cy7c133; 忙 输出 旗子 开启

CY7C143

• 可用 入点 68-管脚 plcc

• 引脚兼容 和 功能上 等效 至 idt7133

和 idt7143

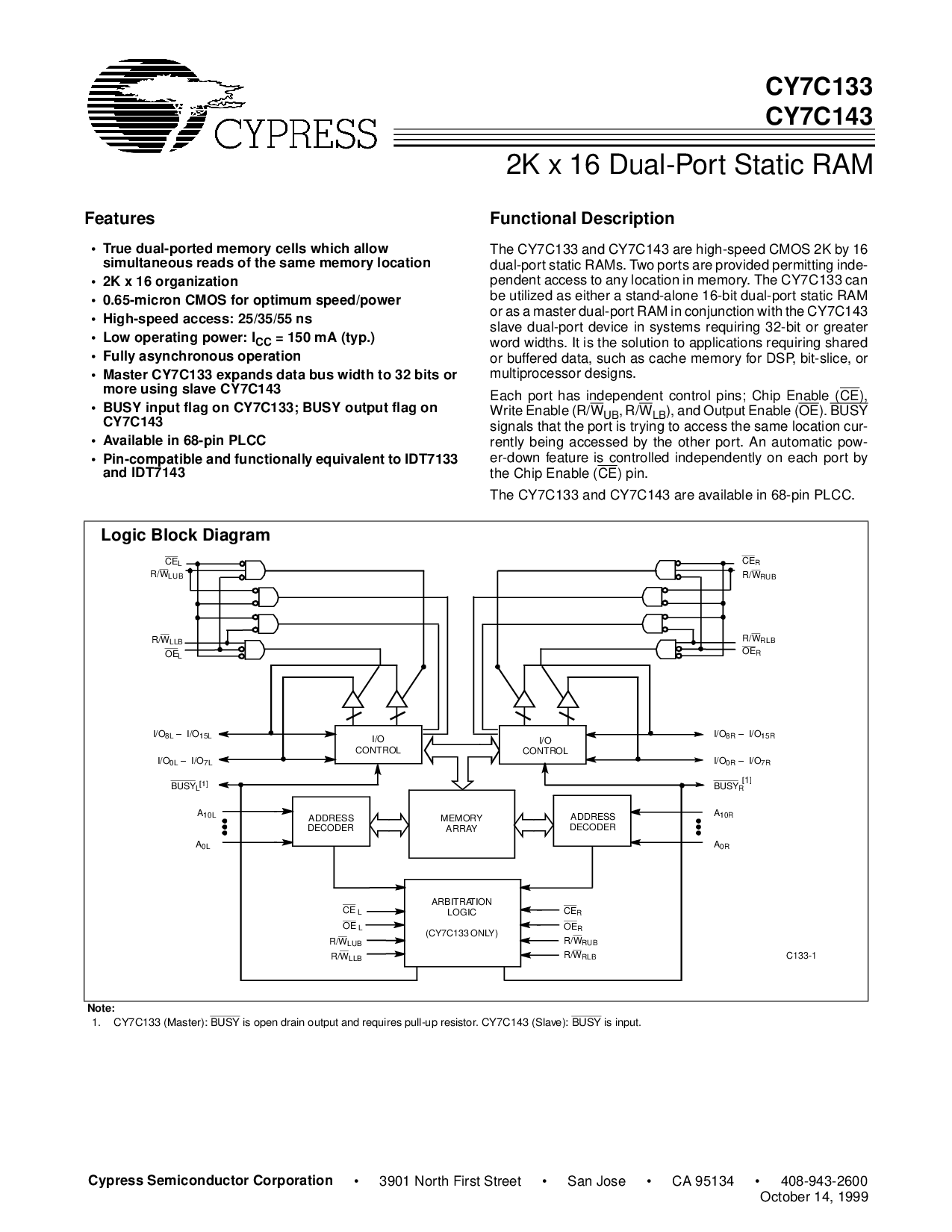

功能 描述

这 cy7c133 和 cy7c143 是 高速 cmos 2k 由 16

双端口 静态 rams. 两个 端口 是 提供 允许 inde-

悬挂式 访问权限 至 任何 位置 入点 记忆. 这 cy7c133 可以

是 已利用 作为 要么 一个 单机 16-有点 双端口 静态 ram

或 作为 一个 主人 双端口 ram 入点 连接词 与 这 cy7c143

奴隶 双端口 设备 入点 系统 要求 32-有点 或 更大

字 宽度. 它 是 这 解决方案 至 应用程序 要求 共享

或 缓冲 数据, 这样的 作为 高速缓存 记忆 用于 dsp, 有点-切片, 或

多处理机 设计.

每个 港口 有 独立 控制 针脚; 芯片 启用 (ce

),

写 启用 (右/w

ub

, 右/w

磅

), 和 输出 启用 (oe). 忙

信号 那 这 港口 是 正在尝试 至 访问权限 这 相同 位置 cur-

租金 正在 已访问 由 这 其他 港口. 一个 自动 pow-

er-向下 功能 是 受控 独立 开启 每个 港口 由

这 芯片 启用 (ce

) 管脚.

这 cy7c133 和 cy7c143 是 可用 入点 68-管脚 plcc.

备注:

1. cy7c133 (主人): 忙

是 打开 排水管 输出 和 需要 上拉 电阻. cy7c143 (奴隶): 忙是 输入.

c133-1

右/w

LUB

ce

l

oe

l

一个

10L

一个

0L

右/w

RUB

ce

右

ce

右

oe

右

ce

l

oe

l

右/w

LUB

右/w

RUB

我/o

8L

– 我/o

15L

arbitra操作

逻辑

(cy7c133 仅)

控制

我/o

记忆

阵列

地址

解码器

地址

解码器

忙

l

[1]

控制

我/o

右/w

LLB

右/w

RLB

我/o

0L

– 我/o

7L

右/w

RLB

oe

右

一个

10R

一个

0R

我/o

8R

– 我/o

15R

忙

右

[]

我/o

0R

– 我/o

7R

右/w

LLB

1

逻辑 块 图表