预付款 信息

2.5v 4k/16k/64k x 80 单向

同步 先进先出 w/总线 匹配

CY7C4808V25

CY7C4806V25

CY7C4804V25

柏树 半导体 公司

• 3901 北 第一 街道 • San Jose • ca 95134 • 408-943-2600

12月 16, 1999

5/0251

特点

• 高-速度, 低-电源, 单向, 先进先出 先出

(先进先出) 回忆 w/总线 匹配 能力

• 64k x 80 (cy7c4808v25)

• 16k x 80 (cy7c4806v25)

• 4k x 80 (cy7c4804v25)

• 2.5v ± 125 mv 电源 供应

• 预制 使用 柏树 0.21-微米 cmos 技术-

ogy 用于 最佳 速度/电源

• 个人 时钟 频率 向上 至 200 mhz (5 ns

阅读/写 循环 次)

• 高速 访问权限 与 t

一个

= 3.5

• 总线 匹配 开启 两者都有 端口: x80, x40, x20, x10

• 自由运行 clka 和 clkb. 时钟 将 是 asyn-

时间 或 重合

• cy 标准 或 第一-字 fall-穿透 模式

• 串行 和 平行 编程 的 几乎 空/已满

旗帜, 每个 与 3 默认 数值 (8, 16, 64)

• 主人 和 部分 重置 能力

• 重发 能力

• 全部 我/操作系统 是 1.5v hstl

• 大 或 小 字节序 格式 开启 港口 b

• 288 fbga 19 mm x 19 mm (1.0-mm 球 变桨) 包装

• 宽度 和 深度 扩展 能力

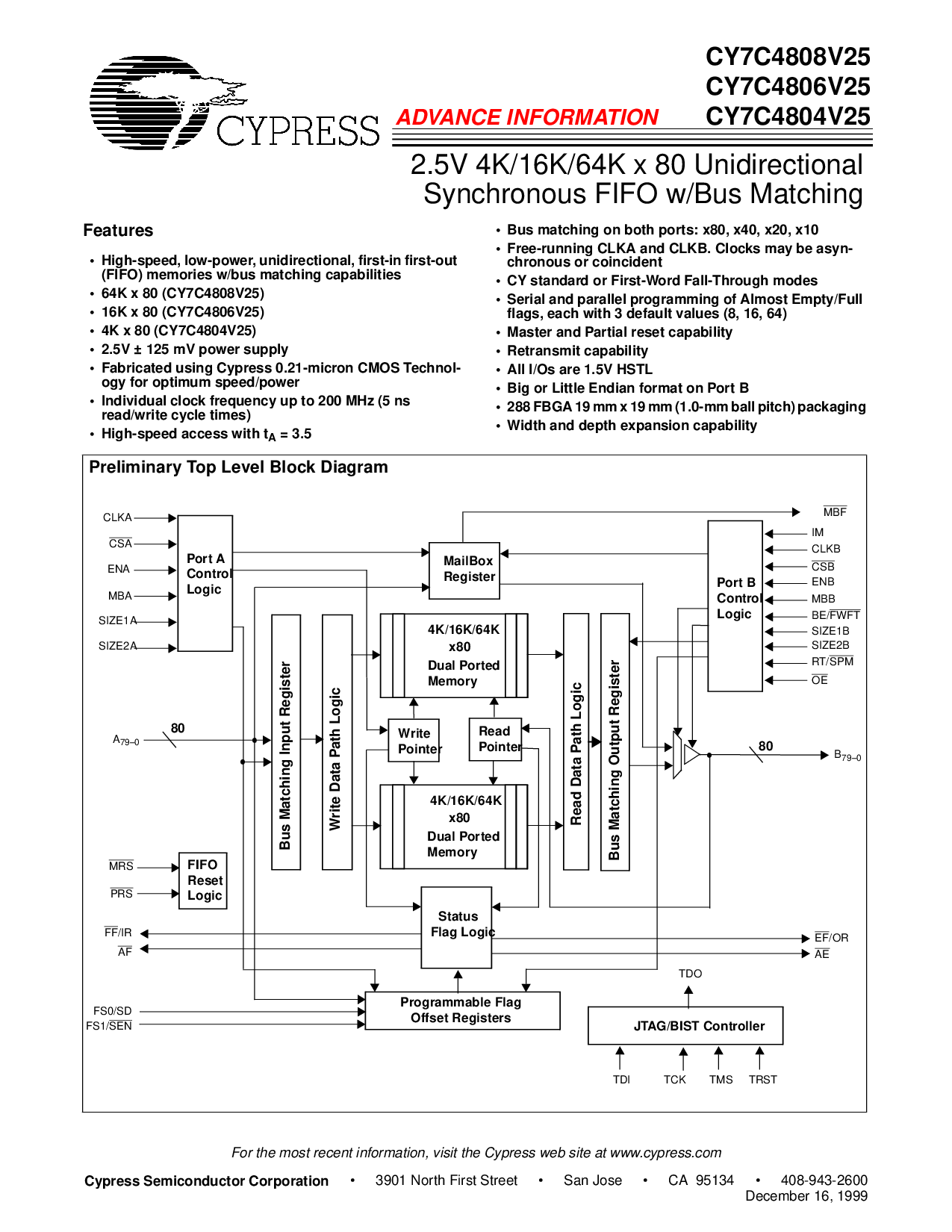

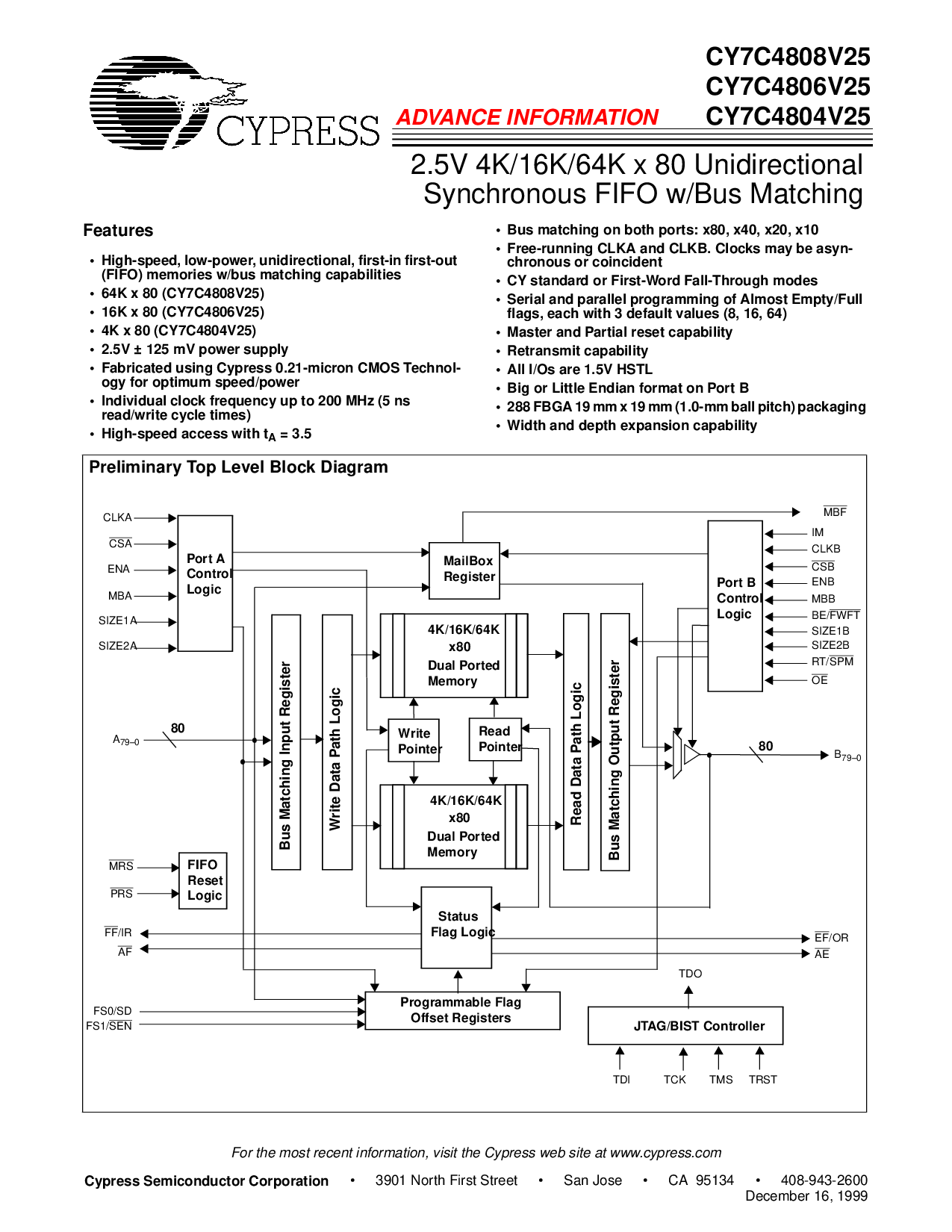

初步 顶部 水平 块 图表

港口 一个

控制

逻辑

port b

控制

逻辑

邮箱

注册

总线 匹配 输入 注册

总线 匹配 输出 注册

写

指针

阅读

指针

状态

旗子 逻辑

可编程 旗子

4k/16k/64k

x80

双 已移植

记忆

先进先出

CLKA

CSA

ena

MBA

MRS

PRS

ff/红外线

af

fs0/sd

fs1/森

一个

79–0

B

79–0

CLKB

CSB

ENB

MBB

是/fwft

SIZE1B

SIZE2B

ef

/或

不良事件

MBF

阅读 数据 路径 逻辑

80

80

重置

逻辑

4k/16k/64k

x80

双 已移植

记忆

SIZE1A

SIZE2A

写 数据 路径 逻辑

rt/spm

即时消息

TDI tck TMS TRST

oe

jtag/bist 控制器

TDO

偏移量 寄存器

用于 这 大多数 最近 信息, 参观 这 柏树 web 现场 在 www.柏树.com