pentium®/二, 6x86, k6 时钟 合成器/驾驶员 用于 台式机 pcs

与 英特尔 82430tx, 82440lx 或 ali 四/iv+, agp 和 3 dimms

CY2273A

柏树 半导体 公司

• 3901 北 第一 街道 • San Jose • ca 95134 • 408-943-2600

october 12

,1998

特点

• 混合 2.5v 和 3.3v 操作

• 完成 时钟 解决方案 用于 pentium®, pentium® 二,

cyrix, 和 amd 处理器-基于 motherboards

— 四 cpu 时钟 在 2.5v 或 3.3v

— 向上 至 十二 3.3v sdram 时钟

— 七 同步 pci 时钟, 一个 自由运行

— 一个 3.3v 48 mhz usb 时钟

— 一个 2.5v ioapic 时钟 (-3 选项 仅)

— 两个 agp 时钟 在 60 或 66.6mhz (-2 选项 仅)

— 一个 3.3v 参考. 时钟 在 14.318 mhz

•I

2

c™ 串行 配置 接口

• 工厂-非易失存储器 可编程 输出 驱动器 和 回转

费率 用于 emi customization

• 工厂-非易失存储器 可编程 cpu 时钟 频率

用于 自定义 配置

• 电源-向下, cpu 停止 和 pci 停止 针脚

• 可用 入点 节省空间 48-管脚 ssop 包装

功能 描述

这 cy2273a 是 一个 时钟 合成器/驾驶员 用于 一个 pentium, 钢笔-

tium 二, cyrix, 或 amd 处理器-基于 pc 使用 英特尔’s

82430tx, 82440lx, ali aladdin 四 或 aladdin iv+ chipsets.

这 cy2273a-1 产出 四 cpu 时钟 在 2.5v 或 3.3v 与

向上 至 83.3mhz 操作. 那里 是 七 pci 时钟, 正在运行

在 30 和 33.3mhz. 一个 的 这 pci 时钟 是 免费-正在运行.

另外, 这 零件 产出 向上 至 十二 3.3v sdram 时钟,

一个 3.3v usb 时钟 在 48 mhz, 和 一个 3.3v 参考 时钟

在 14.318 mhz. 这 cy2273a-2 是 类似, 除了 那

pciclk4 和 pciclk5 是 现在 agp 时钟. 这 cy2273a-3

是 更多 适合 至 pentium 二 系统, 作为 它 产出 一个 2.5v

ioapic 时钟. 最后, 这 cy2273a-4 是 类似 至 这

cy2273a-1 除了 那 是 支架 0-ns cpu-pci 延迟.

这 cy2273a 拥有 电源-向下, cpu 停止, 和 pci

停止 针脚 用于 电源 管理 控制. 这些 输入 是

多路复用 与 sdram 时钟 产出, 和 是 已选择 当

这 模式 管脚 是 驱动 低. 另外, 这 信号 是 syn-

按时间顺序 开启-芯片, 和 确保 无故障 过渡 开启 这

产出. 当 这 cpu_停止

输入 是 已断言, 这 cpu

时钟 产出 是 驱动 低. 当 这 pci_停止

输入 是

已断言, 这 pci 时钟 产出 (除了 这 自由运行 pci

时钟) 是 驱动 低. 当 这 pwr_dwn

管脚 是 已断言,

这 参考 振荡器 和 plls 是 关闭 向下, 和 全部 出点-

看跌期权 是 驱动 低.

这 cy2273a 产出 是 设计 用于 低 emi 排放量.

受控 上升 和 坠落 次, 独一无二 输出 驾驶员 电路 和

工厂-非易失存储器 可编程 输出 驱动器 和 回转率 en-

能 最优 配置 用于 emi 控制.

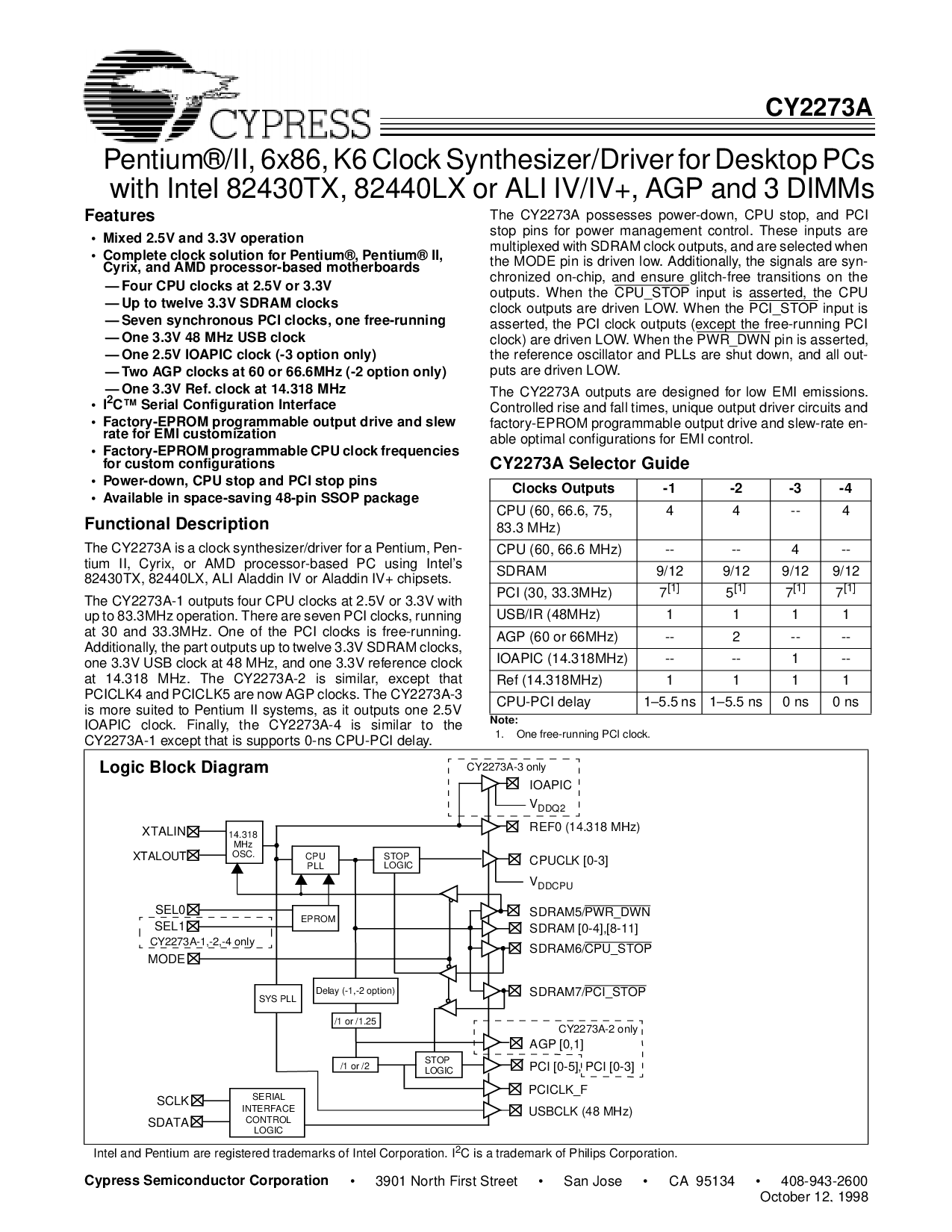

cy2273a 选择器 指南

备注:

1. 一个 自由运行 pci 时钟.

时钟 产出 -1 -2 -3 -4

cpu (60, 66.6, 75,

83.3 mhz)

44--4

cpu (60, 66.6 mhz) -- -- 4 --

SDRAM 9/12 9/12 9/12 9/12

pci (30, 33.3mhz) 7

[1]

5

[1]

7

[1]

7

[1]

usb/红外线 (48mhz) 1 1 1 1

agp (60 或 66mhz) -- 2 -- --

ioapic (14.318mhz) -- -- 1 --

参考 (14.318mhz) 1 1 1 1

cpu-pci 延迟 1–5.5 ns 1–5.5 ns 0 ns 0 ns

英特尔 和 pentium 是 已注册 商标 的 英特尔 公司. 我

2

c 是 一个 商标 的 飞利浦 公司.

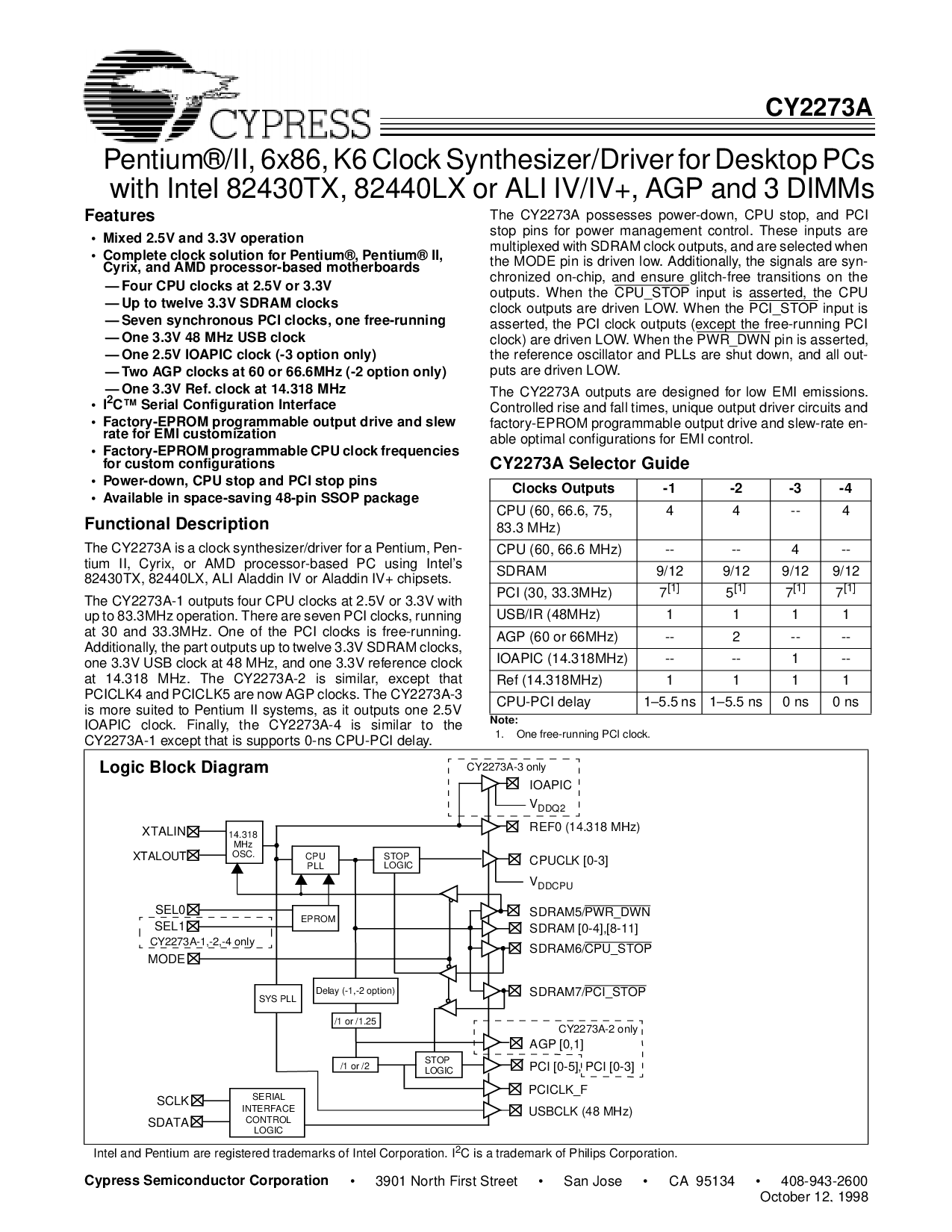

逻辑 块 图表

IOAPIC

v

DDQ2

cy2273a-3 仅

非易失存储器

XTALOUT

XTALIN

14.318

MHz

osc.

sdram [0-4],[8-11]

SEL0

sdram7/pci_停止

CPU

PLL

模式

SCLK

SDATA

ref0 (14.318 mhz)

cpuclk [0-3]

v

DDCPU

sdram6/cpu_停止

pci [0-5], pci [0-3]

pciclk_f

停止

停止

逻辑

逻辑

sdram5/pwr_dwn

SEL1

usbclk (48 mhz)

系统 pll

agp [0,1]

接口

控制

逻辑

串行

/1 或 /2

cy2273a-1,-2,-4 仅

cy2273a-2 仅

/1 或 /1.25

延迟 (-1,-2 选项)