PM73123

8 链接 消费电子展/dbces aal1 sar

aal1gator™-8

pmc-1991272 (r2)

专有 和 confidential 至 pmc

-

sierra, 股份有限公司., 和 用于 其 客户

’

内部 使用

版权 pmc

-

sierra, 公司 2001

特点

•

支架 八 结构化/unstructured

t1, e1 链接 或 一个 unstructured ds3,

e3 或 sts-1/stm-0 链接 结束 一个 aal1

cbr atm 网络.

•

符合 与 atm forum's 消费电子展 (af-

vtoa-0078), 和 itu-t 我.363.1.

•

支架 向上 至 256 vcs.

•

支架 n x 64 (连续的

频道) 和 m x 64 (非-

连续的 频道) 结构化 数据

格式 与 频道 关联的

信令 (cas) 支持.

•

内部 e1/t1 时钟 合成器

提供 用于 每个 线 哪个 可以 是

受控 通过 内部 同步

剩余 时间 邮票 (srts) 或 一个

内部 可编程 加权

正在移动 平均值 自适应 时钟

算法 入点 unstructured 模式. 时钟

合成器 可以 也 是 受控

外部 至 提供 customization 的

srts 或 自适应 时钟 方法.

•

提供 透明 变速器 的

ccs 和 cas 和 终止 的 cas

信令.

•

符合 与 atm forum's 动态

带宽 电路 仿真 服务

(dbces) af-vtoa-0085. 支架

慢车 频道 检测 通过 处理器

干预, cas 信令, 或 数据

图案 检测. 提供 慢车

频道 指示 开启 一个 按 频道

依据.

•

支架 aal0 模式, 可选择 开启 一个

按 vc 依据.

•

提供 发送 和 接收 缓冲区

哪个 可以 是 已使用 用于 oam 细胞 作为

井 作为 任何 其他 用户-已生成 细胞

这样的 作为 aal5 细胞 用于 atm 信令.

线 接口

•

支架 这 以下内容 灵活 线

接口:

•

八 个人 t1 或 e1 线条.

•

两个 h-mvip 线条 在 8 mhz.

•

一个 unstructured ds3, e3 或 sts-

1/stm-0 线.

•

提供 lineside 环回 支持 开启

一个 按 频道 依据.

utopia 接口

•

支架 52 mhz, 8/16-有点 水平 2,

多-phy 模式 (mphy) 与 奇偶校验,

8/16-有点 水平 1, sphy 和 8-有点

水平 1, atm 主人 模式.

•

提供 一个 可选 8/16-有点 任何-

PHY

™

奴隶 接口.

•

提供 一个 三个 细胞 先进先出 用于 utopia

环回 支持 开启 一个 按 vc 依据 或

一个 全球 依据.

发送 截面

•

提供 单独 已启用 按-vc

数据 和 信令 调节 入点 这

发送 细胞 方向 和 按 ds0

数据 和 信令 调节 入点 这

发送 线 方向. 包括 ds3

ais 调节 支持 入点 两者都有

方向.

•

提供 按-vc 配置 的 时间

插槽 已分配, cas 支持, 部分

细胞 尺寸, 数据 和 信令

调节, atm 细胞 页眉

定义.

•

生成 aal1 顺序 编号,

指针 和 srts 数值 入点

符合 与 itu-t 我.363.1.

多播 连接 是 支持.

•

提供 一个 专利 框架 基于

日历 队列 服务 算法 与

反-clumping 添加-队列 机制

那 生产 最小 cdv. 入点

unstructured 模式, 用途 非-框架

基于 时间安排 至 优化 cdv.

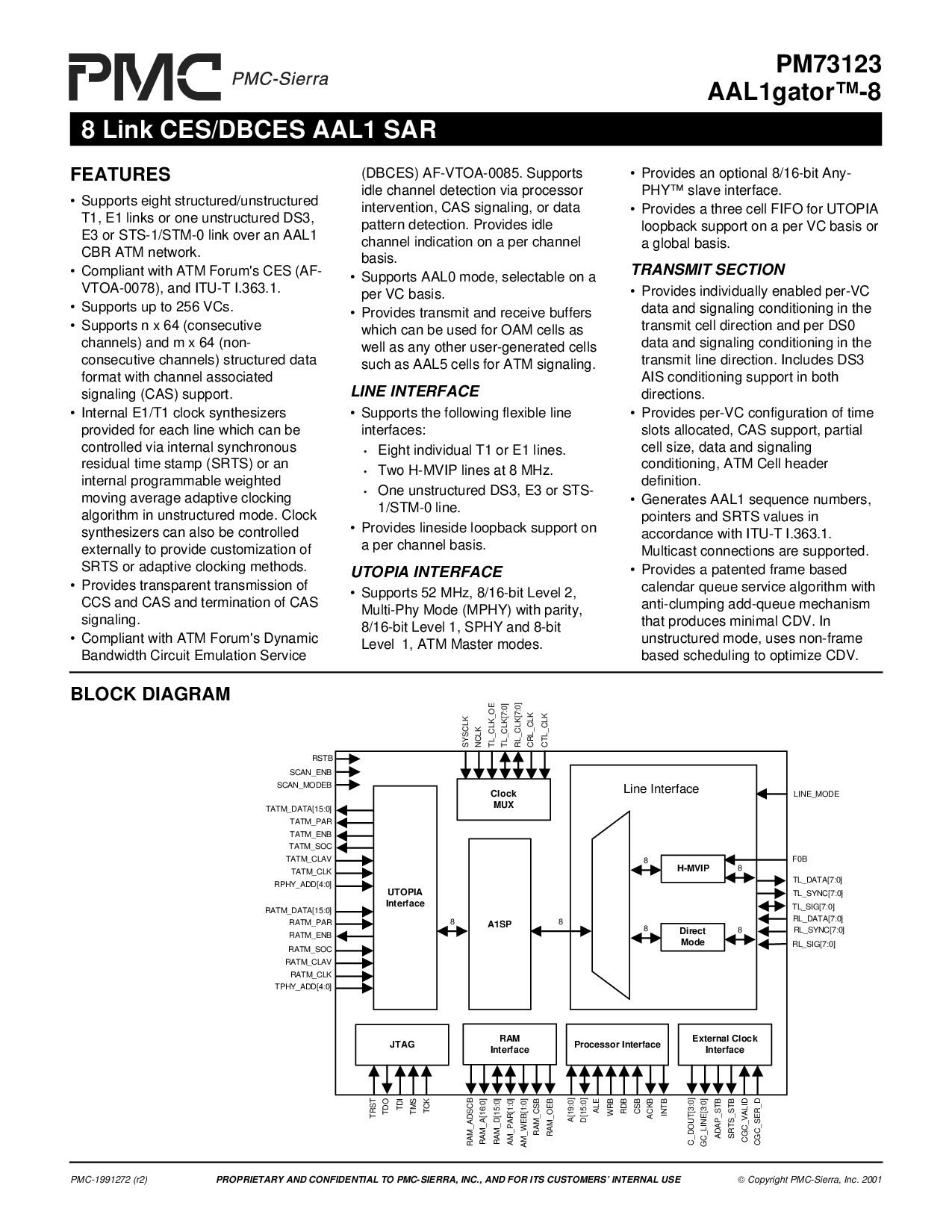

块 图表

UTOPIA

接口

8

tatm_data[15:0]

tatm_par

tatm_enb

tatm_soc

tatm_clav

tatm_clk

rphy_add[4:0]

ratm_data[15:0]

ratm_par

ratm_enb

ratm_soc

ratm_clav

ratm_clk

tphy_add[4:0]

A1SP

8

线 接口

JTAG

TRST

TDI

TMS

tck

TDO

ram

接口

ram_adscb

ram_d[15:0]

上午_par[1:0]

上午_web[1:0]

ram_csb

ram_oeb

ram_a[16:0]

处理器 接口

d[15:0]

WRB

RDB

CSB

ACKB

INTB

ALE

a[19:0]

外部 时钟

接口

c_dout[3:0]

adap_stb

srts_stb

cgc_有效

cgc_ser_d

gc_line[3:0]

SYSCLK

tl_clk_oe

tl_clk[7:0]

rl_clk[7:0]

crl_clk

ctl_clk

NCLK

时钟

mux

8

h-mvip

8

F0B

tl_sig[7:0]

tl_data[7:0]

tl_sync[7:0]

rl_sig[7:0]

rl_data[7:0]

rl_sync[7:0]

线_模式

8

直接

模式

8

RSTB

扫描_enb

扫描_modeb