初步 技术类 数据

sharc 和 这 sharc 徽标 是 已注册商标 的 ana日志 设备, 公司

SHARC

®

处理器

adsp-21267

rev. pra

信息 提供的 由 模拟 设备 是相信 至 是 准确 和 可靠.

然而, 否 责任 是 假设 由 模拟 设备 用于 其 使用, 也没有 用于 任何

侵权 的 专利 或 其他 权利 的 第三 缔约方 那 将 结果 从 其 使用.

规格 主题 至 变更 无 否tice. 否 许可证 是 授予 由 蕴涵

或 否则 下 任何 专利 或 专利 权利 的 模拟 设备. 商标 和

已注册 商标 是 这 财产 的 他们的 各自 业主.

一个 技术 方式, p.o. 框 9106, norwood, ma 02062-9106 美国

电话:781/329-4700 www.模拟.com

摘要

高 业绩 32-有点/40-有点 浮动 点 处理器

优化 用于 高 业绩 音频 加工

代码 兼容 与 全部 其他 sharc dsps

这 adsp-21267 流程 高 业绩 音频 同时

启用 低 系统 费用

音频 解码器 和 post processor-算法 支持.

非挥发性 记忆 可以 是 已配置 至 包含 一个 com-

组合 的 pcm 96 khz, dolby数字, dolby 数字 ex2,

dolby 专业版 逻辑 iix, dts 5.1, dts es 离散 6.1, dts-es

矩阵 6.1, dts neo:6, mpeg2x bc (2 频道) 和 others.

请参见 www.模拟.com/sharc 用于 一个 完成 列表

单指令 多个-数据 (simd) 计算 archi-

tecture—two 32-有点 ieee 浮动-点/32-有点 固定 点/

40-有点 扩展 精度 floa婷 点 计算

单位, 每个 与 一个 乘数, alu, 换档器, 和 注册 文件

高 带宽 我/o — 一个 平行港口, spi 港口, 4 串行 端口,

一个 数字 音频 接口 (dai) 和 jtag

dai 包含 两个 精度时钟 发电机 (pcg), 和

一个 输入 数据 港口 (idp) 那 包括 一个 平行 数据

收购 港口 (pdap), 和 三个 可编程 计时器,

全部 下 软件 控制 由这 信号 路由 单位 (sru)

片上 记忆 — 1m 有点 的片上 sram 和 一个 专用

3m 比特 的 片上 掩模可编程 rom

这 adsp-21267 是 可用 与 一个 150 mhz 核心 说明书

费率. 用于 完成 订购 信息, 请参见订购

指南 开启 第页 43

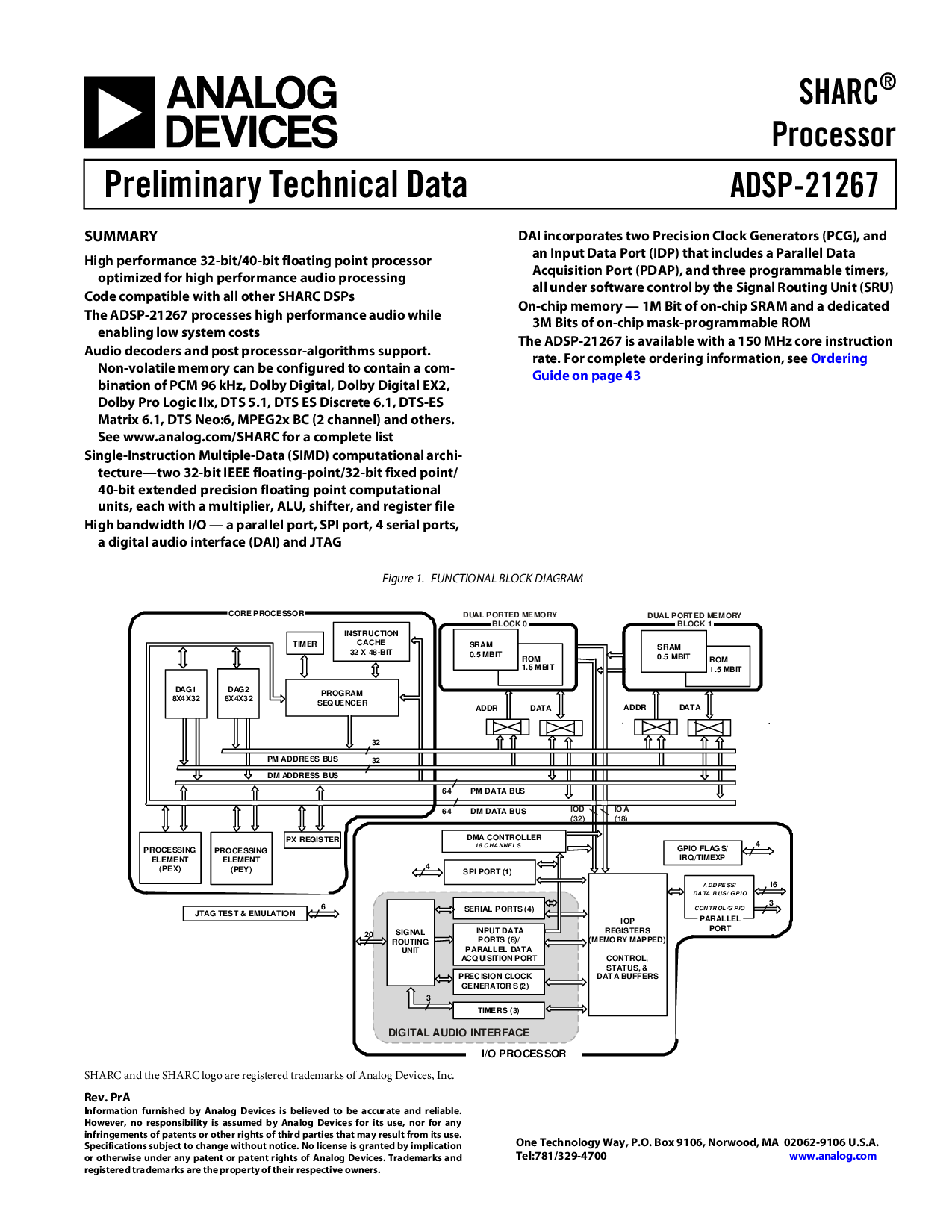

图 1. 功能 块 图表

SRAM

0. 5 m有点

rom

1. 5 mbi t

一个 d 博士 da t一个

px 瑞吉斯 之三

6

JTAG 测试一下 &放大器; 仿真

20

3

串行 p orts (4)

输入 数据

端口 (8)/

平行 数据

acq 用户界面 位置 port

ti 我 右s ( 3)

信号 nal

路由

联合国 它

精度 时钟

发电机 s (2)

数字 音频 接口

3

16

地址/

数据 总线/ gpio

一氧化碳 n t 右 o l / g PIO

平行

港口

IOP

寄存器

(mEMO ry 地图 ped)

控制,

状态, &放大器;

dat一个 缓冲区

4

SPI 港口 (1)

dma 控制器

18 频道

4

gpio 旗帜/

IRQ /提姆exp

我/o p ro 消费电子展 sor

io 一个

(18)

iod

(32)

专业版 ce SSI ng

元素

(pey )

加工

ELEME nt

(pex)

计时器

说明书

高速缓存

32 x 48 -b它

da G1

8X4X32

DAG2

8X 4X3 2

32

下午 地址 总线

dm 地址 总线

32

下午 数据 总线

dm 数据 总线

64

64

核心 p ROCE SSO 右

prog ram

序列 UE nce 右

地址 数据

双 已移植 记忆

块 0

d ua l p ort ed 我 m ory

块 1

SRAM

0.5 MBIT

rom

1.5 MBIT