32k/64kx18 低 电压 深 同步 fifos

cy7c4255v/cy7c4265v

cy7c4275v/cy7c4285v

柏树 半导体 公司

• 3901 北 第一 街道 • San Jose • ca 95134 • 408-943-2600

文件 #: 38-06012 rev. *a 修订 12月 26, 2002

285V

特点

• 3.3v 操作 用于 低 电源 消费 和 容易

集成 进入 低电压 系统

• 高-速度, 低-电源, 先进先出 先出 (先进先出)

回忆

• 8k x 18 (cy7c4255v)

• 16k x 18 (cy7c4265v)

• 32k x 18 (cy7c4275v)

• 64k x 18 (cy7c4285v)

• 0.35 微米 cmos 用于 最佳 速度/电源

• 高速 100-mhz 操作 (10-ns 阅读/写 循环

次)

• 低 电源

—

我

抄送

= 30 ma

—

我

SB

= 4 ma

•

完全 异步 和 同时 阅读 和 写

操作

•

空, 已满, 一半 已满, 和 可编程 几乎 空

和 几乎 已满 状态 旗帜

•

重发 功能

•

输出 启用 (oe

)

管脚

•

独立 阅读 和 写 启用 针脚

•

支架 自由运行 50% 职责 循环 时钟 输入

•

宽度 扩展 能力

•

深度 扩展 能力

•

64-管脚 10x10 stqfp

•

引脚兼容 密度 升级 至 cy7c42x5v-asc

家庭

•

引脚兼容 3.3v 解决方案 用于 cy7c4255/65/75/85

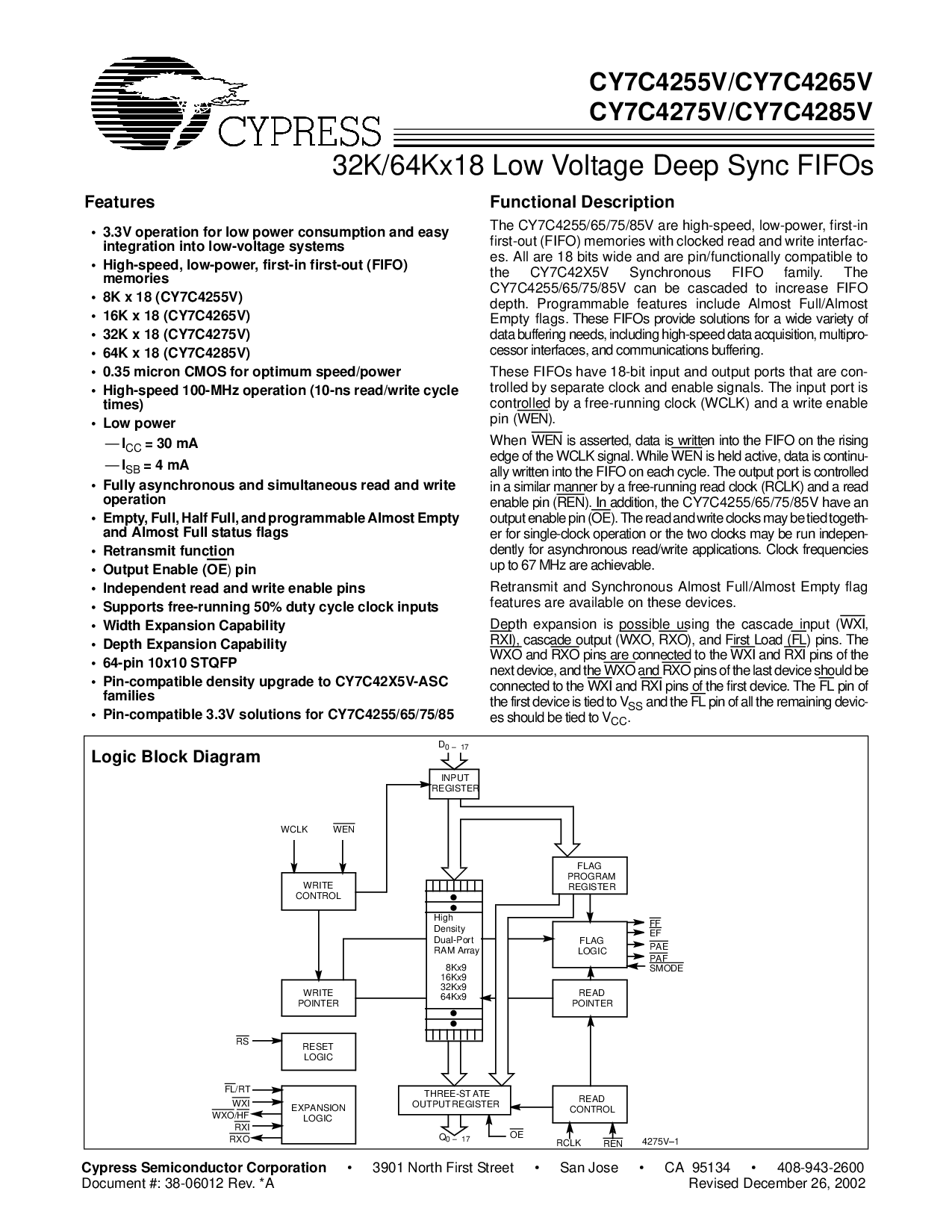

功能 描述

这 cy7c4255/65/75/85v 是 高-速度, 低-电源, 先进先出

先出 (先进先出) 回忆 与 时钟 阅读 和 写 interfac-

es. 全部 是 18 比特 宽 和 是 管脚/功能上 兼容 至

这 cy7c42x5v 同步 先进先出 家庭. 这

cy7c4255/65/75/85v 可以 是 级联 至 增加 先进先出

深度. 可编程 特点 包括 几乎 已满/几乎

空左前一个gs. 这些 fifos 提供 解决方案 用于 一个 宽 品种 的

数据 缓冲 需要, 包括 高速 数据 收购, multipro-

处理器 接口, 和 通信 缓冲.

这些 fifos 有 18-有点 输入 和 输出 端口 那 是 con-

被控制 由 分开 时钟 和 启用 信号. 这 输入 港口 是

受控 由 一个 自由运行 时钟 (wclk) 和 一个 写 启用

管脚 (wen

).

当 wen

是 已断言, 数据 是 书面 进入 这 先进先出 开启 这 上升

边缘 的 这 wclk 信号. 同时 wen是 持有 活动, 数据 是 连续-

盟友 书面 进入 这 先进先出 开启 每个 循环. 这 输出 港口 是 受控

入点 一个 类似 方式 由 一个 自由运行 阅读 时钟 (rclk) 和 一个 阅读

启用 管脚 (ren

). 入点 加法, 这 cY7C4255/65/75/85v 有 一个

输出 启用 管脚 (oe

). 这 阅读 和 写 时钟 将 是 系紧 togeth-

er 用于 单时钟 操作 或 这 两个 时钟 将 是 运行 独立-

丹迪德 用于 异步 阅读/写 应用程序. 时钟 频率

向上 至 67 mhz 是 可实现的.

重发 和 同步 几乎 已满/几乎 空 旗子

特点 是 可用 开启 这些 设备.

深度 扩展 是 可能 使用 这 级联 输入 (wxi

,

RXI

), 级联 输出 (wxo, rxo), 和 第一 荷载 (左前) 针脚. 这

WXO

和 rxo针脚 是 已连接 至 这 wxi和 rxi针脚 的 这

下一个 设备, 和 这 wxo和 rxo针脚 的 这 最后一个 设备 应该 是

已连接 至 这 wxi

和 rxi针脚 的 这 第一 设备. 这 左前 管脚 的

这 第一 设备 是 系紧 至 v

ss

和 这 左前管脚 的 全部 这 剩余 devic-

es 应该 是 系紧 至 v

抄送

.

q

0

–

17

4275V

–

1

三st 吃了

输出 注册

阅读

控制

旗子

逻辑

写

控制

写

指针

阅读

指针

重置

逻辑

扩展

逻辑

输入

注册

旗子

程序

注册

d

0

–

17

REN

rclk

ff

ef

PAE

WENWCLK

rs

左前/rt

WXI

oe

PAF

WXO/hf

RXI

RXO

SMODE

逻辑 块 图表

高

密度

双端口

ram 阵列

8Kx9

32Kx9

16Kx9

64Kx9