64/256/512/1k/2k/4k/8k x 9 同步 fifos

cy7c4421/4201/4211/4221

cy7c4231/4241/4251

柏树 半导体 公司

• 3901 北 第一 街道 • San Jose

,

ca 95134 • 408-943-2600

文件 #: 38-06016 rev. *c 修订 8月 2, 2005

特点

• 高-速度, 低-电源, 第一-入点, 先出 (先进先出)

回忆

— 64 × 9 (cy7c4421)

— 256 × 9 (cy7c4201)

— 512 × 9 (cy7c4211)

— 1k × 9 (cy7c4221)

— 2k × 9 (cy7c4231)

— 4k × 9 (cy7c4241)

— 8k × 9 (cy7c4251)

• 高速 100-mhz 操作 (10 ns 阅读/写 循环

时间)

•low 电源 (我

抄送

= 35 ma)

• 完全 异步 和 同时 阅读 和 写

操作

• 空, 已满, 和 程序可调式 几乎 空 和

几乎 已满 状态 旗帜

• ttl-兼容

• expandable 入点 宽度

• 输出 启用 (oe

) 管脚

• 独立 阅读 和 写 启用 针脚

• 中心 电源 和 接地 针脚 用于 减少 噪声

• 宽度-扩展 能力

• 空间 正在保存 7 mm × 7 mm 32-管脚 tqfp

•

引脚兼容 和 功能上 等效 至

idt72421, 72201, 72211, 72221, 72231, 和 72241

• 铅-免费 软件包 可用

功能 描述

这 cy7c42x1 是 高-速度, 低功耗 先进先出 回忆

与 时钟 阅读 和 写 接口. 全部 是 9 比特 宽. 这

cy7c42x1 是 引脚兼容 至 idt722x1. 可编程

特点 包括 几乎 已满/几乎 空 旗帜. 这些 fifos

提供 解决方案 用于 一个 宽 品种 的 数据 缓冲 需要,

包括 高速 数据 收购, 多处理机 国际米兰-

面, 和 通信 缓冲.

这些 fifos 有 9-有点 输入 和 输出 端口 那 是

受控 由 分开 时钟 和 启用 信号. 这 输入 港口

是 受控 由 一个 自由运行 时钟 (wclk) 和 两个

写启用 针脚 (wen1

, wen2/ld).

当 wen1

是 低 和 wen2/ld是 高, 数据 是 书面

进入 这 先进先出 开启 这 上升边缘 的 这 wclk 信号. 同时

WEN1

, wen2/ld是 持有 活动, 数据 是 不断地 书面 进入

这 先进先出 开启 每个 wclk 循环. 这 输出 港口 是 受控 入点

一个 类似 方式 由 一个 自由运行 阅读 时钟 (rclk) 和 两个

读取-启用 针脚 (ren1

, ren2). 入点 加法, 这 cy7c42x1

有 一个 输出 启用 管脚 (oe

). 这 阅读 (rclk) 和 写

(wclk) 时钟 将 是 系紧 toget她的 用于 单时钟 操作

或 这 两个 时钟 将 是 运行 独立 用于 异步

阅读/写 应用程序. 时钟 频率 向上 至 100 mhz 是

可实现的.

深度 扩展 是 可能 使用 一个 启用 输入 用于 系统

控制, 同时 这 其他 启用 是 受控 由 扩展 逻辑

至 直接 这 流量 的 数据.

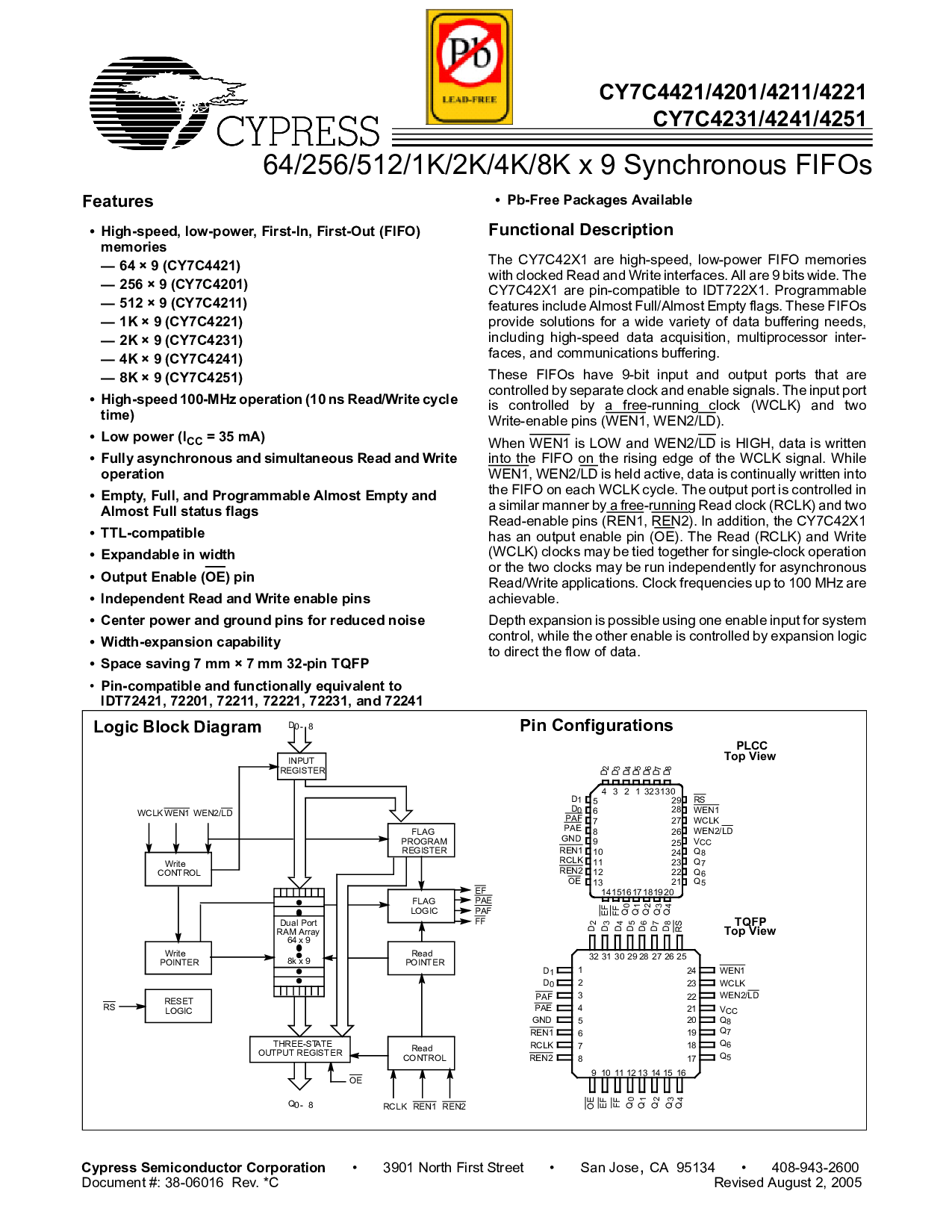

逻辑 块 图表

管脚

c开启fIgurig饰

三态

输出 注册

阅读

控制

旗子

逻辑

写

控制

写

指针

阅读

指针

重置

逻辑

输入

注册

旗子

程序

注册

d

0- 8

rclk

ef

PAE

PAF

q

0- 8

WEN1

WCLK

rs

oe

双 港口

ram 阵列

64 x 9

8k x

9

wen2/ld

REN1 REN2

ff

d

8

d

7

d

6

d

5

d

4

d

3

d

2

1

2

3

4

5

6

7

8

d

1

d

0

rclk

地

PAF

PAE

REN1

REN2

17

18

19

20

21

22

23

24

14 15 16910111213

31 3032 29 28 27 2526

ff

q

0

q

1

q

2

q

3

q

4

ef

oe

v

抄送

WCLK

wen2/ld

q

8

q

7

q

6

q

5

WEN1

rs

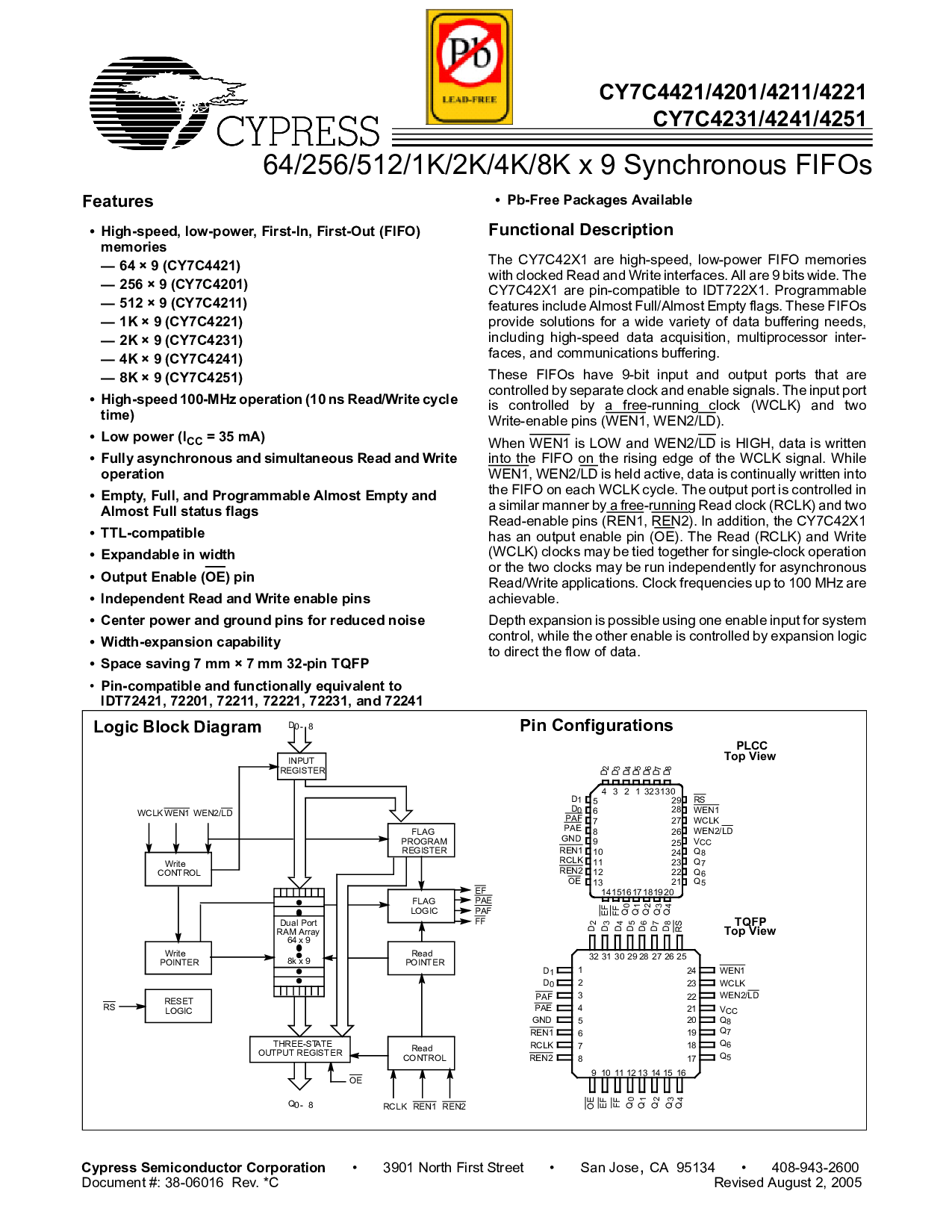

TQFP

顶部 查看

PLCC

d

1

d

0

rclk

v

抄送

d

8

d

7

d

6

d

5

d

4

d

3

地

WCLK

wen2/ld

q

8

q

7

d

2

PAF

PAE

5

6

7

8

9

10

11

12

13

REN1

oe

REN2

4 3 2 1 313032

21

22

23

24

27

28

29

25

26

14151617181920

q

6

q

5

WEN1

rs

ff

q

0

q

1

q

2

q

3

q

4

ef

顶部 查看

cy7c4421/4201/4211/4221

cy7c4231/4241/425164/256/512/1k/2k/4k/8k x 9 同步 fifos