初步

36-mbit ddr-二 sram 4-字

突发 体系结构

CY7C1417AV18

CY7C1428AV18

CY7C1419AV18

CY7C1421AV18

柏树 半导体 公司

• 198 champion court • San Jose

,

ca 95134-1709 • 408-943-2600

文件 号码: 38-05618 rev. *c 修订 12月 12, 2005

特点

• 36-mbit 密度 (4m x 8, 4m x 9, 2m x 18, 1m x 36)

• 300-mhz 时钟 用于 高 带宽

• 4-字 突发 用于 减少 地址 总线 频率

• 双 数据 费率 (ddr) 接口

(数据 已转移 在 600 mhz) @ 300 mhz

• 两个 输入 时钟 (k 和 k

) 用于 精确 ddr 计时

— sram 用途 上升 边缘 仅

• 两个 输入 时钟 用于输出 数据 (c 和 c

) 至 最小化

时钟-偏斜 一个d 飞行-时间 不匹配

• 回声 时钟 (cq 和 cq

) 简化 数据捕获 入点

高速 系统

• 同步 内部 自定时 写入

• 1.8v 核心 电源 供应 与 hstl 输入 和 产出

• 变量 驱动器 hstl 输出 缓冲区

• 展开 hstl 输出 电压 (1.4v–v

dd

)

• 可用 入点 165-球 fbga 包装 (15 x 17 x 1.4 mm)

• 提供 入点 两者都有 无铅 和 非 无铅 软件包

• jtag 1149.1 兼容 测试一下 访问权限 港口

• 延迟 锁 回路 (dll) 用于 准确 数据 放置位置

配置

cy7c1417av18 – 4m x 8

cy7c1428av18 – 4m x 9

cy7c1419av18 – 2m x 18

cy7c1421av18 – 1m x 36

功能 描述

这 cy7c1417av18, cy7c1428av18, cy7c1419av18, 和

cy7c1421av18 是 1.8v 同步 流水线 sram

配备 与 ddr-二 (双 数据 费率) 体系结构. 这

ddr-二 由 的 一个 sram 核心 与 高级 同步

外围设备 电路 和 一个 两位 突发 计数器. 地址 用于

阅读 和 写 是 锁定 开启 备用 上升 边缘 的 这

输入 (k) 时钟. 写 数据 是 已注册 开启 这 上升 边缘 的

两者都有 k 和 k

. 阅读 数据 是 驱动 开启 这 上升 边缘 的 c 和

c

如果 提供, 或 开启 这 上升 边缘 的 k 和 k如果 c/c是 不

提供. 每个 地址 位置 是 关联的 与 四 8-有点

字词 入点 这 案例 的 cy7c1417av18 和 四 9-有点 字词 入点

这 案例 的 cy7c1428av18 那突发 按顺序 进入 或 出点

的 这 设备. 这 突发 counte右 总是 开始 与 “00” 国际米兰-

纳利 入点 这 案例 的 cy7c1417av18 和 cy7c1421av18. 开启

cy7c1428av18 和 cy7c1419av18, 这 突发 计数器 需要

入点 这 最后一个 两个 重大 比特 的 这 外部 地址 和

突发 四 18-有点 字词 入点 这 案例 的 cy7c1428av18, 和

四 36-有点 字词 入点 这 案例 的 cy7c1419av18, 按顺序

进入 或 出点 的 这 设备.

异步 输入 包括 输出 阻抗 匹配

输入 (zq). 同步 数据产出 (q, 共享 这 相同

物理 针脚 作为 这 数据 输入, d) 是 紧紧地 匹配 至 这

两个 输出 回声 时钟 cq/cq

, 消除 这 需要 用于

单独 捕获 数据 从 每个 个人 ddr-二 sram

入点 这 系统 设计. output 数据 时钟 (c/c) 启用

最大值 系统 时钟 和 da助教 同步 灵活性.

全部 同步 输入 通过 通过 输入 寄存器 受控

由 这 k 或 k

输入 时钟. 全部 数据 产出 通过 通过 输出

寄存器 受控 由 这 c 或 c

(或 k 或 k入点 一个 单独 时钟

域) 输入 时钟. 写入 是 进行 与 片上

同步 自定时 写 电路.

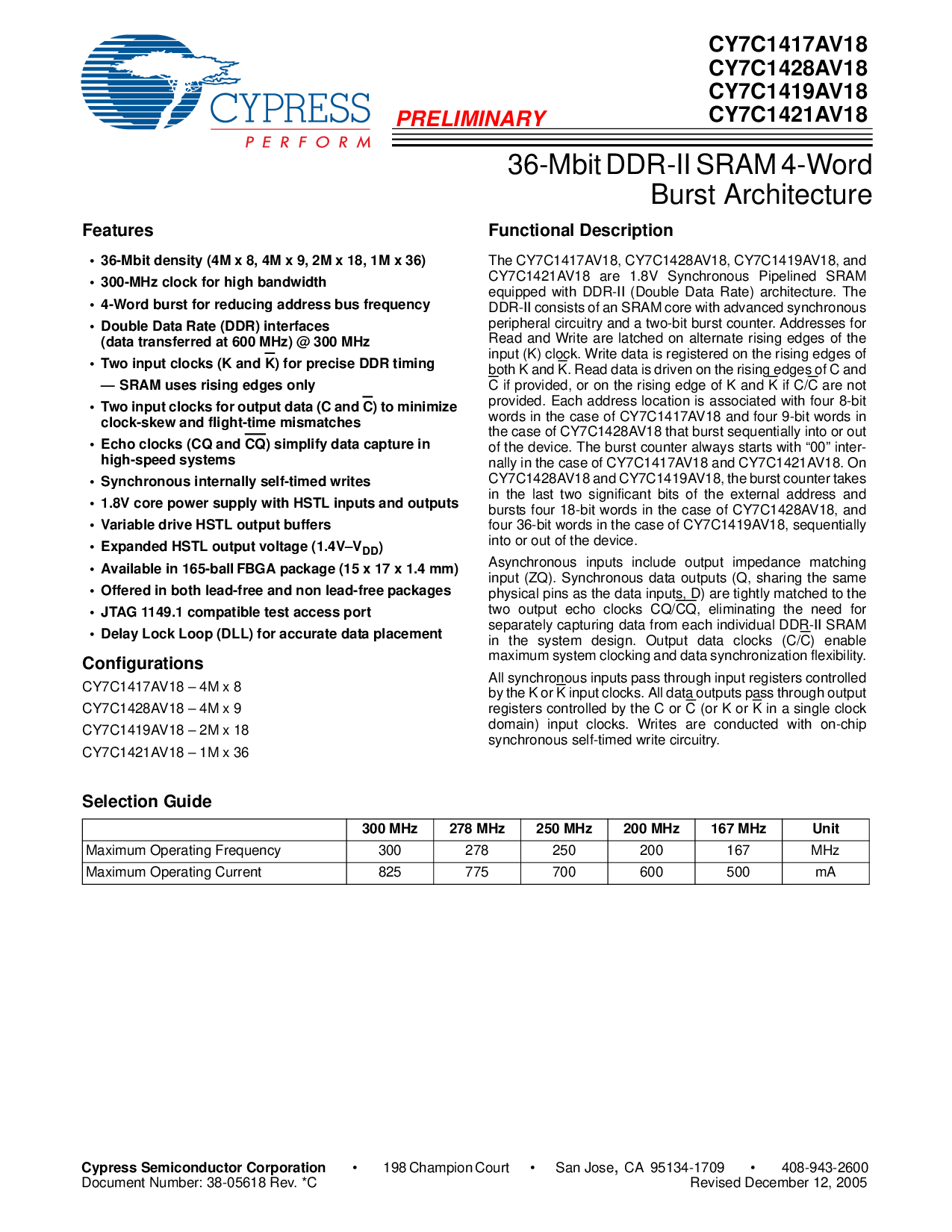

选择 指南

300 mhz 278 mhz 250 mhz 200 mhz 167 mhz 单位

最大值 操作 频率 300 278 250 200 167 MHz

最大值 操作 电流 825 775 700 600 500 ma