2.5/3.3v 200-mhz 多输出 零 延迟 缓冲区

CY2V9950

柏树 半导体 公司

• 3901 北 第一 街道 • San Jose

,

ca 95134 • 408-943-2600

文件 #: 38-07436 rev. *a 修订 8月 11, 2004

特点

• 2.5v 或 3.3v 操作

• 拆分 输出 银行 电源 供应品

• 输出 频率 范围: 6 mhz 至 200 mhz

• 输出-输出 偏斜 &指示灯; 150 ps

• 循环-循环 抖动 &指示灯; 100 ps

• 可选择 正 或 内加活动 边缘 同步

• 可选择 锁相 回路 (pll) 频率 范围

•

8 lvttl 产出 驾驶 50

Ω

已终止 线条

• lvcmos/lvttl 过电压 宽容 参考 输入

• 2x, 4x 相乘 和 (1/2)x, (1/4)x 除法 比率

• 传播-光谱-兼容

• 引脚兼容 与 idt5v9950 和 idt5t9950

• 工业 温度 范围: –40

°

c 至 +85

°

c

• 32-管脚 tqfp 包装

功能 描述

这 cy2v9950 是 一个 低-电压,低-电源, 八-输出,

200-mhz 时钟 驾驶员. 它 壮举操作系统 功能 必要的 至

优化 这 计时 的 高 业绩 计算机 和

通信 系统.

这 用户 可以 程序 这 输出 银行 通过 3f[0:1] 和

4f[0:1]pins. 任何 一个 的 这 产出 可以 是 已连接 至

反馈 输入 至 实现 不同的 参考 频率 多-

折叠 和 除法 比率 和 零 输入-输出 延迟.

这 设备 也 特点 拆分输出 银行 电源 供应品

哪个 启用 这 用户 至 运行 two 银行 (1qn 和 2qn) 在 一个

电源 供应 水平 不同的 右前om 那 的 t他 其他 两个 银行

(3qn 和 4qn). 另外, 这 pe 管脚 控件 这 同步-

N化 的 这 输出 信号 至 要么 这 上升 或 这 坠落

边缘 的 这 参考 时钟.

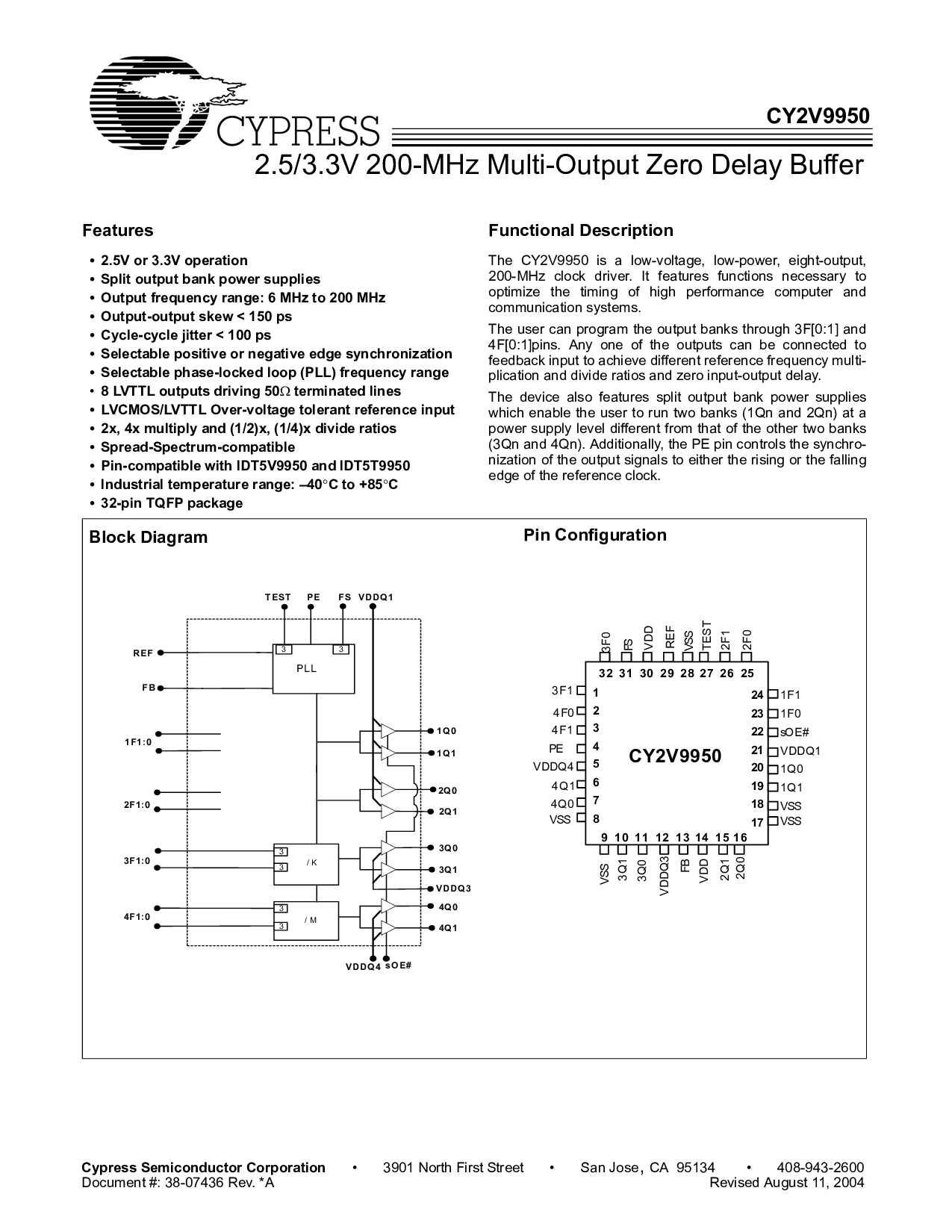

块 图表

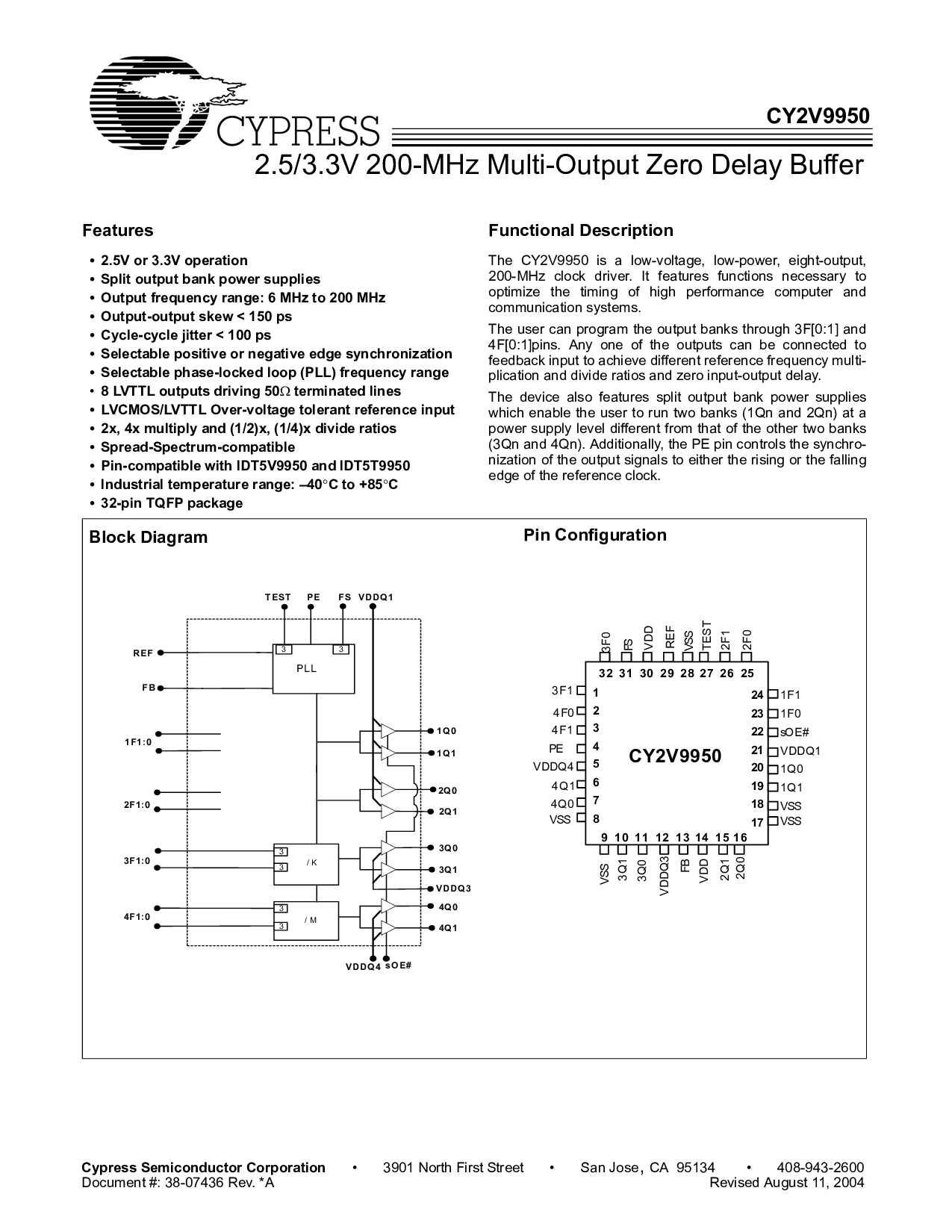

管脚 配置

3F0

fs

VDD

参考

vss

测试一下

2F1

2F0

CY2V9950

3231302928 272625

910111213 141516

24

23

22

21

20

19

18

17

1

2

3

4

5

6

7

8

1F1

1F0

所以 e? #

VDDQ1

1Q0

1Q1

vss

vss

3F1

4F0

4F1

pe

VDDQ4

4Q0

vss

4Q1

vss

3Q1

3Q0

VDDQ3

2Q1

fb

VDD

2Q0

pe测试一下 fs

33

参考

fb

2f1:0

1f1:0

3f1:0

4f1:0

1Q0

1Q1

2Q0

2Q1

3Q0

3Q1

4Q0

4Q1

PLL

3

3

3

3

/ k

sOE#

VDDQ1

VDDQ4

/ m

VDDQ3