差速器 时钟 缓冲区/驱动器右

CY2SSTV855

柏树 半导体 公司

• 198 champion court • San Jose

,

ca 95134-1709 • 408-943-2600

文件 #: 38-07459 rev. *e 修订 october 5, 2005

特点

• 锁相 回路 (pll) clock 分布 用于 双

数据 费率 同步 dram 应用程序

• 1:5 差速器 产出

• 外部 反馈 针脚 (fbint, fbinc) 是 已使用 至

同步 这 产出 至 这 时钟 输入

• sscg: 传播 aware™ 用于 电磁

干扰 (e?mi) 减少

• 28-管脚 tssop 包装

• 符合 至 电子元件工业联合会 ddr 规格

功能 描述

这 cy2sstv855 是 一个 高-业绩, 很-低-偏斜,

很-低-抖动 零-延迟 缓冲区 那 分发 一个 差速器

时钟 输入 对 (sstl_2) 至 四 差速器 (sstl_2) 对 的

时钟 产出 和 一个 差速器 对 的 反馈 时钟

产出. 入点 支持 的 低 电源 要求, 当

掉电 是 高, 这 产出 开关 入点 相位 和

频率 与 这 输入 时钟. 当 掉电 是 低, 全部

产出 是 已禁用 至 一个 高阻抗 州 和 这 pll 是

关闭 向下.

这 设备 支架 一个 低频 掉电 模式.

当 这 输入 是 &指示灯; 20 mhz, 这 pll 是 已禁用 和 这

产出 是 put 入点 这 嗨-z 州. 当 这 输入 频率 是

> 20 mhz, 这 pll 和 产出 是 已启用.

当 avdd 是 系紧 至 接地, 这 pll 是 翻转 关 和

旁路 与 这 输入 参考 时钟 门控 至 这 产出.

这 柏树 cy2sstv855 是 传播 意识到 和 支架

间距 的 传播 光谱 时钟 输入 至 减少 emi

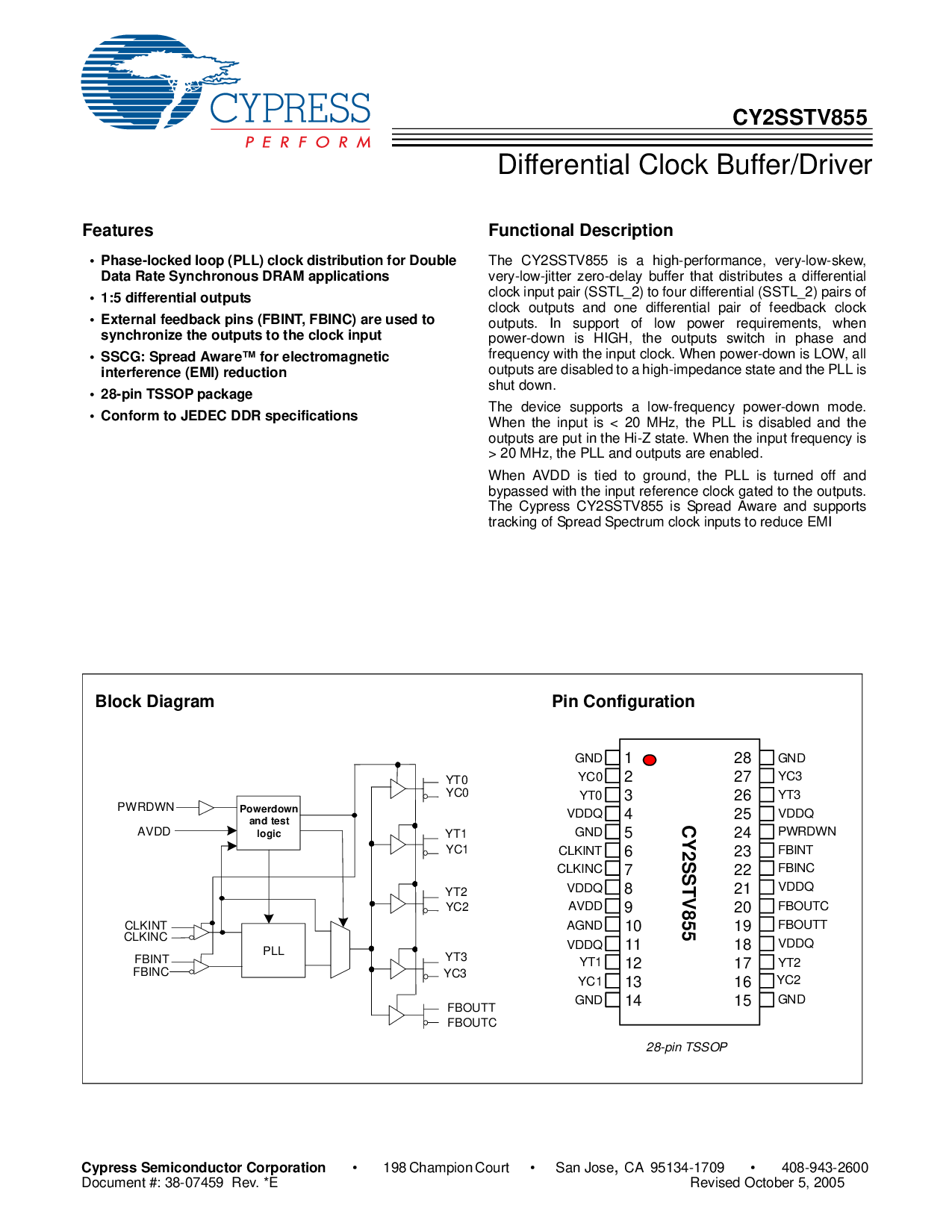

块 图表

管脚 配置

28-管脚 tssop

1

2

3

4

5

6

7

8

9

10

11

12

13

14

28

27

26

25

24

23

22

21

20

19

18

17

16

15

地

YT3

VDDQ

FBOUTT

YT2

YC2

地

VDDQ

FBOUTC

YC3

VDDQ

PWRDWN

FBINT

FBINC

地

YT0

VDDQ

AGND

YT1

YC1

地

VDDQ

AVDD

YC0

VDDQ

地

CLKINT

CLKINC

CY2SSTV855

FBOUTT

FBOUTC

YT0

YC0

YC3

YT3

PLL

PWRDWN

YC2

YT2

YT1

YC1

断电

和 测试一下

逻辑

AVDD

CLKINT

CLKINC

FBINT

FBINC