差速器 时钟 缓冲区/驾驶员

CY2SSTV8575

柏树 半导体 公司

• 3901 北 第一 街道 • San Jose • ca 95134 • 408-943-2600

文件 #: 38-07458 rev. ** 修订 october 30, 2002

TV8575

特点

• 操作 频率: 60 mhz 至 170 mhz

• 支架 266-mhz ddr sdram

• 5 差速器 产出 从 1 差速器 输入

• 传播 光谱 兼容

• 低 抖动 (循环-至-循环): &指示灯; 75

• 很 低 偏斜: &指示灯; 100 ps

• 电源 管理 控制 输入

• 高阻抗 产出 当 输入 时钟 &指示灯; 20 mhz

• 2.5v 操作

• 32-管脚 tqfp 电子元件工业联合会 ms-026 c

描述

这 cy2sstv8575 是 一个 高-业绩, 低-偏斜, 低 抖动

零-延迟 缓冲区 设计 至 分发 差速器 时钟 入点

高速 应用程序. 这 cy2sstv8575 生成 五个

差速器 对 时钟 产出 从 一个 差速器 对 时钟

输入. 入点 加法, 这 cy2sstv8575 特点 差速器

反馈 时钟 产出 和 输入. 这个 允许 这

cy2sstv8575 至 是 已使用 作为 一个 零-延迟 缓冲区.

当 已使用 作为 一个 零-延迟 缓冲区 入点 嵌套 时钟 树木, 这

cy2sstv8575 锁 上 这 输入 参考 和 翻译

与 近 零 延迟 至 低偏斜 产出.

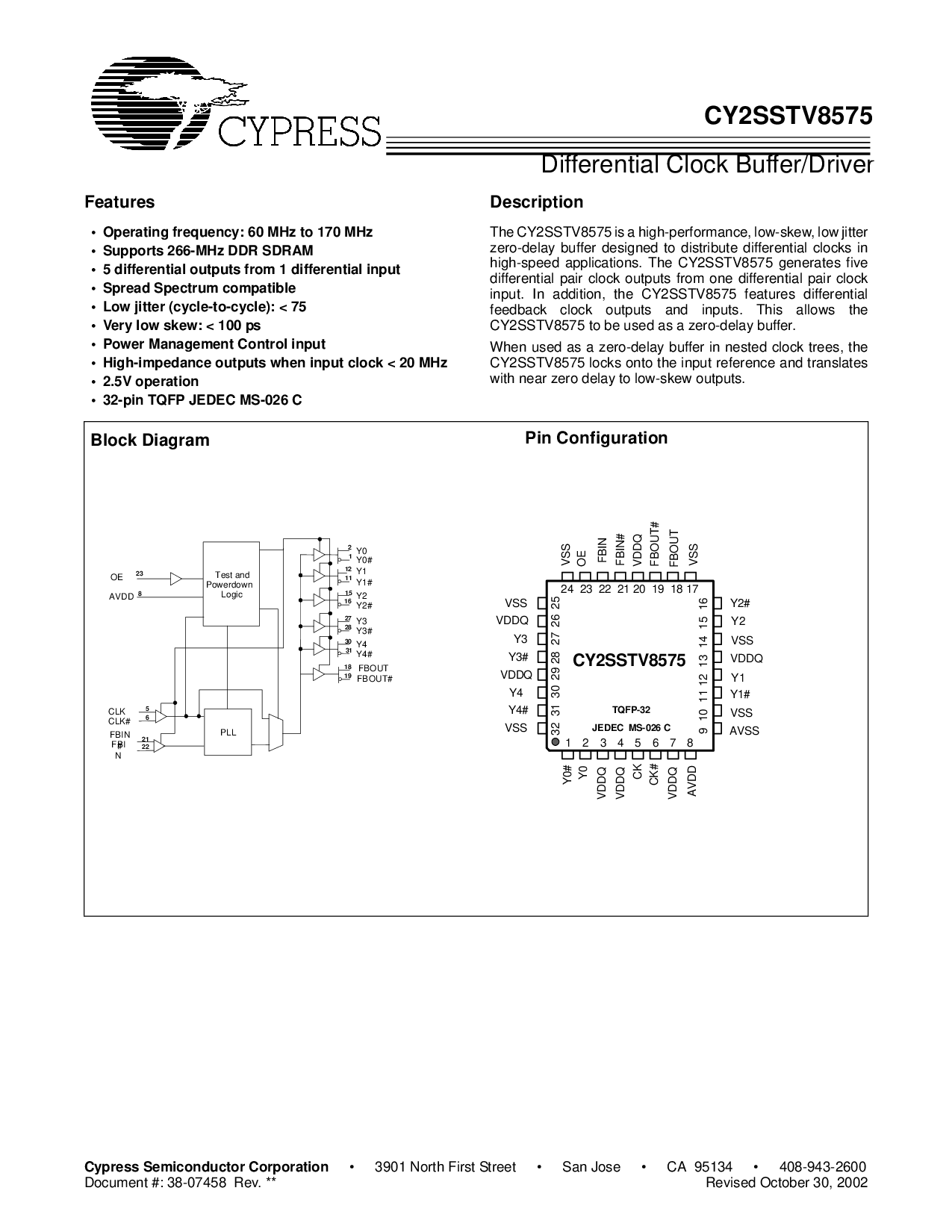

块 图表

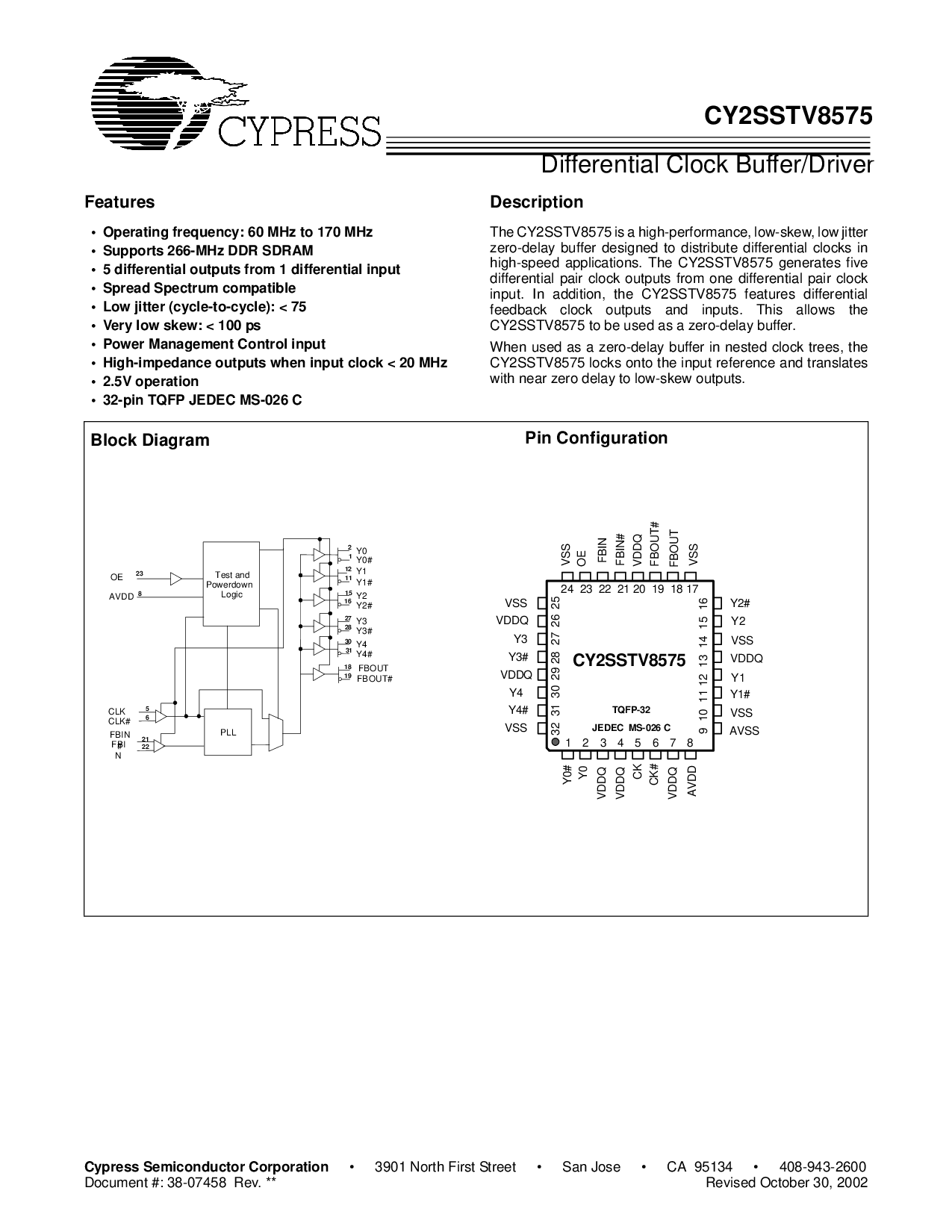

管脚 配置

16

2

1

12

11

15

27

28

30

31

18

19

测试一下 和

断电

逻辑

PLL

5

6

21

22

FBI

n

FBIN

#

clk

CLK#

AVDD

23

8

oe

Y0

Y0#

Y1

Y1#

Y2

Y2#

Y3

Y3#

Y4

Y4#

FBOUT

FBOUT#

tqfp-32

电子元件工业联合会 ms-026 c

Y2#

Y2

vss

VDDQ

Y1

Y1#

vss

AVSS

Y0#

Y0

VDDQ

ck

CK#

AVDD

VDDQ

VDDQ

VDDQ

vss

Y4#

Y4

Y3#

Y3

VDDQ

vss

vss

oe

FBIN

VDDQ

FBOUT#

vss

FBIN#

FBOUT

CY2SSTV8575

12345678

9 10 11 12 13 14 15 16

24 23 22 21 20 19 18 17

32 31

30

29 28 27

26

25