14-有点 已注册 布菲右

pc2700-/pc3200-符合

CY2SSTV16857

柏树 半导体 公司

• 3901 北 第一 街道 • San Jose

,

ca 95134 • 408-943-2600

文件 #: 38-07443 rev. *d 修订 january 12, 2005

特点

• 差速器 时钟 输入 向上 至 280 mhz

• 支架 lvttl 开关g 级别 开启 这 重置

管脚

• 输出 驱动程序 有 受控 边缘 费率, 所以 否

外部 电阻 是 必填项

• 两个 kv esd 保护

• 闩锁 业绩 超过 100 ma: jesd78, 类 二

• 符合 至 电子元件工业联合会 标准 (jesd82-3) 用于 缓冲 ddr

DIMMs

• 48-管脚 tssop

描述

这个 14-有点 已注册 缓冲区 是 设计 具体而言 用于 2.3v 至

2.7v v

dd

操作 和 是 表征 用于 操作 从

0°c 至 + 85°c.

全部 输入 是 兼容 与 这 电子元件工业联合会 标准 用于

sstl_2, 除了 这 lvcmos 重置 (重置

) 输入. 全部 产出

是 sstl_2, 类 二-兼容.

这 sstv16857 操作 从 一个 差速器 时钟 (clk 和

clk

). 数据 是 已测量 在 这穿越 的 clk 继续 高,

和 clk

继续 低.

当 重置是 低, 这 差速器 输入 接收器 是

已禁用, 和 未驱动 (floating) 数据, 时钟, 和 参考 电压

输入 是 允许. 入点 加法, 当 重置

是 低, 全部

寄存器 是 重置 和 全部 产出 力 至 这 低 州. 这

lvcmos 重置输入 必须 总是 是 持有 在 一个 有效 逻辑

高 或 低 水平.

至 确保 已定义 产出 从这 注册 之前 一个 稳定

时钟 有 被 提供的, 重置 必须 是 持有 入点 这 低

州 期间 电源-向上.

入点 这 ddr 已注册dimm 应用程序, 重置

是 指定

至 是 完全 异步 与 尊重 至 clk 和 clk

.

因此, 否 计时 关系 可以 是 保证 之间

这 两个. 当 进入 重置,这 注册 将 是 已清除 和

这 产出 将 是 驱动 低 快速, 相对 至 这 时间 至

禁用 这 差速器 输入接收器, 因此 确保 否

故障 开启 这 输出. 然而,当 即将到来 出点 的 重置, 这

注册 将 成为 活动 快速, 相对 至 这 时间 至

启用 这 差速器 输入 接收器. 作为 长 作为 这 数据

输入 是 低, 和 这 时钟 是 稳定 期间 这 时间 从 这

从低到高 trans活动 的 重置

直到 这 输入 接收器 是

完全 已启用, 这 设计 必须确保 那 这 产出 将

保持 低.

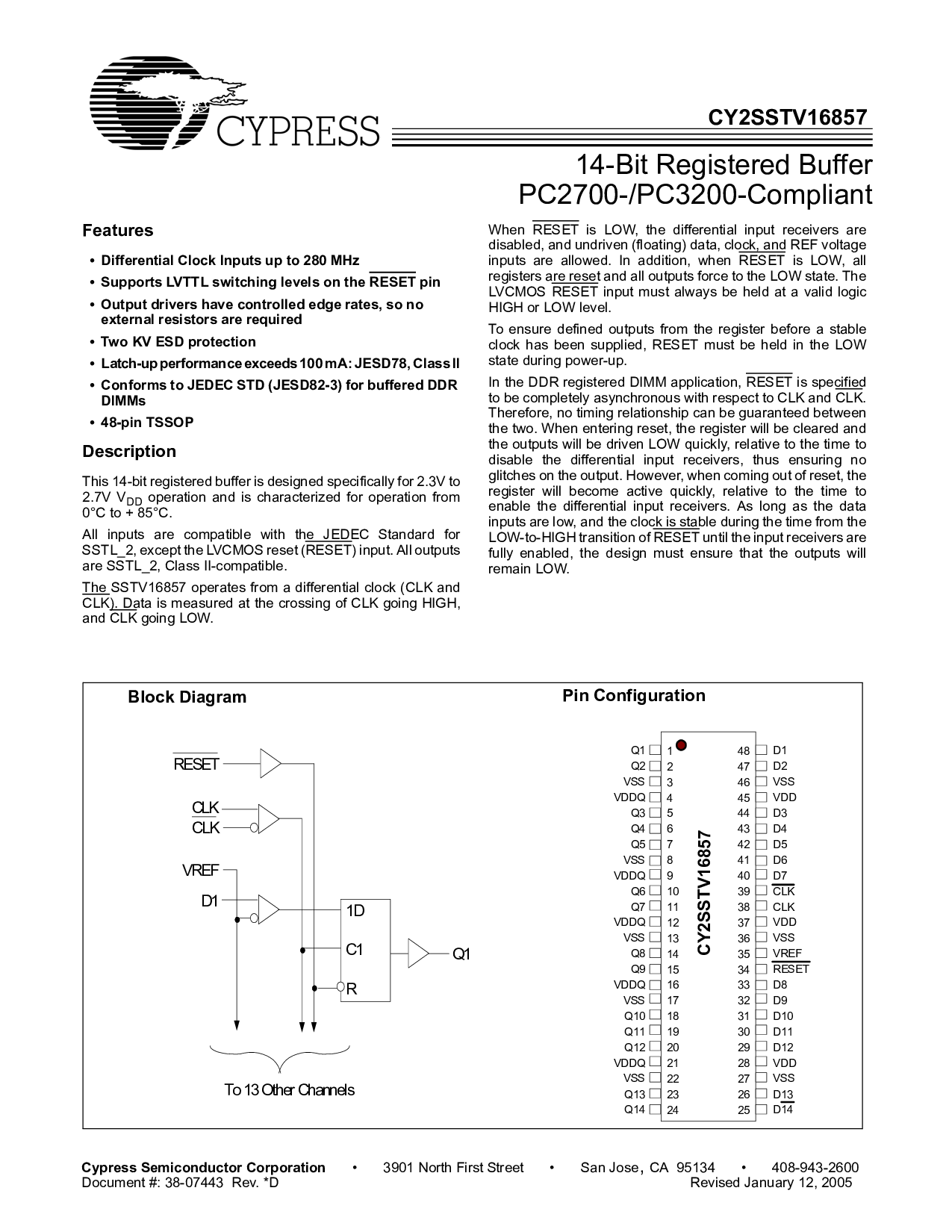

块 图表

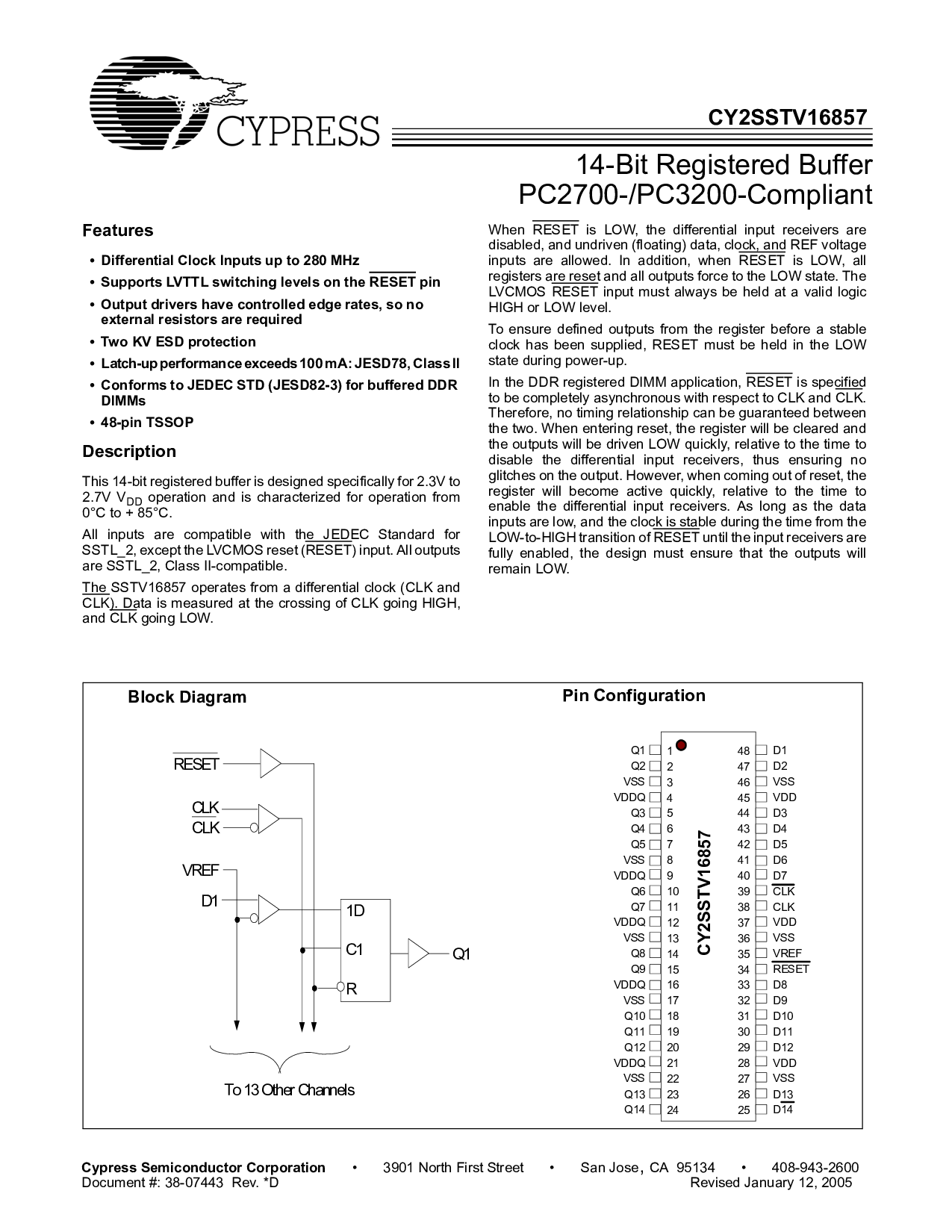

管脚 配置

1D

C1

右

重置

clk

clk

VREF

D1

Q1

至 13 ot她的频道s

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

Q1

Q2

vss

VDDQ

Q3

Q4

Q5

vss

VDDQ

Q6

Q7

VDDQ

vss

Q8

Q9

VDDQ

vss

Q10

Q11

Q12

VDDQ

vss

Q13

Q14

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

D1

D2

vss

VDD

D3

D4

D5

D6

D7

clk

clk

VDD

vss

VREF

重置

D8

D9

D10

D11

D12

VDD

vss

D13

D14

CY2SSTV16857