初步

1.8v, 500-mhz, 10-输出 电子元件工业联合会-符合

零 dela

y布菲右

CY2SSTU877

柏树 半导体 公司

• 198 champion court • San Jose

,

ca 95134-1709 • 408-943-2600

文件 #: 38-07575 rev. *e 修订 january 27, 2006

特点

• 操作 频率: 125 mhz 至 500 mhz

• 支架 ddrii sdram

• 1 至 10 差速器时钟 缓冲区 (sstl_18)

• 传播-光谱-兼容

• 低 抖动 (循环-至-循环): 40 ps

• 很 低 输出到输出 偏斜: 40 ps

• 自动 掉电 功能 当 输入 是 低

• 1.8v 操作

• 完全 电子元件工业联合会-符合 (jesd 82-8)

• 52-球 bga

功能 描述

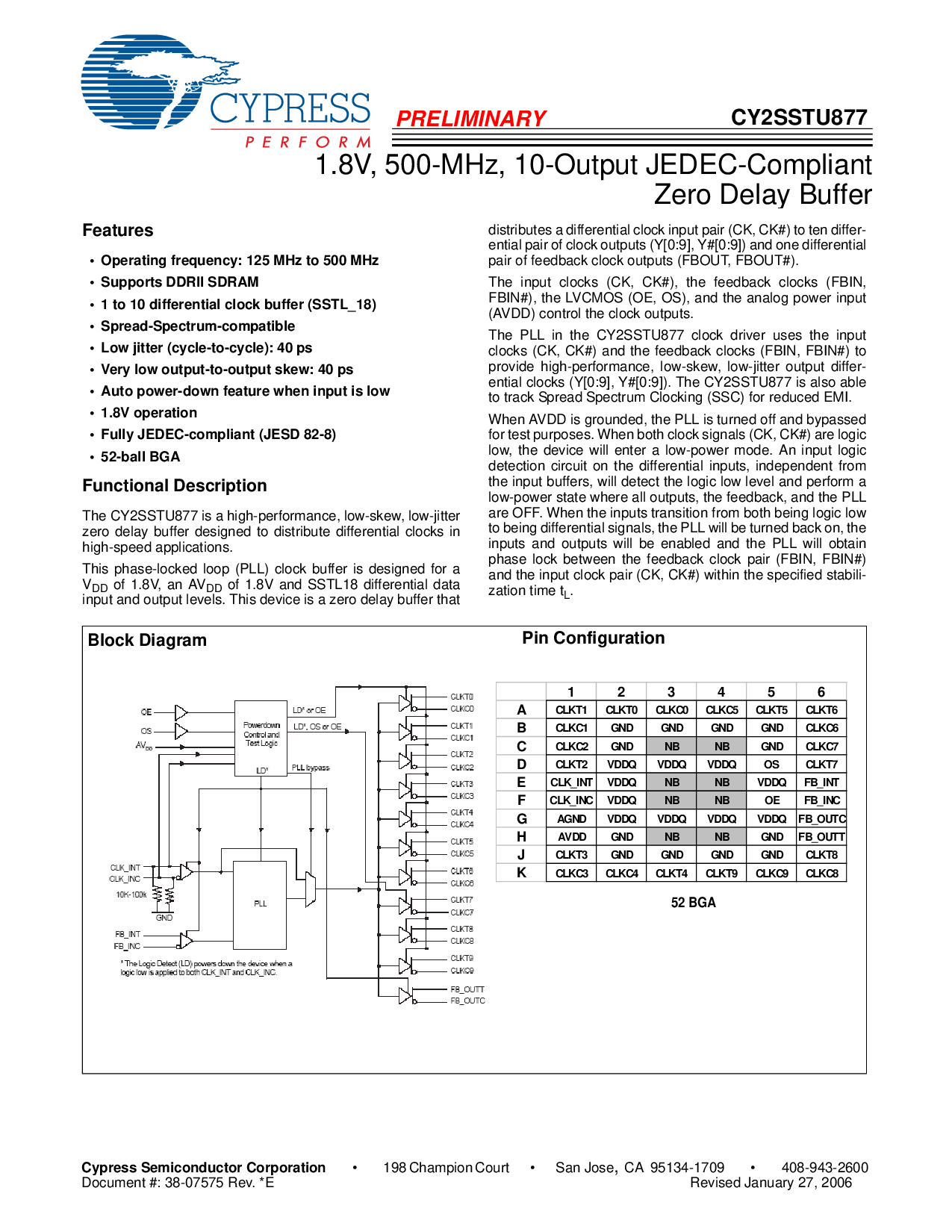

这 cy2sstu877 是 一个 高-业绩, 低-偏斜, 低抖动

零 延迟 缓冲区 设计 至分发 差速器 时钟 入点

高速 应用程序.

这个 锁相 回路 (pll) 时钟 缓冲区 是 设计 用于 一个

v

dd

的 1.8v, 一个 av

dd

的 1.8v 和 sstl18 差速器 数据

输入 和 输出 级别. 这个 设备 是 一个 零 延迟 缓冲区 那

分发 一个 差速器 时钟 输入对 (ck, ck#) 至 十 不同-

电位 对 的 时钟 产出 (y[0:9], y#[0:9]) 和 一个 差速器

对 的 反馈 时钟 产出 (fbout, fbout#).

这 输入 时钟 (ck, ck#), 这 反馈 时钟 (fbin,

fbin#), 这 lvcmos (oe, 操作系统), 和 这 模拟 电源 输入

(avdd) 控制 这 时钟 产出.

这 pll 入点 这 cy2sstu877 时钟 驾驶员 用途 这 输入

时钟 (ck, ck#) 和 这 feedback 时钟 (fbin, fbin#) 至

提供 高-业绩, 低-偏斜, 低抖动 输出 不同-

电位 时钟 (y[0:9], y#[0:9]). 这 cy2sstu877 是 也 能

至 轨道 传播 光谱 时钟 (ssc) 用于 减少 emi.

当 avdd 是 接地, 这 pll 是 翻转 关 和 旁路

用于 测试一下 目的. 当 两者都有 时钟 信号 (ck, ck#) 是 逻辑

低, 这 设备 将 输入 一个 低功耗 模式. 一个 输入 逻辑

检测 电路 开启 这 差速器 输入, 独立 从

这 输入 缓冲区, 将 检测 这 逻辑 低 水平 和 执行 一个

低功耗 州 在哪里 全部 出点看跌期权, 这 反馈, 和 这 pll

是 关. 当 这 输入 过渡 从 两者都有 正在 逻辑 低

至 正在 差速器 信号, 这 pll 将 是 翻转 背面 开启, 这

输入 和 产出 将 是 已启用 和 这 pll 将 获取

相位 锁 之间 这 反馈 时钟 对 (fbin, fbin#)

和 这 输入 时钟 对 (ck, ck#) 内 这 指定 stabili-

化 时间 t

l

.

块 图表

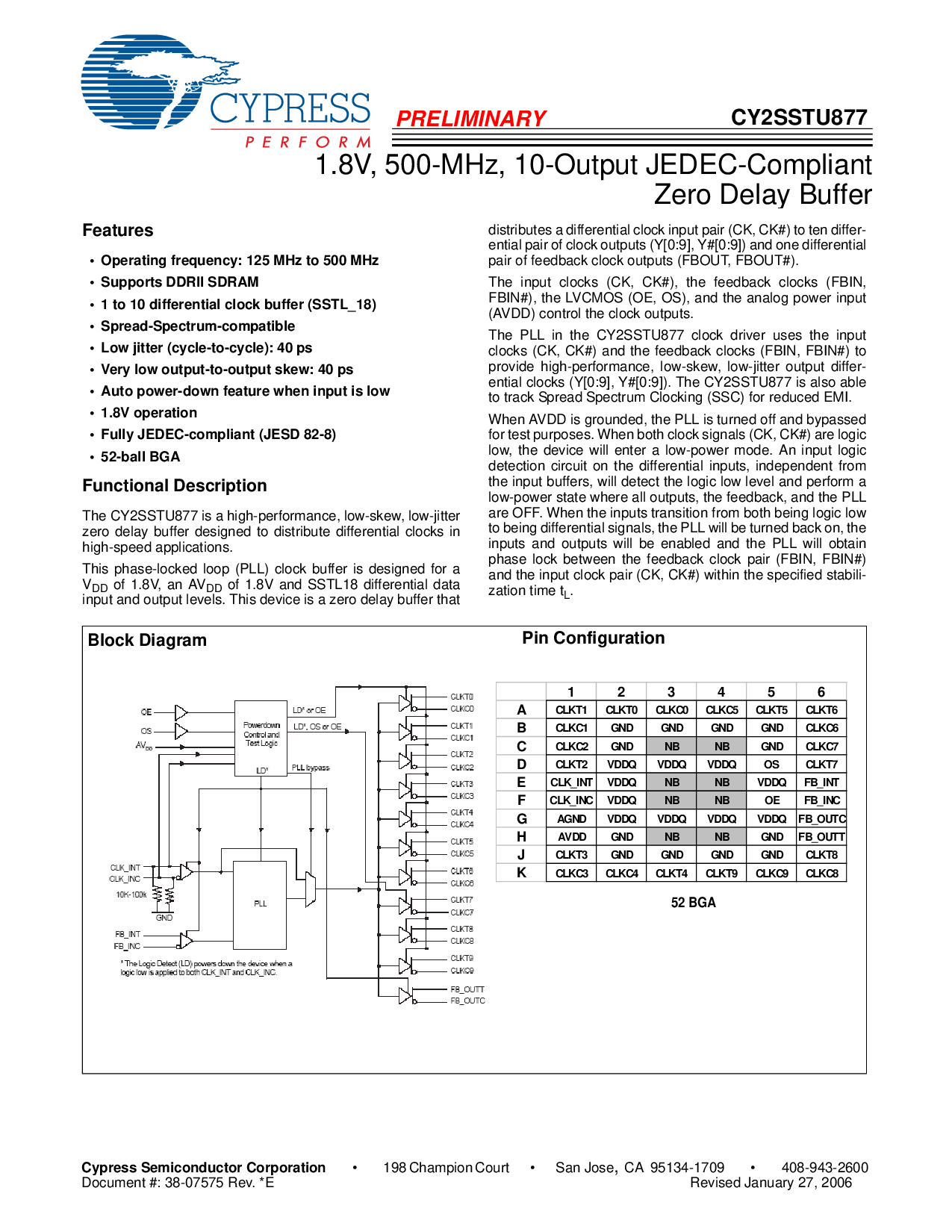

管脚 配置

52 bga

123456

一个

CLKT1 CLKT0 CLKC0 CLKC5 CLKT5 CLKT6

B

CLKC1 地 地 地 地 CLKC6

c

CLKC2 地 nb nb 地 CLKC7

d

CLKT2 VDDQ VDDQ VDDQ 操作系统 CLKT7

e?

clk_我nt VDDQ nb nb VDDQ fb_我nt

f

clk_我nc VDDQ nb nb oe fb_我nc

g

AGND VDDQ VDDQ vDDQ VDDQ fb_outc

h

AVDD 地 nb nb 地 fb_outt

j

CLKT3 地 地 地 地 CLKT8

k

CLKC3 CLKC4 CLKT4 CLKT9 CLKC9 CLKC8