双 1:10 差速器 cl锁定/数据 扇出 布菲右

fastedge™ 系列

CY2PP3220

柏树 半导体 公司

• 3901 北 第一 街道 • San Jose

,

ca 95134 • 408-943-2600

文件 #: 38-07513 rev.*c 修订 july 28, 2004

特点

• 两个 集 的 十 ecl/pecl 差速器 产出

• 两个 ecl/pecl 差速器 输入

• 热-可交换/-insertable

• 50 ps 输出到输出 偏斜

• 150 ps 设备到设备 偏斜

• 500 ps 传播 延迟 (典型)

• 1.5 ghz 操作 (2.7 ghz 最大值 切换 频率)

• pecl 模式 供应 范围: v

抄送

= 2.5v± 5% 至 3.3v±5%

与 v

ee

= 0v

• ecl 模式 供应 范围: v

e? e?

= –2.5v± 5% 至 –3.3v±5%

与 v

抄送

= 0v

• 工业 温度 范围: –40°c 至 85°c

• 52-管脚 1.4-mm tqfp 包装

• 温度 补偿 喜欢 100k ecl

• 管脚 兼容 与 mc100es6220

功能 描述

这 cy2pp3220 是 一个 低-偏斜, 低 传播 延迟 双

1-至-10 差速器 扇出 缓冲区 有针对性的 至 满足 这 需要-

部分 的 高性能 时钟 和 数据 分布 应用程序-

区域. 这 设备 是 已实施 开启 sige 技术 和 有

一个 完全 差速器 内部 architecture 那 是 优化 至

实现 低 信号 偏斜 在 操作正在处理 频率 的 向上 至 1.5

ghz.

这 设备 特点 两个 差速器 输入 路径 那 是 不同-

电位 内部. 这 cy2pp3220 将 功能 不 仅 作为 一个

差速器 时钟 缓冲区 但是 也 作为 一个 信号电平 翻译器 和

扇出 开启 ecl/pecl 信号 至 二十 ecl/pecl 差速器

荷载. 一个 外部 偏差 管脚, vbb, 是 提供 用于 这个 目的.

入点 这样的 一个 应用程序, 这 vbb 管脚 应该 是 已连接 至

要么 一个 的 这 clka# 或 clkb# 输入 和 旁路 至

接地 通过 一个 0.01-

µ

f 电容器. 传统上, 入点 ecl, 它 是 已使用

至 提供 这 参考 水平 至 一个 收货 单端 输入

那 可能 有 一个 不同的 自偏 点.

自 这 cy2pp3220 介绍 可忽略不计 抖动 至 这 计时

预算, 它 是 这 理想 选择用于 分发 高 频率,

高 精度 时钟 跨越 背面-飞机 和 板 入点 com-

通信 系统.此外, 高级 电路 设计

方案, 这样的 作为 内部 te温度 compens位置, 确保

那 这 cy2pp3220 交付 一致 业绩 结束

各种 platforms.

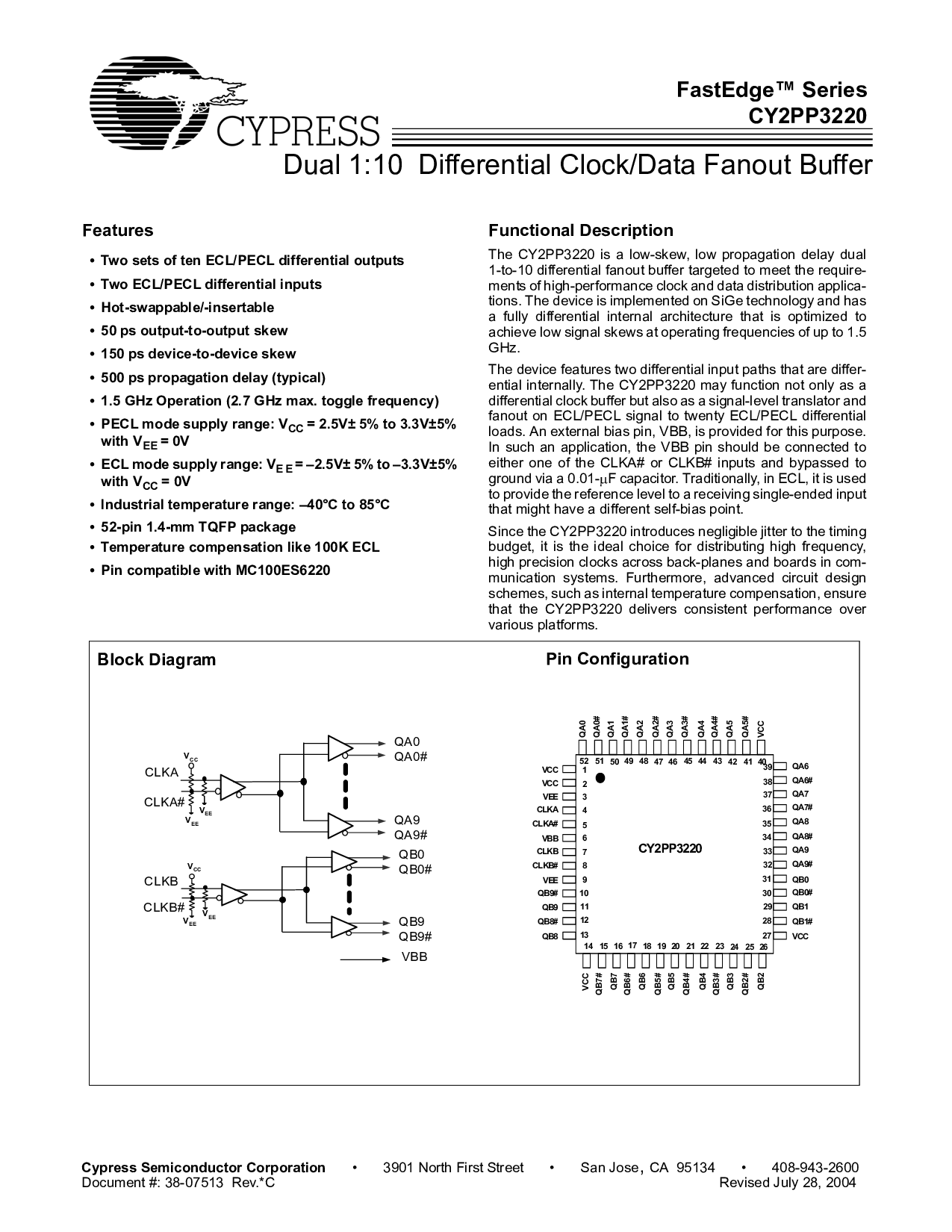

块 图表

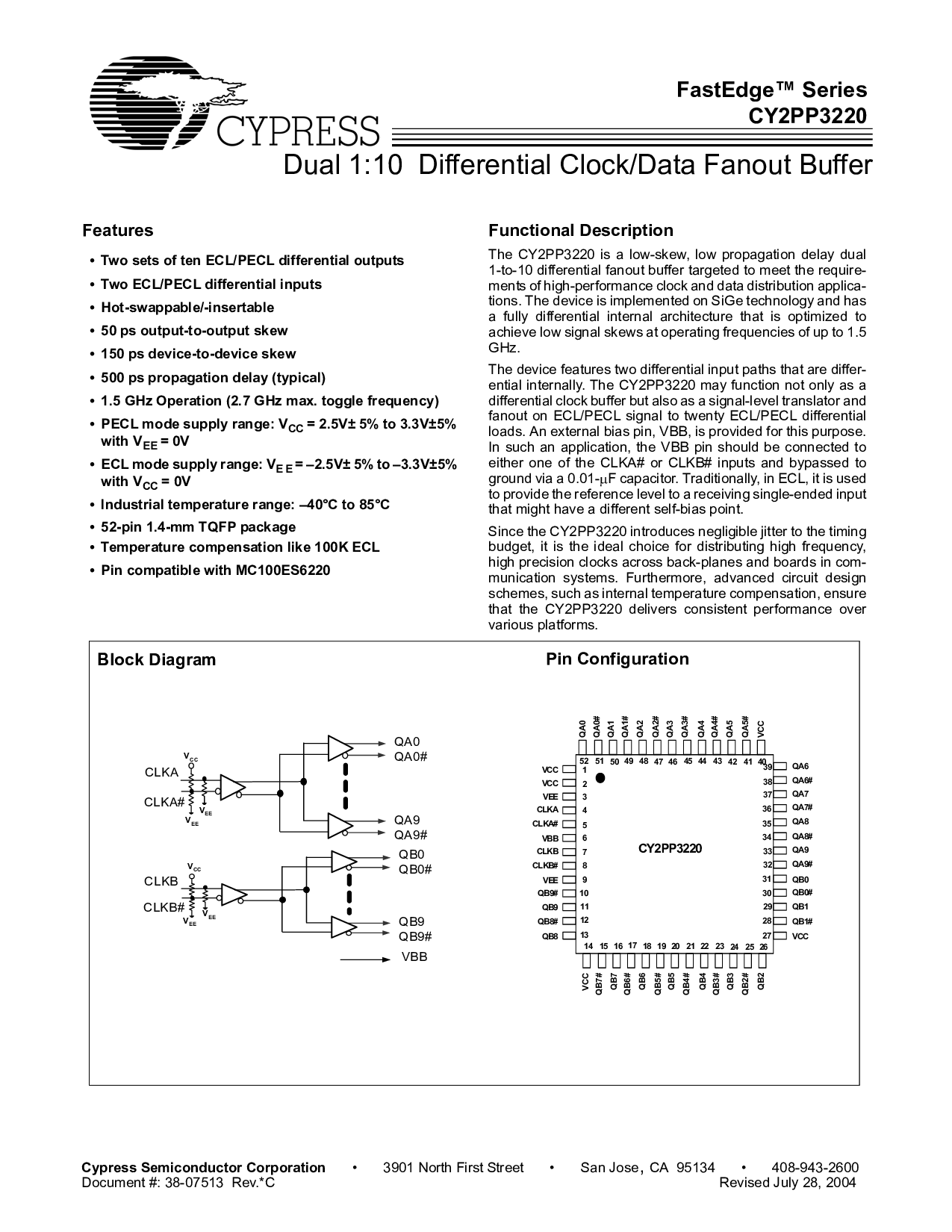

管脚 配置

CY2PP3220

40

4142

434445

4647

48

49

50

51

52

QA0

QA1

QA0#

QA1#

QA2

QA2#

QA3

QA3#

QA4

QA4#

QA5

QA5#

VCC

39

38

37

36

35

34

33

32

31

30

29

28

27

QA6

QA7

QA6#

QA7#

QA8

QA8#

QA9

QA9#

QB0

QB0#

QB1

QB1#

VCC

1

2

3

4

5

6

7

8

9

10

11

12

13

VCC

VEE

VCC

CLKA

CLKA#

VBB

CLKB

CLKB#

VEE

QB9#

QB9

QB8#

QB8

26

2524

232221

2019

18

17

16

15

14

VCC

QB7

QB7#

QB6#

QB6

QB5#

QB5

QB4#

QB4

QB3#

QB3

QB2#

QB2

CLKA

CLKA#

v

抄送

QA0

QA0#

QA9

QA9#

CLKB

CLKB#

QB0

QB0#

QB9

QB9#

v

ee

VBB

v

ee

v

抄送

v

ee

v

ee