320-mhz 1:7 pecl 至 pecl/cmos buffer

CY2PD817

柏树 半导体 公司

• 3901 北 第一 街道 • San Jose

,

ca 95134 • 408-943-2600

文件 #: 38-07574 rev. ** 修订 8月 28, 2003

特点

• 直流 至 320-mhz 操作

• 50-ps 输出-输出 偏斜

• 30-ps 循环-循环 抖动

• 2.5v 电源 供应

• lvpecl 输入 @ 320-mhz 操作

• 一个 lvpecl 输出 @ 320-mhz 操作

• 四 lvcmos/lvttl 产出 @ 250 mhz/160 mhz

• 两个 lvcmos/lvttl 产出 @ 250 mhz/80 mhz

• 45% 至 55% 输出 职责 循环

• 输出 分隔器 控制

• 输出 启用/禁用 控制

• 操作 温度 范围: 0°c 至 +85°c

• 24-管脚 tssop

描述

这 cy2pd817 是 一个 低电压 lvpecl-至-lvpecl 和

lvcmos 扇出 缓冲区 设计 用于 服务器, 数据 社区-

阳离子, 和 时钟 管理.

这 cy2pd817 是 理想 用于 应用程序 要求 混合 不同-

电位 和 单端 时钟 分布. 这个 设备 接受

一个 lvpecl 输入 参考 时钟 和 提供 一个 lvpecl

和 六个 lvcmos/lvttl 输出 时钟. 这 产出 是 parti-

规定的 进入 三个 银行 的 一个, 两个, 和 四 产出. 这

lvpecl 输出 是 一个 缓冲 复制 的 这 输入 时钟 同时 这

lvcmos 产出 是 分割 由 1, 2, 和 4. 当 clrdiv 是

设置 高, 这 输出 分隔器 是 设置 至 1. 入点 这个 模式, 这

最大值 输入 频率 是 有限 至 250 mhz.

当 oe

是 设置 高, 这 产出 是 已禁用 入点 一个 高z

州.

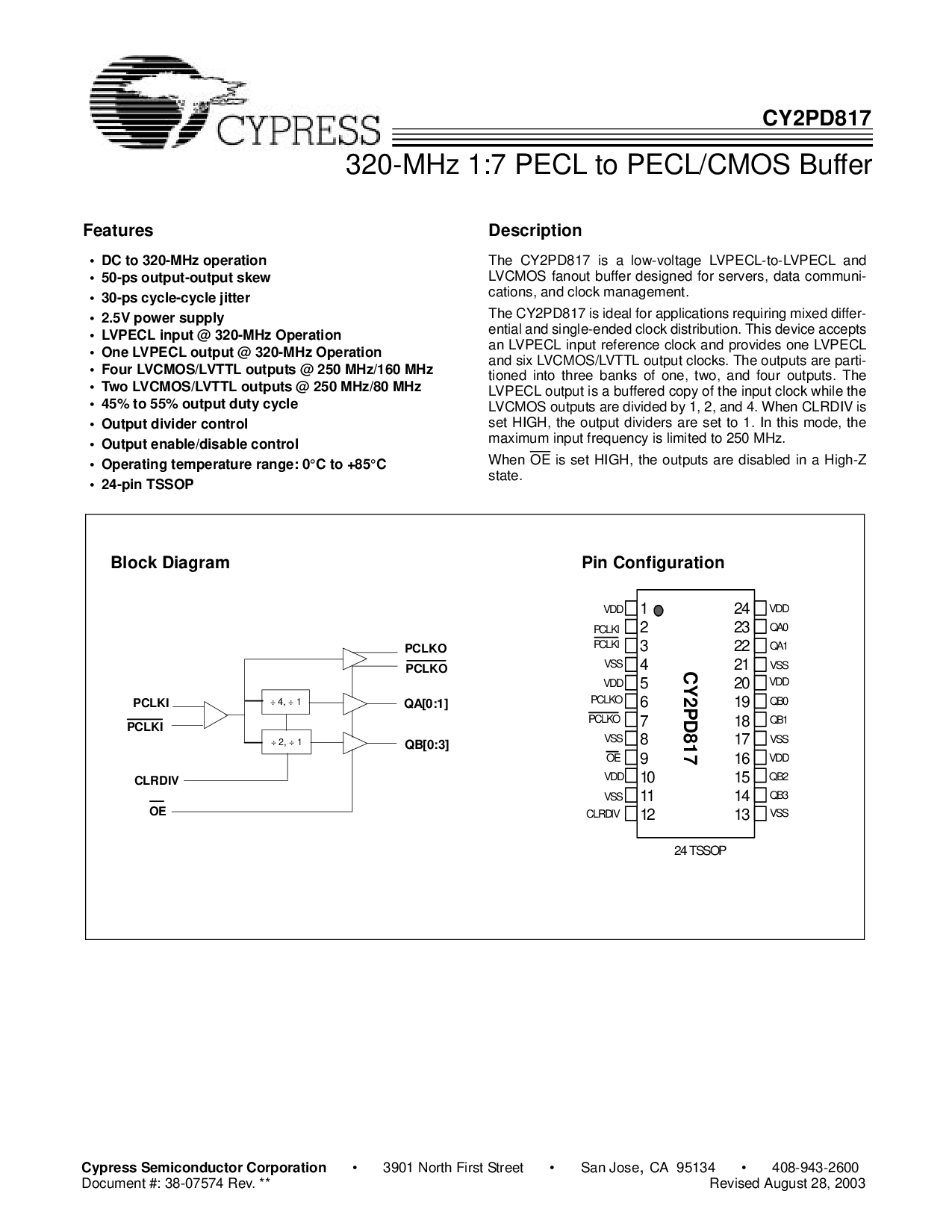

PCLKI

oe

÷ 4, ÷ 1

÷ 2, ÷ 1

qa[0:1]

qb[0:3]

PCLKO

CLRDIV

PCLKI

PCLKO

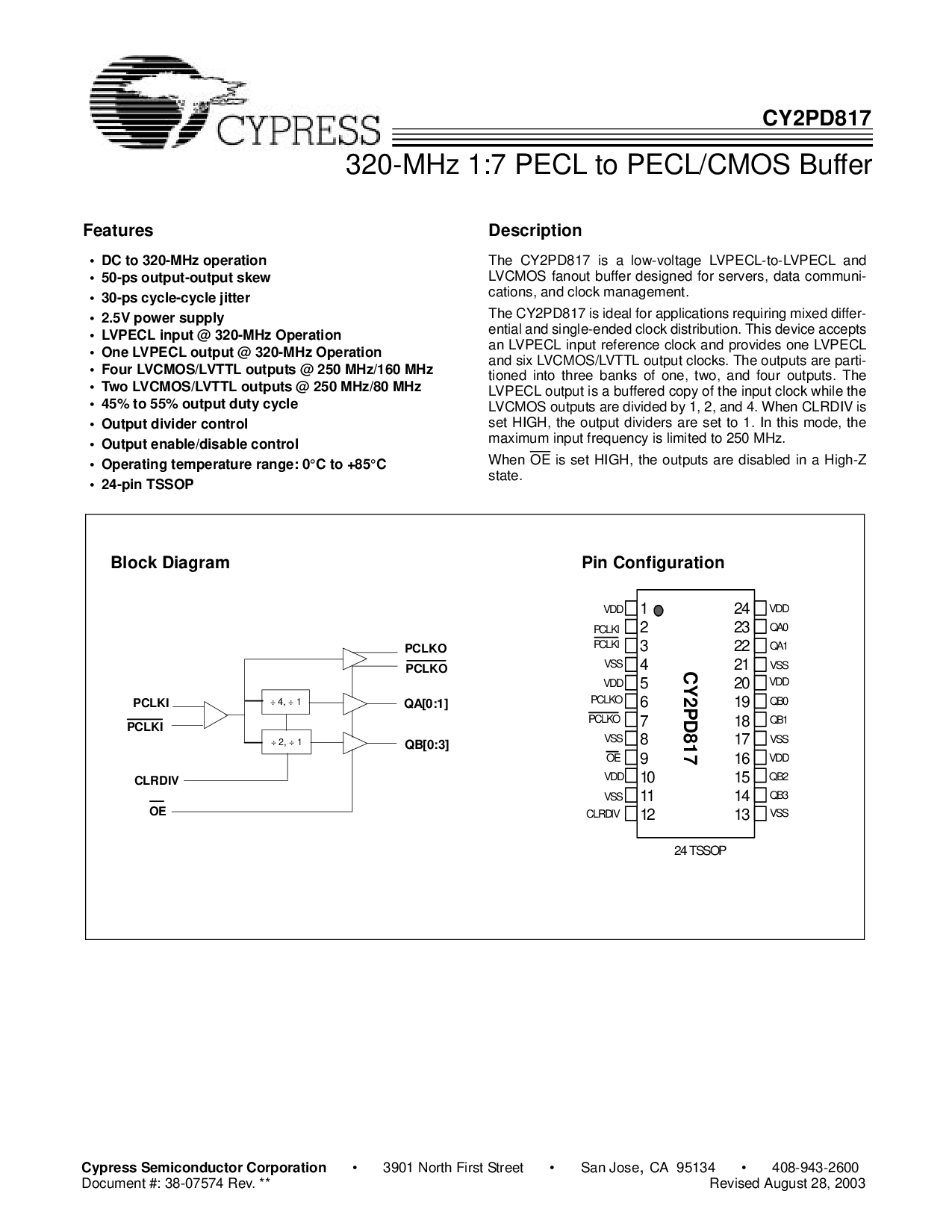

VDD

QA1

vss

QB2

vss

QB3

VDD

QA0

vss

VDD

QB0

QB1

VDD

vss

VDD

CLRDIV

vss

PCLKI

vss

VDD

PCLKO

1

2

3

4

5

6

7

8

9

10

11

12

24

23

22

21

20

19

18

17

16

15

14

13

24 tssop

CY2PD817

oe

PCLKI

PCLKO

块 图表 管脚 配置