1:4 时钟 扇出 布菲右

comlink™ 系列

CY2DL814

柏树 半导体 公司

• 3901 北 第一 街道 • San Jose

,

ca 95134 • 408-943-2600

文件 #: 38-07057 rev. *b 修订 六月 20, 2005

特点

• 低电压 操作

•V

dd

= 3.3v

• 1:4 扇出

• 单独-输入 可配置 用于

— lvds, lvpecl, 或 lvttl

— 四 差速器 对 的 lvds 产出

• 驱动器 50- 或 100-欧姆 荷载 (可选择)

• 低 输入 电容

• 85 ps 典型 output-至-输出 偏斜

• &指示灯;4 ns 典型 传播 延迟

• 是否 不 超过 bellcore 802.3 标准

• 操作 在

⇒

350 mhz – 700 mbps

• 工业 版本 可用

• 软件包 可用 包括 tssop/soic

描述

这 柏树 cy2 系列 的 网络 电路 是 生产 使用

高级 0.35-微米 cmos 技术, 实现 这

行业’s 最快 逻辑.

这 柏树 cy2dl814 扇出 缓冲区 特点 一个 单独

lvds-, lvpecl-, 或 lvttl-兼容 输入 和 四 lvds

输出 对.

设计 用于 数据-通信 时钟 管理 应用程序-

区域, 这 扇出 从 一个 单独 输入 减少 正在加载 开启 这

输入 时钟.

这 cy2dl814 是 理想 用于 两者都有 水平 翻译 从 单独

已结束 至 lvds 和/或 用于 这 分布 的 lvds-基于 时钟

信号. 这 柏树 cy2dl814 有 可配置 输入 和

输出 功能. 这 输入 可以 是 可选择 用于

lvpecl/lvttl 或 lvds 信号s 同时 这 输出 驾驶员’s

支持 标准 和 高 drive? lvds. 驱动器 要么 一个 50-欧姆

或 100-欧姆 线 与 一个 单独 零件 号码/设备.

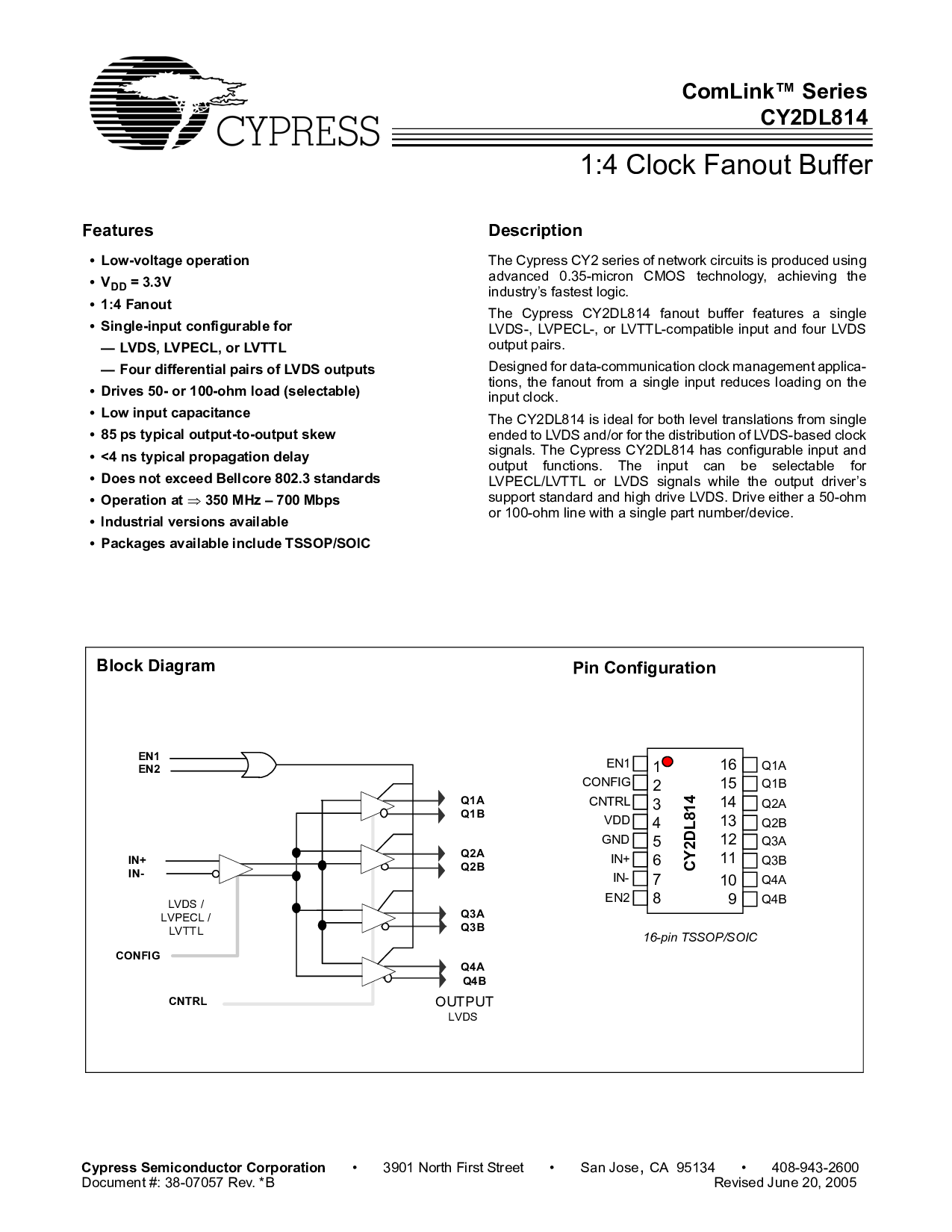

块 图表

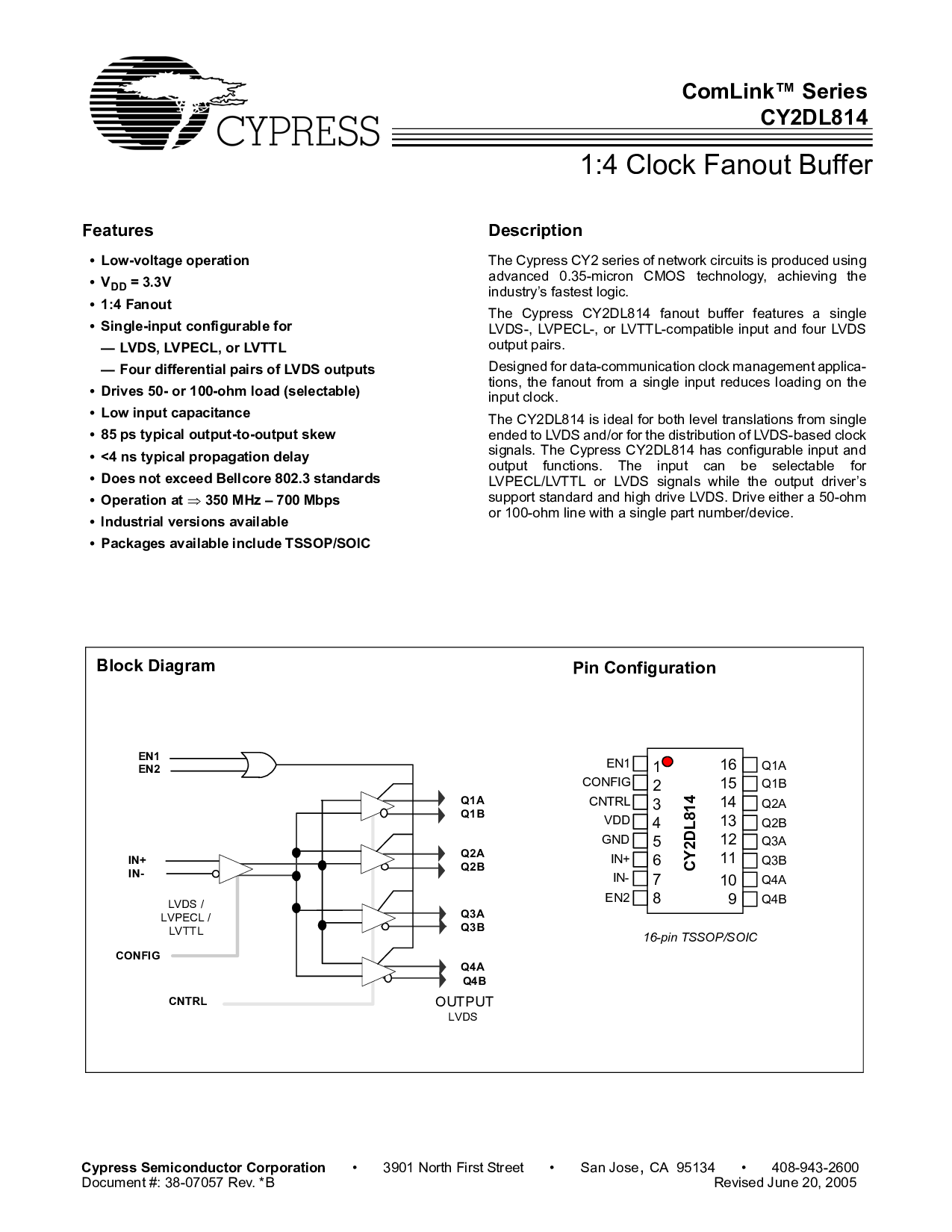

管脚 配置

输出

IN+

入点-

Q1A

Q1B

Q2A

Q2B

Q4A

Q4B

Q3A

Q3B

CNTRL

lvds /

lvpecl /

LVTTL

配置

EN1

EN2

LVDS

CY2DL814

16-管脚 tssop/soic

EN1

配置

CNTRL

VDD

IN+

入点-

EN2

地

Q1A

Q1B

Q2A

Q2B

Q3A

Q3B

Q4A

Q4B

1

2

3

4

5

6

7

8

10

9

11

12

13

14

15

16