2.5v 或 3.3v, 200-mhz

1:18 时钟 分布 缓冲区

cy29940-1

柏树 半导体 公司

• 3901 北 第一 街道 • San Jose

,

ca 95134 • 408-943-2600

文件 #: 38-07487 rev. ** 修订 january 28, 2003

特点

• 200-mhz 时钟 支持

• lvpecl 或 lvcmos/lvttl 时钟 输入

• lvcmos/lvttl-兼容 输入

• 18 时钟 产出: 驱动器 向上 至 36 时钟 线条

• 150 ps 最大值 输出到输出 偏斜

•23

Ω

输出 阻抗

• 双 或 单独 供应 操作:

— 3.3v 核心 和 3.3v 产出

— 3.3v 核心 和 2.5v 产出

— 2.5v 核心 和 2.5v 产出

• 引脚兼容 与 mpc940l, mpc9109

• 可用 入点 商业 和 工业 温度

范围

• 32-管脚 tqfp 包装

描述

这 cy29940-1 是 一个 低电压 200-mhz 时钟 分布

缓冲区 与 这 能力 至 选择 要么 一个 差速器 lvpecl-

或 一个 lvcmos/lvttl-兼容 输入 时钟. 这 两个 时钟

来源 可以 是 已使用 至 提供 用于 一个 测试一下 时钟 作为 井 作为 这

主要 系统 时钟. 全部 其他 控制 输入 是

lvcmos/lvttl-兼容. 这 十八 产出 是 2.5v

或 3.3v lvcmos/lvttl-兼容 和 可以 驱动器 50

Ω

系列

或 平行 已终止 变速器 线条. 用于 系列 已终止

变速器 线条, 每个 输出 可以 驱动器 一个 或 两个 痕迹

给予 这 设备 一个 有效 扇出 的 1:36. 低

输出到输出 偏斜 制造 这 cy29940-1 一个 理想 时钟

分布 缓冲区 用于 嵌套 时钟 树木 入点 这 大多数

要求苛刻 的 同步 系统.

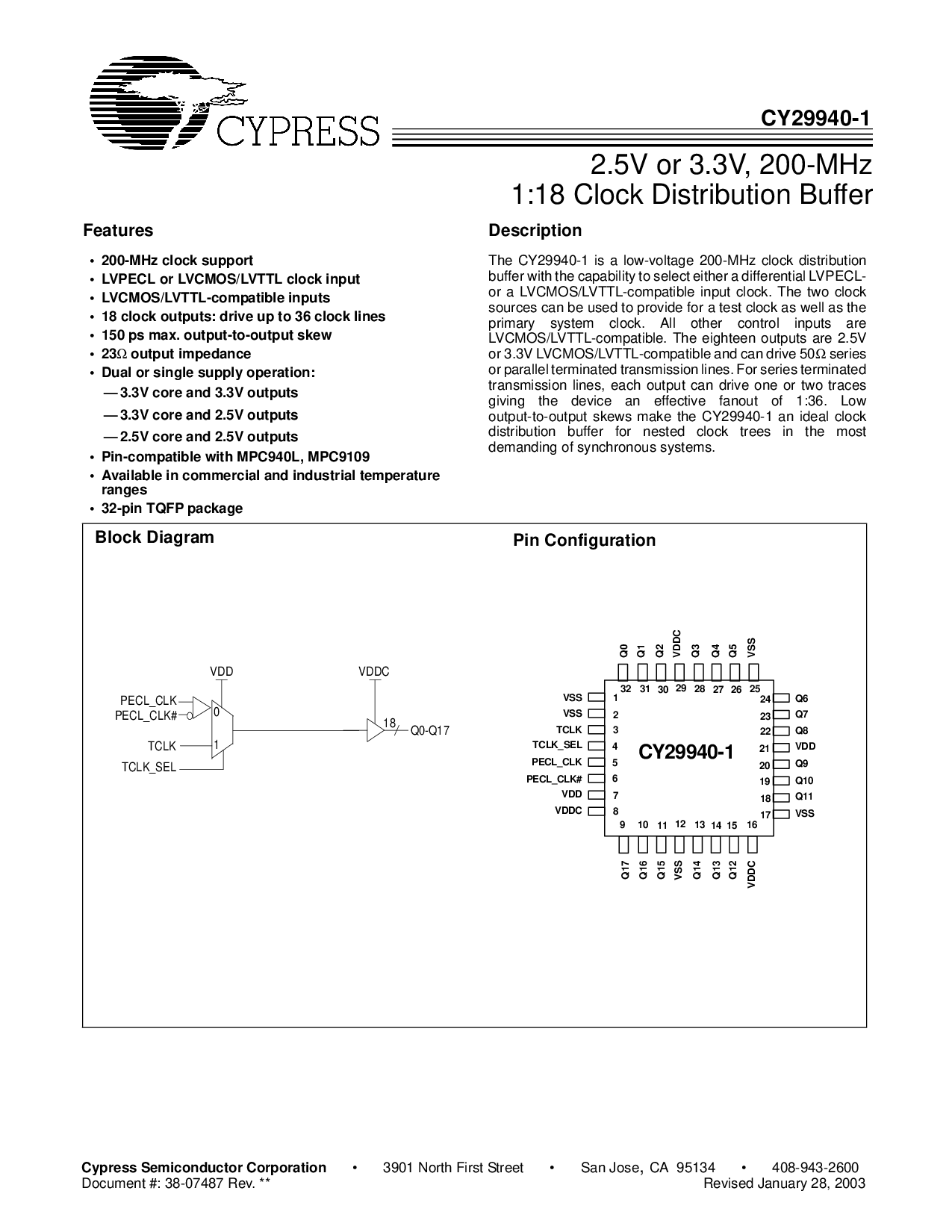

块 图表

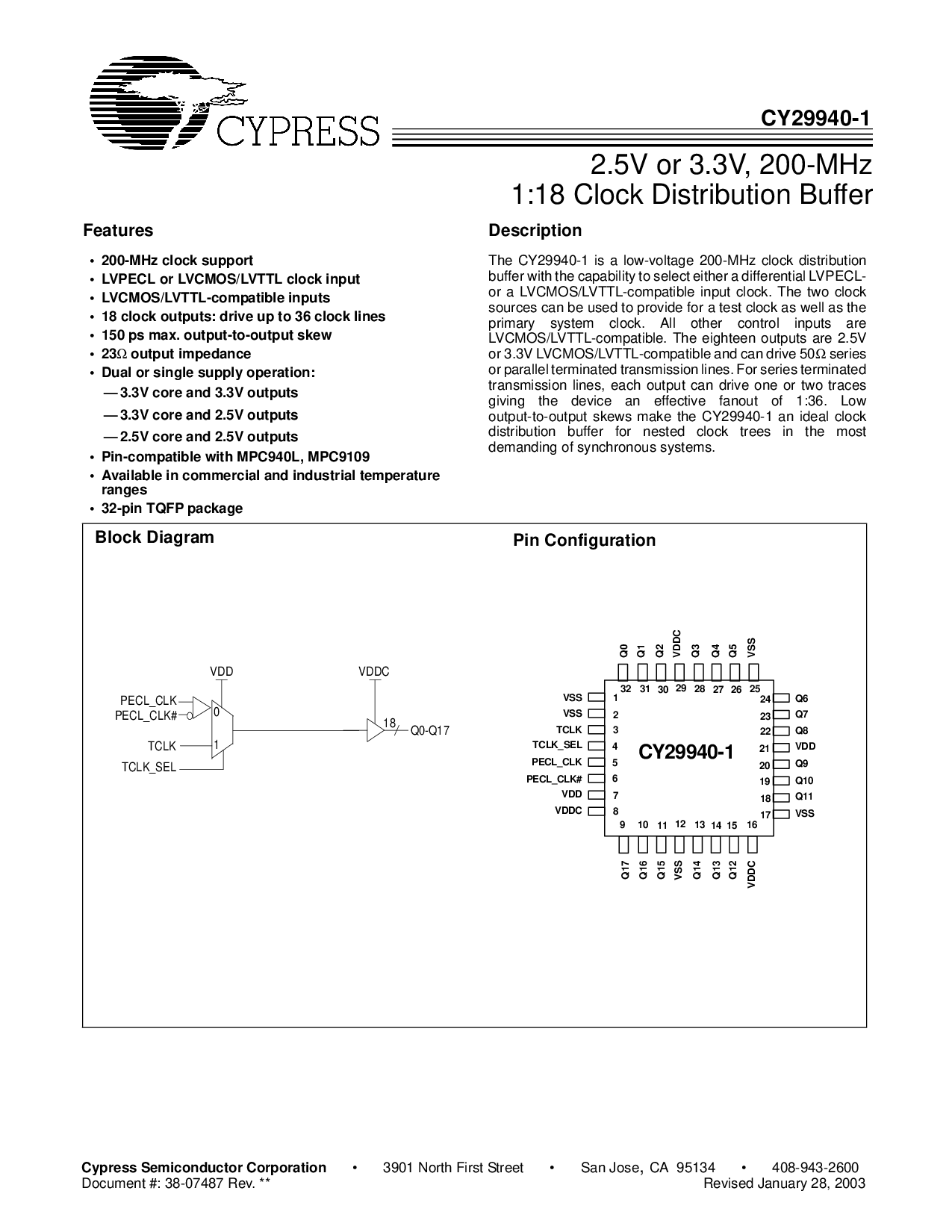

管脚 配置

pecl_clk

pecl_clk#

0

1

TCLK

tclk_选择

VDDC

18

q0-q17

VDD

cy29940-1

1

2

3

4

5

6

7

8

16

1514

13

12

11

10

9

Q17

Q15

Q16

vss

Q14

Q13

Q12

VDDC

24

23

22

21

20

19

18

17

Q6

Q8

Q7

VDD

Q9

Q10

Q11

vss

25

2627

28

29

30

3132

Q0

Q2

Q1

VDDC

Q3

Q4

Q5

vss

vss

TCLK

vss

tclk_选择

pecl_clk

pecl_clk#

VDD

VDDC