200-mhz 字段 可编程 零 延迟 布菲右

cy23fp12-002

柏树 半导体 公司

• 3901 北 第一 街道 • San Jose

,

ca 95134 • 408-943-2600

文件 #: 38-07644 rev. ** 修订 二月 25, 2004

特点

• 预编程 配置

• 完全 字段-可编程

— 输入 和 输出 分隔器

— 反转/非反相 产出

— 锁相 回路 (pll) 或 扇出 缓冲区 配置-

定量

• 10-mhz 至 200-mhz 操作 范围

• 拆分 2.5v 或 3.3v 产出

• 两个 lvcmos 参考 输入

• 十二 低偏斜 产出

— 输出-输出 偏斜 &指示灯; 200 ps

— 设备-设备 偏斜 &指示灯; 500 ps

• 输入-输出 偏斜 &指示灯; 250 ps

• 循环-循环 抖动&指示灯; 100 ps (典型)

• 三个-stateable 产出

•&指示灯; 50-

µ

一个 停机 电流

•spread 意识到

• 28-管脚 ssop

• 3.3v 操作

• 工业 温度 可用

功能 描述

这 cy23fp12-002 是 一个 预编程 版本 的 这

cy23fp12. 它 特点 一个 高性能 完全 字段-程序-

mable 200 mhz 零 延迟 缓冲区 设计 用于 高 速度

时钟 分布. 这 综合 pll 是 设计 用于 低 抖动

和 优化 用于 噪声 拒收. 这些 参数 是

关键 用于 参考 时钟 distribution 入点 系统ems 使用 高-

业绩 asics 和 微处理器.

这 cy23fp12-002 是 完全 可编程 通过 体积 或

原型 程序员 启用 这 用户 至 定义 一个 应用程序-

阳离子-具体 零 延迟 缓冲区 与 定制 输入 和

输出 分隔器, 反馈 拓扑 (内部/外部), 输出

反演, 和 输出 驱动器 优势. 用于 附加 灵活性,

这 用户 可以 混合 和 匹配 多个 功能, 已列出 入点

助教ble? 2

, 和 分配 一个 特别 功能 设置 至 任何 一个 的 这

四 可能 s1-s2 控制 bit 组合. 这个 功能

允许 用于 这 实施 的四 相异 personalities,

可选择 与 s1-s2 比特, 开启 一个 单独 编程 硅.

这 cy23fp12-002 也 特点 一个 专有 自动-电源-

向下 电路 那 关闭 向下 the? 设备 入点 案例 的 一个 参考

故障, 结果 入点 较少 比 50

µ

一个 的 电流 绘制.

这 cy23fp12-002 提供 十二 产出 分组 入点 两个

银行 与 分开 电源 供应 针脚 哪个 可以 是

已连接 独立 至 either 一个 2.5v 或 一个 3.3v 轨道.

可选择 参考 输入 是一个 故障 公差 功能 哪个

允许 用于 无故障 开关 结束 至 次要 时钟 来源

当 refsel 是 已断言/de-已断言.

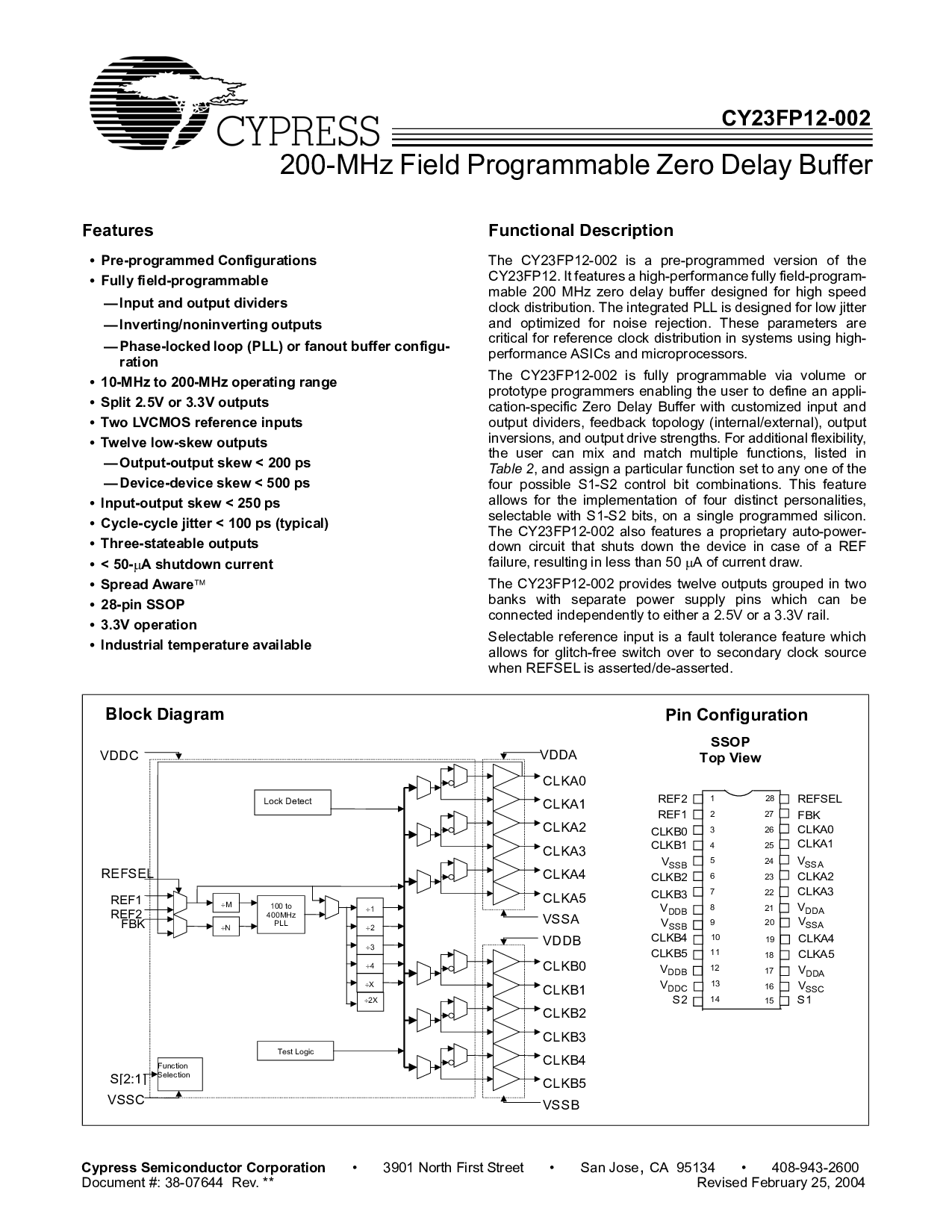

21

28

REFSEL

FBK

CLKA0

CLKA1

v

SSA

CLKA2

CLKA3

v

DDA

1

2

3

4

5

6

7

8

22

23

24

25

26

27

REF2

REF1

CLKB0

CLKB1

v

SSB

CLKB2

CLKB3

v

DDB

SSOP

顶部 查看

管脚 配置

17

v

DDA

20

v

SSA

19

CLKA4

18

CLKA5

16

v

SSC

15

S1

9

v

SSB

12

v

DDB

13

v

DDC

10

CLKB4

11

CLKB5

14

S2

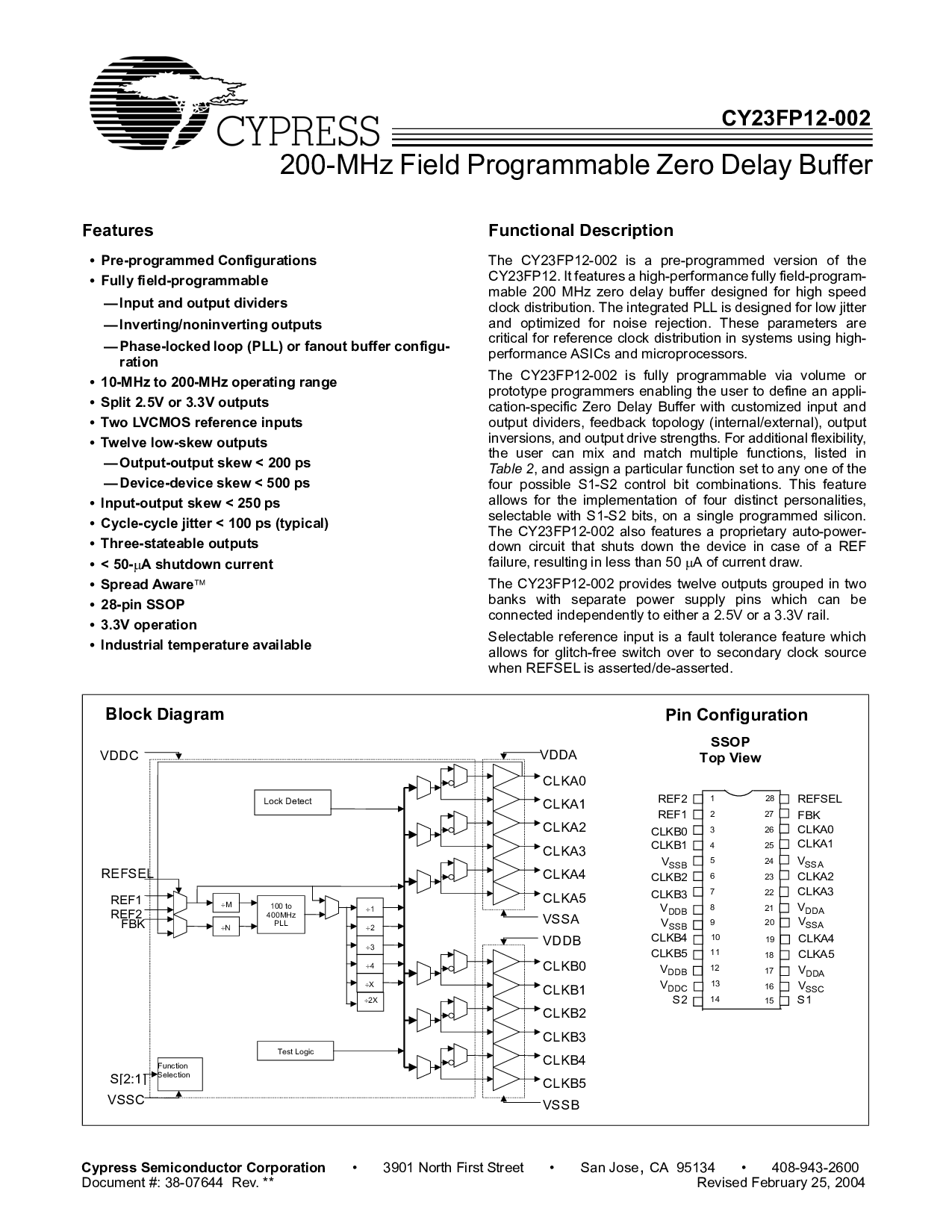

FBK

÷

m

÷

n

100 至

400MHz

PLL

CLKA1

CLKA3

CLKA2

REF2

REFSEL

CLKA4

CLKA5

CLKB1

CLKB3

CLKB2

CLKB4

CLKB5

VDDA

VSSA

VDDB

vSSB

÷

2

÷

3

÷

4

÷

x

CLKA0

VDDC

VSSC

÷

1

锁 检测

测试一下 逻辑

REF1

CLKB0

S[2:1]

功能

选择

÷

2X

块 图表