1

特点

•

行业标准 体系结构

– 仿真 许多 20-管脚 pals

®

– 低成本 易于使用 软件 工具

•

高速 可电擦除 可编程 逻辑 设备

– 7.5 ns 最大值 pin-to-pin 延迟

•

几个 电源 正在保存 选项

•

cmos 和 ttl 兼容 输入 和 产出

– 输入 和 我/o 上拉 电阻

•

高级 闪光灯 技术

– 可重新编程

– 100% 已测试

•

高可靠性 cmos 流程

– 20 年份 数据 保留

– 100 擦除/写 循环次数

– 2,000v esd 保护

– 200 ma latchup 免疫

•

商业, 和 工业 温度 范围

•

双列直插式 和 表面 安装 软件包 入点 标准 引出线

•

pci-符合

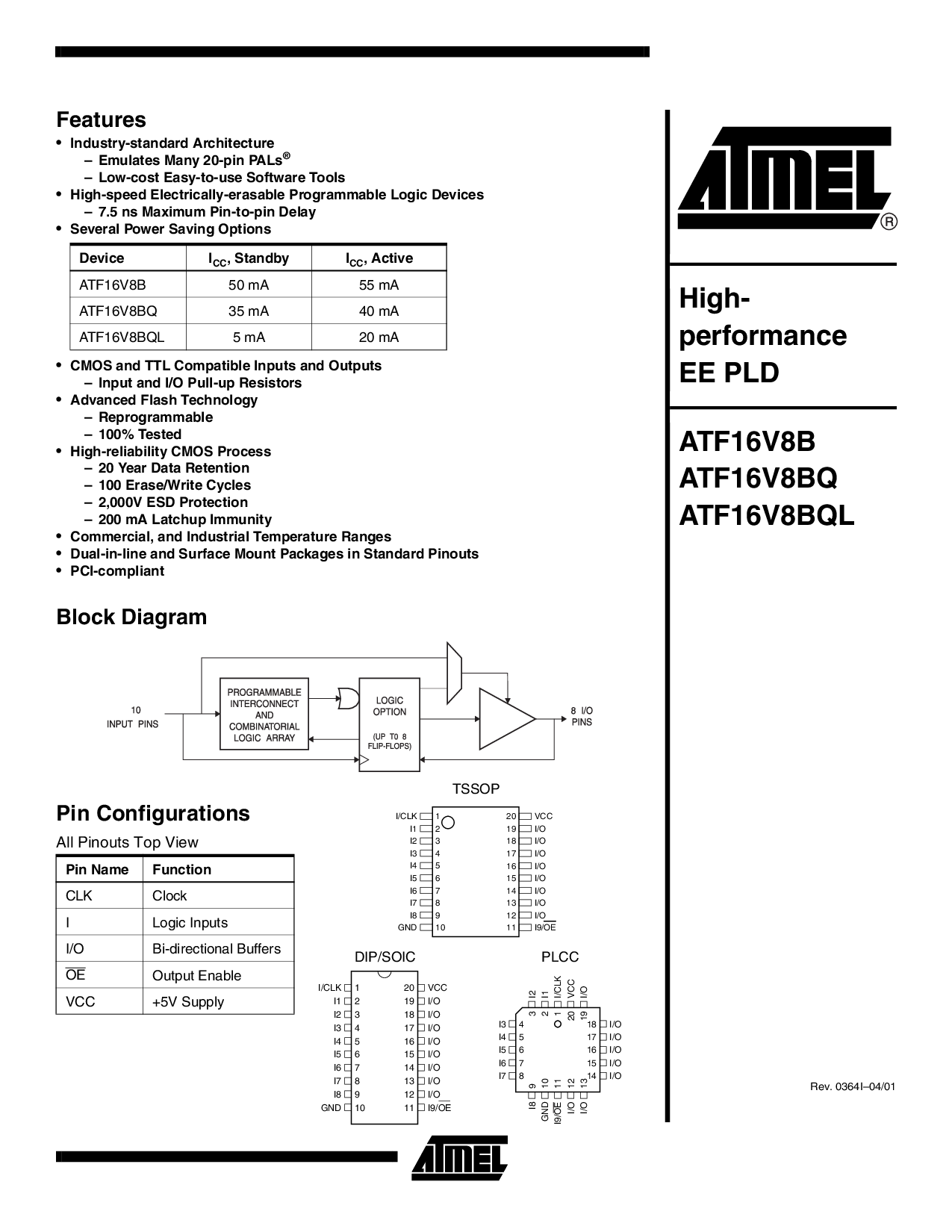

块 图表

设备 我

抄送

, 备用 我

抄送

, 活动

ATF16V8B 50 ma 55 ma

ATF16V8BQ 35 ma 40 ma

ATF16V8BQL 5 ma 20 ma

rev. 0364i–04/01

高-

业绩

ee PLD

在f16v8B

在f16v8Bq

在f16v8Bql

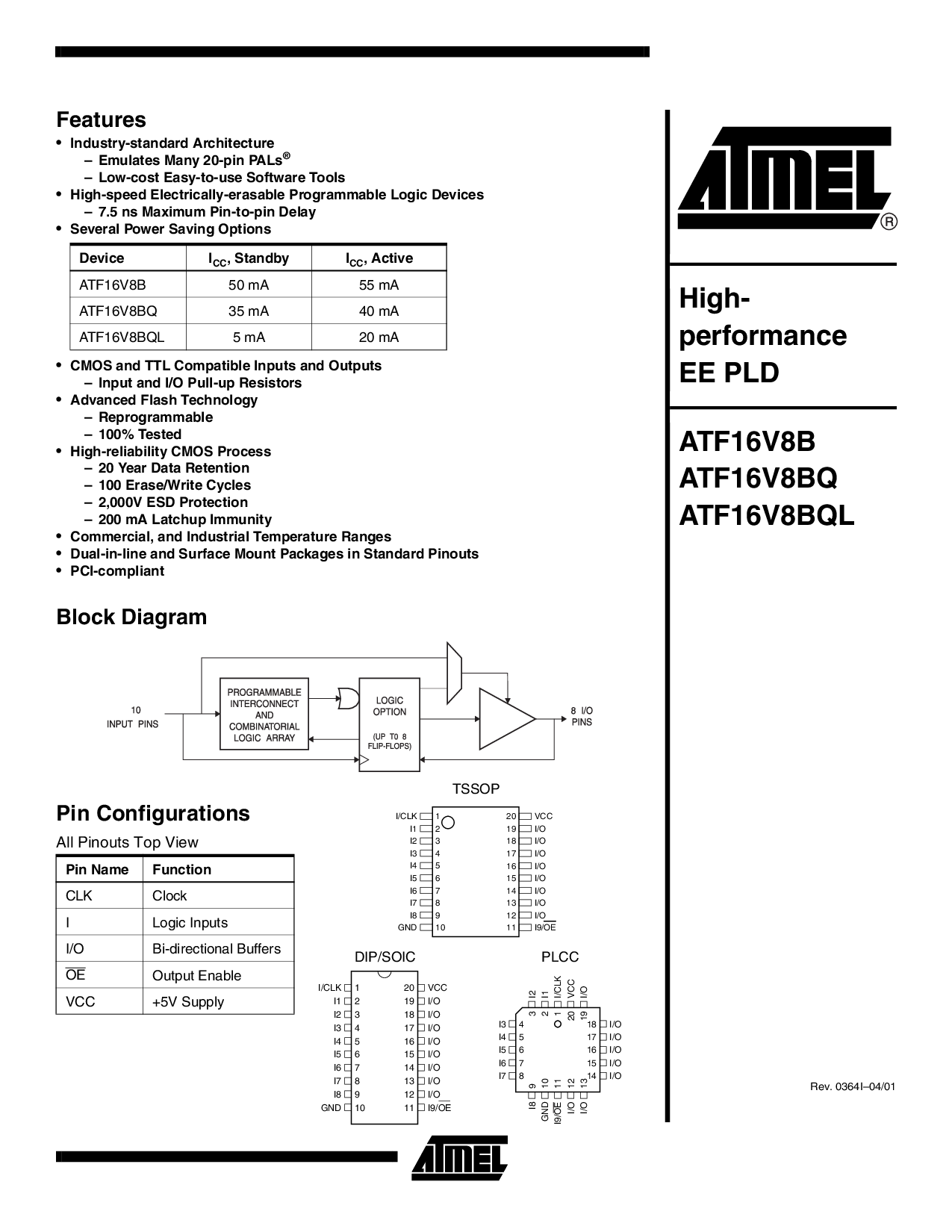

管脚 配置

全部 引出线 顶部 查看

管脚 姓名 功能

clk 时钟

我 逻辑 输入

我/o 双向 缓冲区

oe

输出 启用

VCC +5v 供应

TSSOP

1

2

3

4

5

6

7

8

9

10

20

19

18

17

16

15

14

13

12

11

我/clk

I1

I2

I3

I4

I5

I6

I7

I8

地

VCC

我/o

我/o

我/o

我/o

我/o

我/o

我/o

我/o

i9/oe

倾角/soic

1

2

3

4

5

6

7

8

9

10

20

19

18

17

16

15

14

13

12

11

我/clk

I1

I2

I3

I4

I5

I6

I7

I8

地

VCC

我/o

我/o

我/o

我/o

我/o

我/o

我/o

我/o

i9/oe

PLCC

4

5

6

7

8

18

17

16

15

14

I3

I4

I5

I6

I7

我/o

我/o

我/o

我/o

我/o

3

2

1

20

19

9

10

11

12

13

I8

地

i9/oe

我/o

我/o

I2

I1

我/clk

VCC

我/o