特点

eroflex 电路

技术

– risc turboengines 用于 这 未来 © scd5261 rev 1 12/22/98

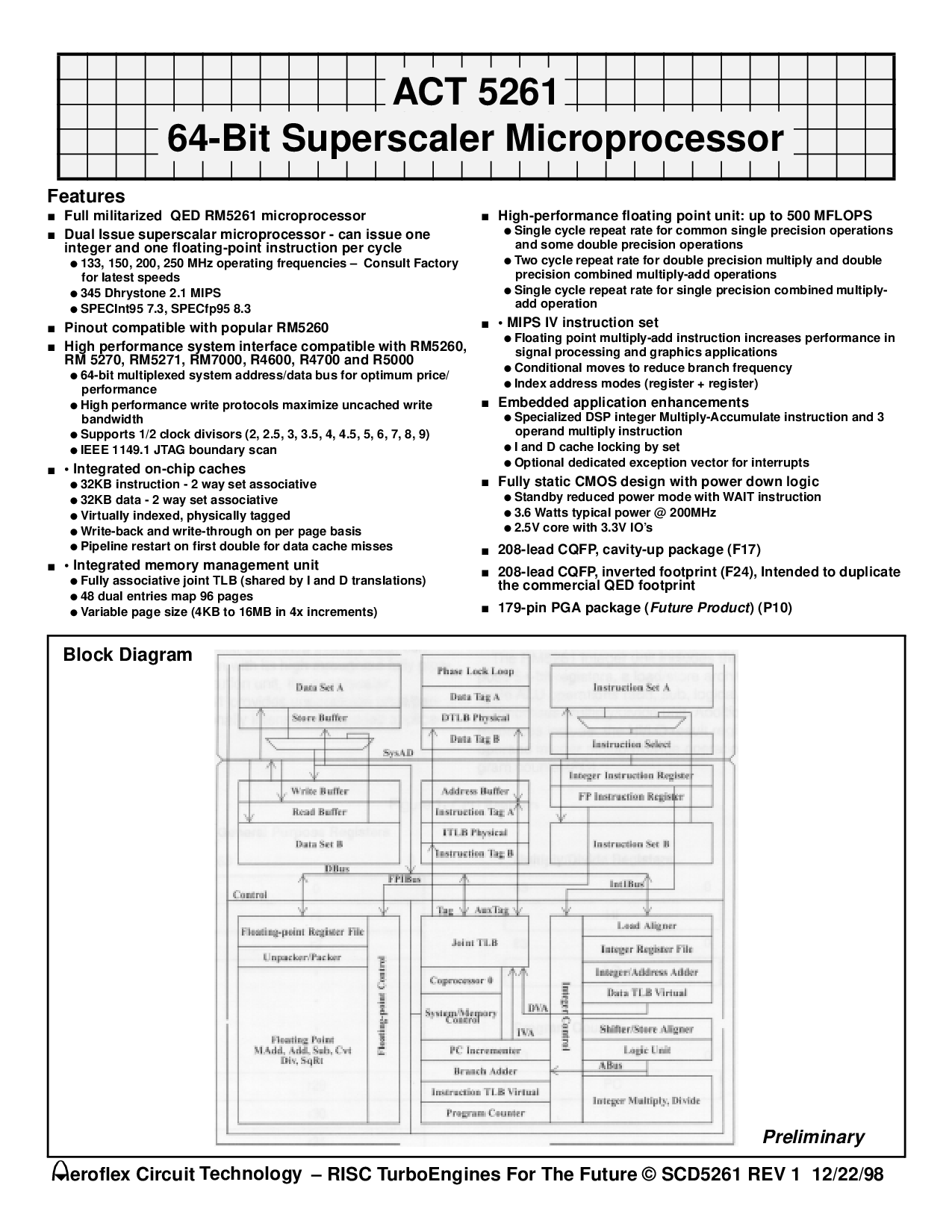

块 图表

■

已满 军事化 qed rm5261 微处理器

■

双 问题 超标量 微处理器 - 可以 问题 一个

整数 和 一个 浮点 说明书 按 循环

●

133, 150, 200, 250 mhz 操作 频率 – 咨询 工厂

用于 最新 速度

●

345 dhrystone 2.1 mips

●

specint95 7.3, specfp95 8.3

■

引出线 兼容 与 受欢迎 rm5260

■

高 业绩 系统 接口 兼容 与 rm5260,

rm 5270, rm5271, rm7000, r4600, r4700 和 r5000

●

64-有点 多路复用 系统 地址/数据 总线 用于 最佳 价格/

业绩

●

高 业绩 写 协议 最大化 未缓存 写

带宽

●

支架 1/2 时钟 除数 (2, 2.5, 3, 3.5, 4, 4.5, 5, 6, 7, 8, 9)

●

ieee 1149.1 jtag 边界 扫描

■

• 综合 片上 缓存

●

32kb 说明书 - 2 方式 设置 联想

●

32kb 数据 - 2 方式 设置 联想

●

几乎 索引, 物理 已标记

●

回写 和 直写 开启 按 第页 依据

●

管道 重新启动 开启 第一 双 用于 数据 高速缓存 错过

■

• 综合 记忆 管理 单位

●

完全 联想 接头 tlb (共享 由 我 和 d 翻译)

●

48 双 条目 地图 96 页数

●

变量 第页 尺寸 (4kb 至 16mb 入点 4x 增量)

■

高性能 浮动 点 单位: 向上 至 500 mflops

●

单独 循环 重复 费率 用于 普通 单独 精度 运营

和 一些 双 精度 运营

●

两个 循环 重复 费率 用于 双 精度 相乘 和 双

精度 合并 乘-加 运营

●

单独 循环 重复 费率 用于 单独 精度 合并 相乘-

添加 操作

■

• mips 四 说明书 设置

●

浮动 点 乘-加 说明书 增加 业绩 入点

信号 加工 和 图形 应用程序

●

有条件的 移动 至 减少 分支机构 频率

●

索引 地址 模式 (注册 + 注册)

■

嵌入式 应用程序 增强功能

●

专业化 dsp 整数 乘法-累加 说明书 和 3

操作数 相乘 说明书

●

我 和 d 高速缓存 锁定 由 设置

●

可选 专用 例外 向量 用于 中断

■

完全 静态 cmos 设计 与 电源 向下 逻辑

●

备用 减少 电源 模式 与 等待 说明书

●

3.6 瓦特 典型 电源 @ 200mhz

●

2.5v 核心 与 3.3v io’s

■

208-铅 cqfp, 空腔-向上 包装 (f17)

■

208-铅 cqfp, 倒置 占地面积 (f24), 预期 至 重复

这 商业 qed 占地面积

■

179-管脚 pga 包装 (

未来 产品

) (p10)

初步

64-有点 superscaler 微处理器

act 5261