1

09005aef80cd8e48 微米 技术, 股份有限公司., 储备金 这 右侧 至 变更 产品 或 规格 无 通知.

256mbsdramx32.p65 – rev. b; 酒吧. 03/04 ©2003 微米 技术, 公司

256mb: x32

SDRAM

初步

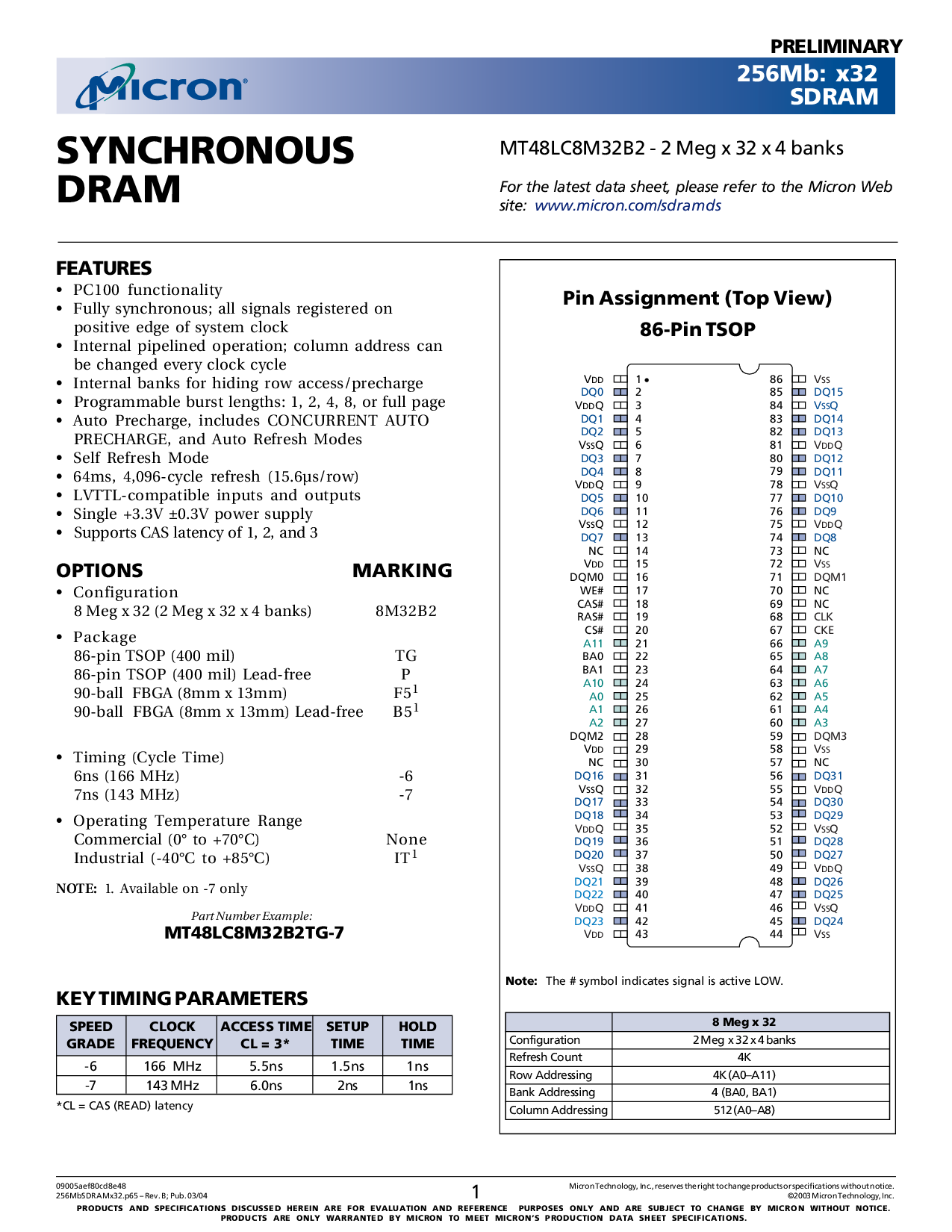

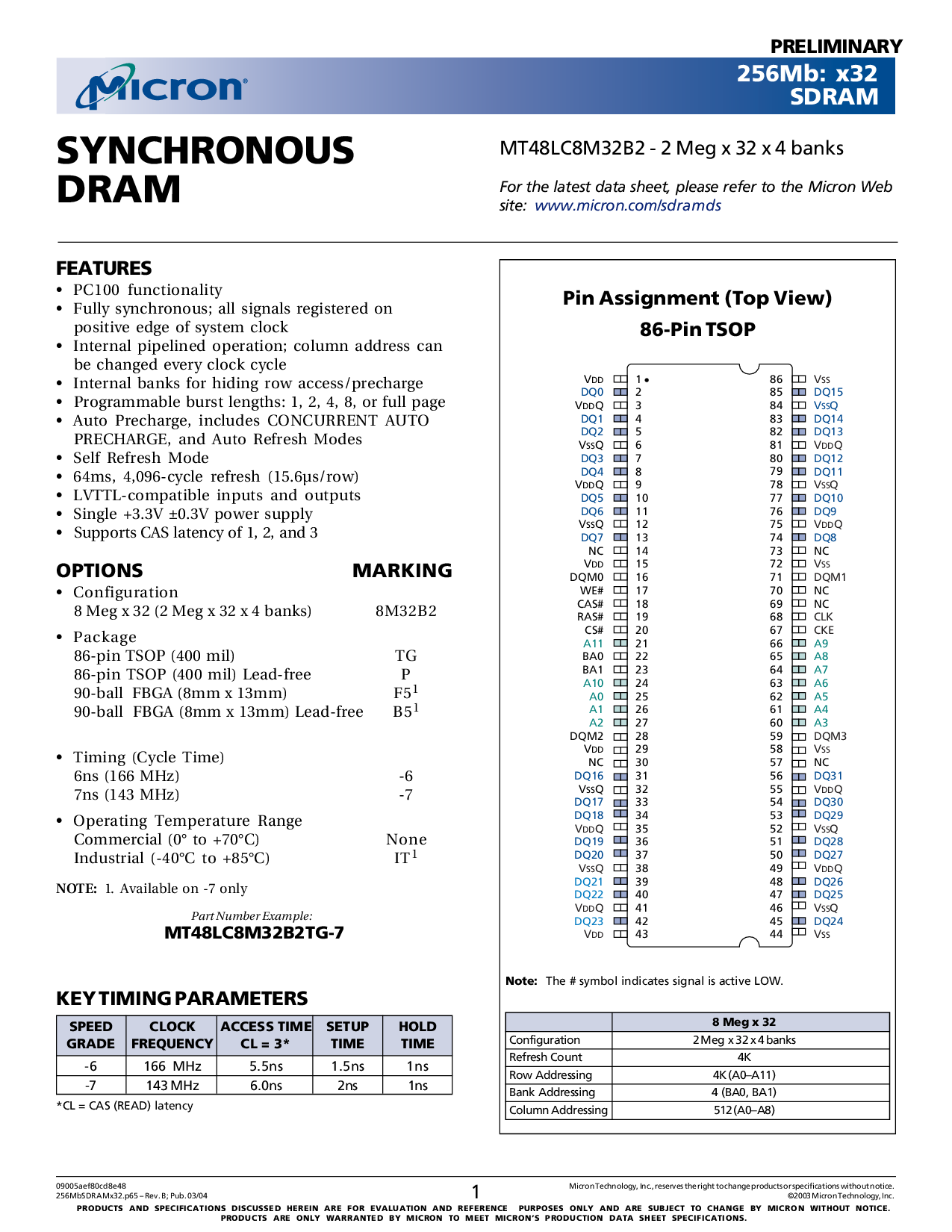

8 meg x 32

配置 2meg x 32 x 4 银行

刷新 计数 4K

行 寻址 4k (a0–a11)

银行 寻址 4 (ba0, ba1)

色谱柱 寻址 512 (a0–a8)

管脚 分配 (顶部 查看)

86-管脚 tsop

特点

• pc100 功能

• 完全 同步; 全部 信号 已注册 开启

正 边缘 的 系统 时钟

• 内部 流水线 操作; 色谱柱 地址 可以

是 已更改 每 时钟 循环

• 内部 银行 用于 隐藏 行 访问权限/预充电

• 可编程 突发 长度: 1, 2, 4, 8, 或 已满 第页

• 自动 预充电, 包括 并发 自动

预充电, 和 自动 刷新 模式

• 自我 刷新 模式

• 64ms, 4,096-循环 刷新 (15.6µs/行)

• lvttl-兼容 输入 和 产出

• 单独 +3.3v ±0.3v 电源 供应

• 支架 cas 延迟 的 1, 2, 和 3

选项 标记

• 配置

8 meg x 32 (2 meg x 32 x 4 银行) 8M32B2

• 包装

86-管脚 tsop (400 密耳) TG

86-管脚 tsop (400 密耳) 无铅 p

90-球 fbga (8mm x 13mm) F5

1

90-球 fbga (8mm x 13mm) 无铅 B5

1

• 计时 (循环 时间)

6ns (166 mhz) -6

7ns (143 mhz) -7

• 操作 温度 范围

商业 (0° 至 +70°c) 无

工业 (-40°c 至 +85°c) 它

1

备注:

1. 可用 开启 -7 仅

零件 号码 示例:

mt48lc8m32b2tg-7

备注:

这 # 符号 表示 信号 是 活动 低.

v

dd

DQ0

v

dd

q

DQ1

DQ2

v

ss

q

DQ3

DQ4

v

dd

q

DQ5

DQ6

v

ss

q

DQ7

nc

v

dd

DQM0

WE#

CAS#

RAS#

CS#

A11

BA0

BA1

A10

A0

A1

A2

DQM2

v

dd

nc

DQ16

v

ss

q

DQ17

DQ18

v

dd

q

DQ19

DQ20

v

ss

q

DQ21

DQ22

v

dd

q

DQ23

v

dd

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

86

85

84

83

82

81

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

v

ss

DQ15

v

ss

q

DQ14

DQ13

v

dd

q

DQ12

DQ11

v

ss

q

DQ10

DQ9

v

dd

q

DQ8

nc

v

ss

DQM1

nc

nc

clk

CKE

A9

A8

A7

A6

A5

A4

A3

DQM3

v

ss

nc

DQ31

v

dd

q

DQ30

DQ29

v

ss

q

DQ28

DQ27

v

dd

q

DQ26

DQ25

v

ss

q

DQ24

v

ss

同步

dram

mt48lc8m32b2 - 2 meg x 32 x 4 银行

用于 这 最新 数据 工作表, 请 参考 至 这 微米 web

现场: www.微米.com/sdramds

钥匙 计时 参数

速度 时钟 访问权限 时间 设置 保持

等级 频率 cl = 3* 时间 时间

-6 166 mhz 5.5ns 1.5ns 1ns

-7 143 mhz 6.0ns 2ns 1ns

*cl = cas (阅读) 延迟

产品 和 规格 讨论 此处 是 用于 评价 和 参考 目的 仅 和 是 主题 至 变更 由 微米 无 通知.

产品 是 仅 保证 由 微米 至 满足 微米’s 生产 数据 工作表 规格.