半导体 组件 行业, llc, 2004

六月, 2004 − rev. 7

1

出版物 订单 号码:

mc10ep32/d

mc10ep32, mc100ep32

3.3v / 5vecl

2 分隔器

这 mc10/100ep32 是 一个 综合

2 分隔器 与 差速器

clk 输入.

这 v

bb

管脚, 一个 内部 已生成 电压 供应, 是 可用 至

这个 设备 仅. 用于 单端 输入 条件, 这 未使用

差速器输入 是 已连接 至 v

bb

作为 一个 开关 参考 电压.

v

bb

将 也 重新偏置 交流电 耦合 输入. 当 已使用, 解耦 v

bb

和 v

抄送

通过 一个 0.01

f 电容器 和 限制 电流 采购 或 下沉

至 0.5 ma. 当 不 已使用, v

bb

应该 是 左 打开.

这 重置 管脚 是 异步 和 是 已断言 开启 这 上升 边缘.

在 上电, 这 内部 触发器 将 获得 一个 随机 州; 这

重置 允许 用于 这 同步 的 多个 ep32’s 入点 一个 系统.

这 100 系列 包含 温度 补偿.

•

350 ps 典型 传播 延迟

•

最大值 频率 > 4 ghz 典型 (图 3)

•

pecl 模式 操作 范围:

v

抄送

= 3.0 v 至 5.5 v 与 v

ee

= 0 v

•

necl 模式 操作 范围:

v

抄送

= 0 v 与 v

ee

= −3.0 v 至 −5.5 v

•

打开 输入 默认 州

•

安全 卡箍 开启 输入

•

q 输出 将 默认 低 与 输入 打开 或 在 v

ee

•

pb−free 包装 是 可用

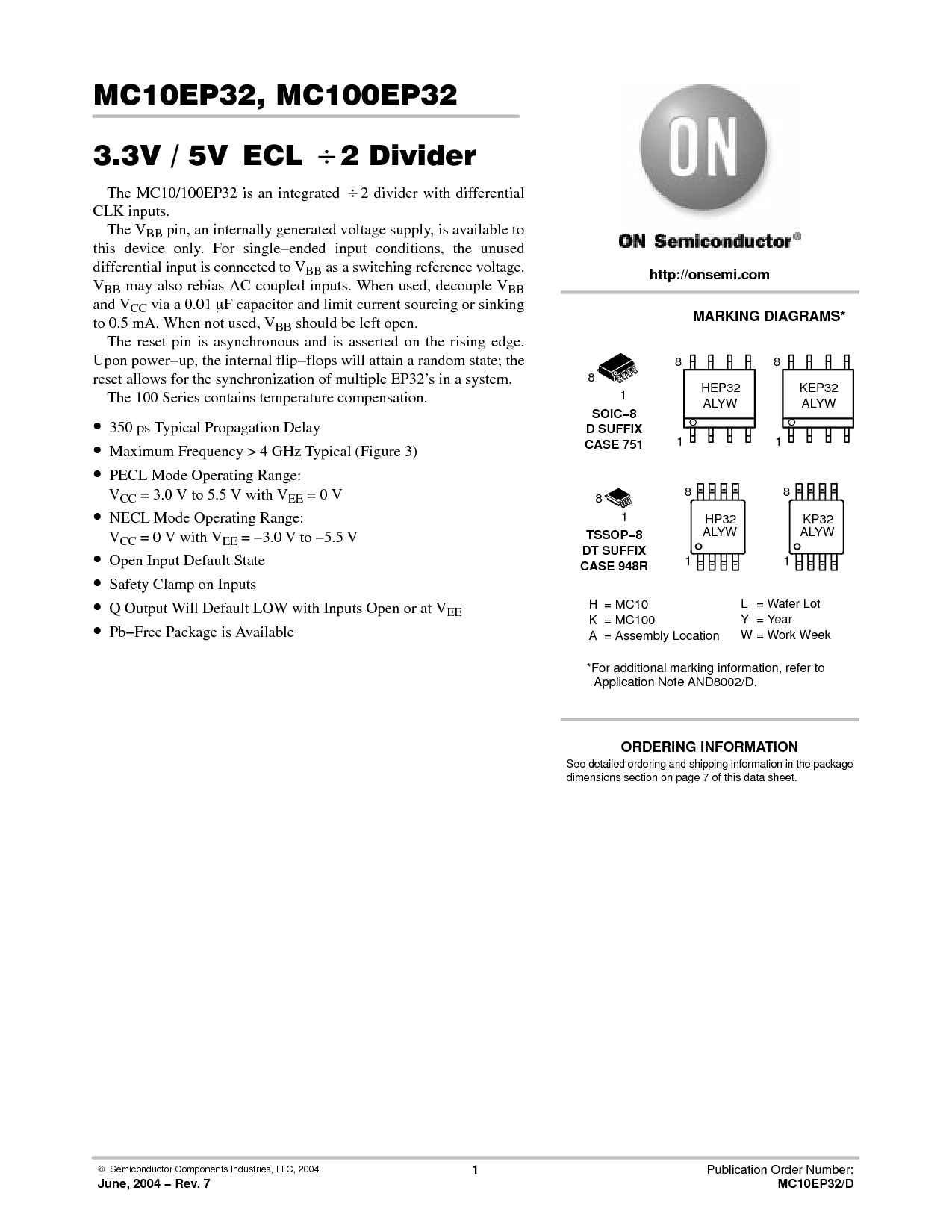

l = 晶圆 批号

y = 年份

w = 工作 周

h = mc10

k = mc100

一个 = 总成 位置

SOIC−8

d 后缀

案例 751

标记 diagrams*

TSSOP−8

dt 后缀

案例 948r

ALYW

KEP32

ALYW

HP32

HEP32

ALYW

ALYW

KP32

1

8

1

8

1

8

1

8

1

8

1

8

http://onsemi.com

*for 附加 标记 信息, 参考 至

应用程序 备注 and8002/d.

请参见 详细 订购 和 装运 信息 入点 这 包装

尺寸 截面 开启 第页 7 的 这个 数据 工作表.

订购 信息