april 1999

英特尔 和 pentium 是 已注册 商标 的 英特尔 公司. 我

2

c 是 一个 许可 商标 的 飞利浦 电子产品, n.v. 美国 microsystems, 公司 储备金 这 右侧 至 变更 这 详图 规格ifica-

区域 作为 将 是 必填项 至 许可证 改进 入点 这 设计 的 其 产品.

4.5.99

1.0 特点

•

生成 向上 至 十八 低-偏斜, 非反相

时钟 从 一个 时钟 输入

•

支架 向上 至 四 sdram dimms

•

用途 要么 我

2

c

-总线 或 smbus 串行 接口 与

阅读 和 w仪式 能力 用于 个人 时钟 输出

控制

•

输出 启用 管脚 三州 全部 时钟 产出 至 facili-

泰特 板 测试

•

时钟 产出 偏斜-匹配 至 较少 比 250ps

•

较少 比 5ns 传播 延迟

•

输出 阻抗: 17

Ω

在 0.5v

dd

•

串行 接口 我/o 满足 我

2

c 规格; 全部 其他

我/o 是 lvttl/lvcmos-兼容

•

五个 differerent 管脚 配置 可用:

•

fs6050: 18 时钟 产出 入点 一个 48-管脚 ssop

•

fs6051: 10 时钟 产出 入点 一个 28-管脚 soic, ssop

•

fs6053: 13 时钟 产出 入点 一个 28-管脚 soic

•

fs6054: 14 时钟 产出 入点 一个 28-管脚 soic

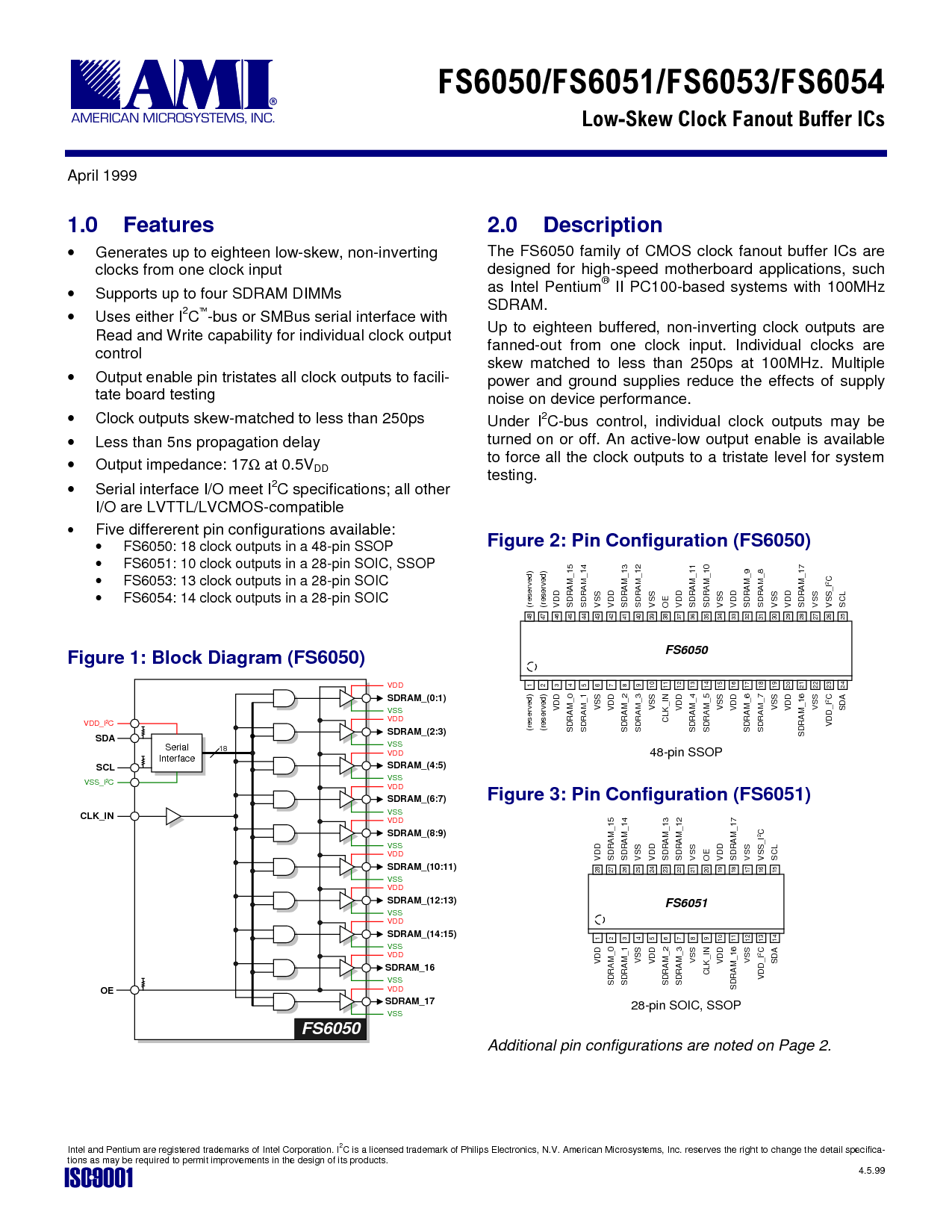

图 1: 块 图表 (fs6050)

串行

接口

sdram_(0:1)

scl

SDA

clk_入点

oe

FS6050

sdram_(2:3)

sdram_(4:5)

sdram_(6:7)

sdram_(8:9)

sdram_(10:11)

sdram_(12:13)

sdram_(14:15)

sdram_16

vss_我

2

c

vdd_我

2

c

vss

VDD

vss

VDD

vss

VDD

vss

VDD

vss

VDD

vss

VDD

vss

VDD

vss

VDD

vss

VDD

sdram_17

vss

VDD

18

2.0 描述

这 fs6050 家庭 的 cmos 时钟 扇出 缓冲区 ics 是

设计 用于 高速 主板 应用程序, 这样的

作为 英特尔 pentium

®

二 pc100-基于 系统 与 100mhz

sdram.

向上 至 十八 缓冲, 非反相 时钟 产出 是

扇子-出点 从 一个 时钟 输入. 个人 时钟 是

偏斜 匹配 至 较少 比 250ps 在 100mhz. 多个

电源 和 接地 供应品 减少 这 效果 的 供应

噪声 开启 设备 业绩.

下 我

2

c-总线 控制, 个人 时钟 产出 将 是

翻转 开启 或 关. 一个 低电平有效 输出 启用 是 可用

至 力 全部 这 时钟 产出 至 一个 三态 水平 用于 系统

测试.

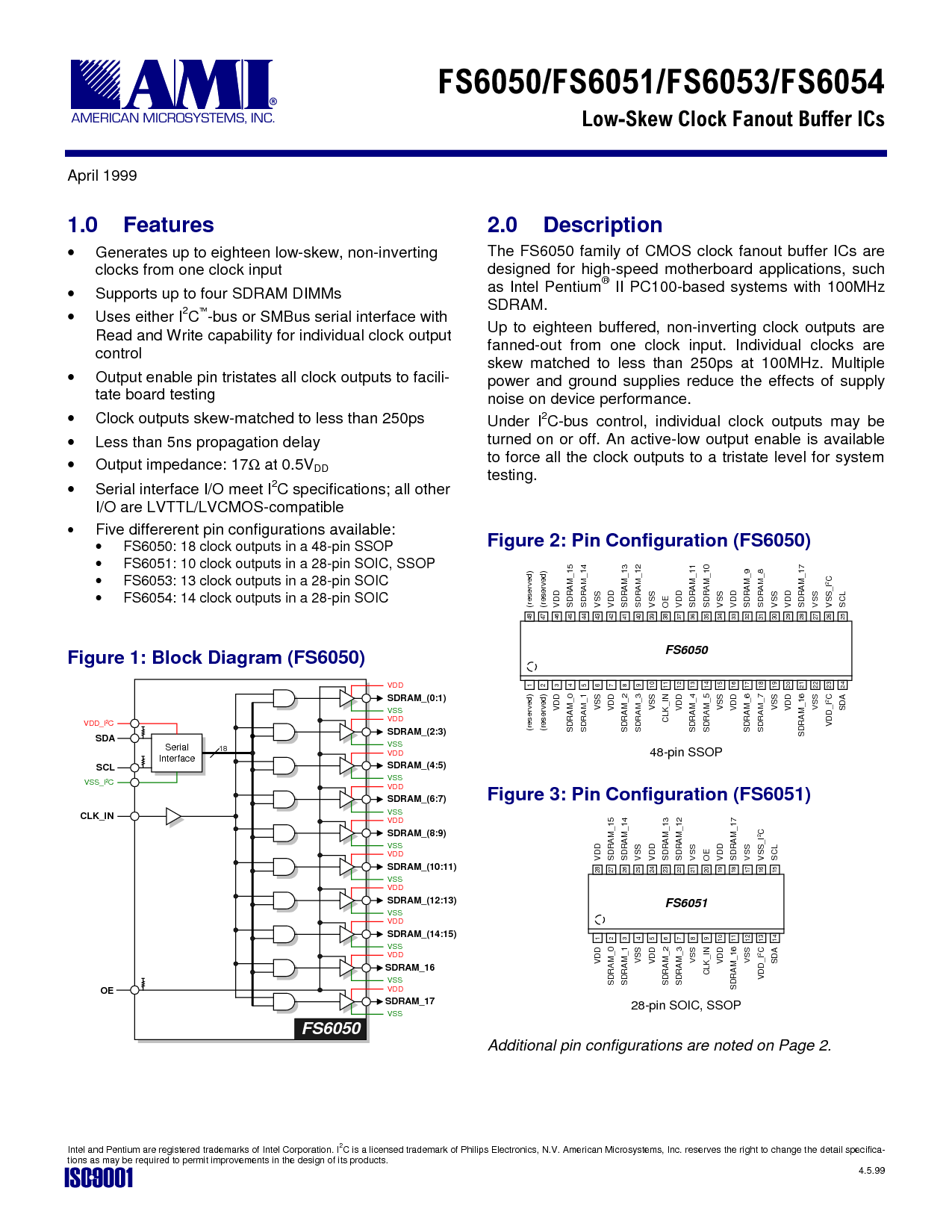

图 2: 管脚 配置 (fs6050)

1 48

2

3

4

5

6

7

8

47

46

45

44

43

42

41

(保留)

(保留)

VDD

sdram_0

sdram_1

vss

VDD

sdram_2

vss

sdram_14

sdram_15

(保留)

VDD

(保留)

9

10

11

12

13

14

15

16

sdram_3

vss

clk_入点

VDD

sdram_4

sdram_5

vss

VDD

17

18

19

20

21

22

23

sdram_6

sdram_7

vss

VDD

sdram_16

vss

vdd_我

2

c

40

39

38

37

36

35

34

33

sdram_10

sdram_11

VDD

oe

sdram_13

sdram_12

vss

VDD

32

31

30

29

28

27

26

vss_我

2

c

vss

sdram_17

VDD

sdram_9

sdram_8

vss

24

SDA

25

scl

VDD

vss

FS6050

48-管脚 ssop

图 3: 管脚 配置 (fs6051)

1

2

3

4

5

6

7

8

VDD

sdram_0

sdram_1

vss

VDD

sdram_2

vss

sdram_14

sdram_15

VDD

9

10

11

12

13

14

15

16

sdram_3

vss

clk_入点

VDD

17

18

19

20

21

22

23

sdram_16

vss

vdd_我

2

c

VDD

oe

sdram_13

sdram_12

vss

VDD

28

27

26

vss_我

2

c

vss

sdram_17

24

SDA

25

scl

FS6051

28-管脚 soic, ssop

附加 管脚 配置 是 已注明 开启 第页 2.