3-34

特点

• 通常 较少 比 2

µ

v

p-p

噪声 (200.00mv 已满

缩放, lcl8068)

• 准确度 保证 至

±

1 计数 结束 整个

±

20,000

计数 (2.0000v 已满 缩放)

• 保证 零 阅读 用于 0v 输入

• 真 极性 在 零 计数 用于 精确 null 检测

• 单独 参考 电压 必填项

• 超范围 和 下-范围 信号 可用 用于

自动-测距 能力

• 全部 产出 ttl 兼容

• 中 质量 参考, 40ppm (典型值) 开启 板

• 闪烁 显示 给出 目视检查 指示 的 结束

范围

• 六个 辅助 输入/产出 是 可用 用于

接口 至 uarts, 微处理器 或 其他

复杂 电路

• 5pa 输入 电流 (典型值) (8052a)

描述

这 icl8052 或 icl8068/lcl71c03 芯片 对 与 他们的

多路复用 bcd 输出 和 数字 驱动程序 是 理想情况下 适合

用于 这 目视检查 显示 dvm/dpm 市场. 这 未结清

4

1

/

2

数字 准确度, 200.00mv 至 2.0000v 已满 缩放 capabil-

国家, 自动归零 和 自动-极性 联合收割机 与 真 比率计

操作, 几乎 理想 差速器 线性度 和 时间-经过验证

双 坡度 换算. 使用 的 这些 芯片 对 消除

时钟 馈通 问题, 和 避免 这 关键 板

布局 通常 必填项 至 最小化 费用 注射.

当 仅 2000 计数 的 分辨率 是 必填项, 这 71c03

可以 是 有线 用于 3

1

/

2

数字 和 给 向上 至 30 读数/秒.,

制作 它 理想情况下 适合 用于 一个 宽 品种 的 应用程序.

这 icl71c03 是 一个 改进 cmos 插件 更换 用于

这 lcl7103 和 应该 是 已使用 入点 全部 新建 设计.

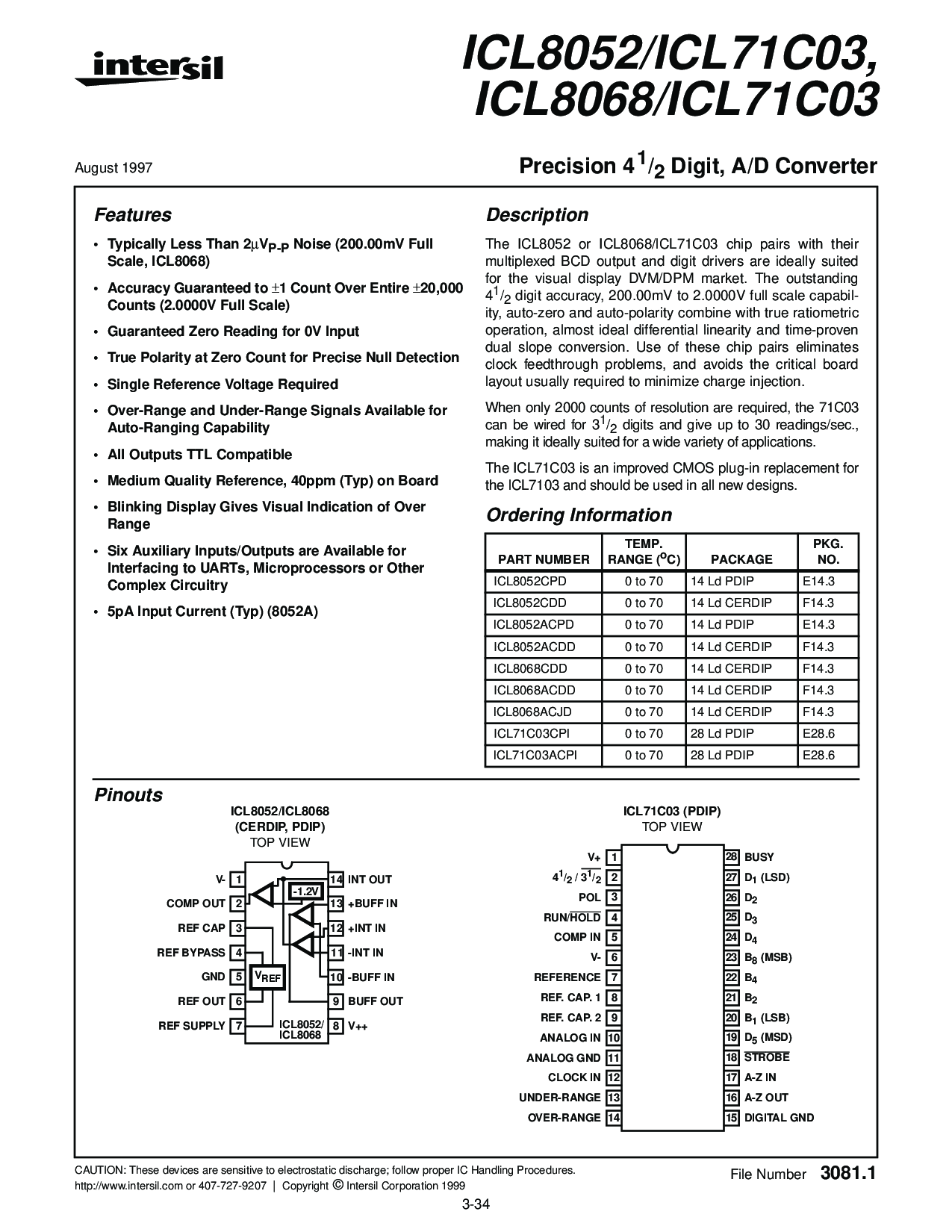

引出线

订购 信息

零件 号码

温度

范围 (

o

c) 包装

pkg.

否.

ICL8052CPD 0 至 70 14 ld pdip e14.3

lCL8052CDD 0 至 70 14 ld cerdip f14.3

lCL8052ACPD 0 至 70 14 ld pdip e14.3

ICL8052ACDD 0 至 70 14 ld cerdip f14.3

ICL8068CDD 0 至 70 14 ld cerdip f14.3

ICL8068ACDD 0 至 70 14 ld cerdip f14.3

lCL8068ACJD 0 至 70 14 ld cerdip f14.3

ICL71C03CPl 0 至 70 28 ld pdip e28.6

lCL71C03ACPl 0 至 70 28 ld pdip e28.6

icl8052/icl8068

(cerdip, pdip)

顶部 查看

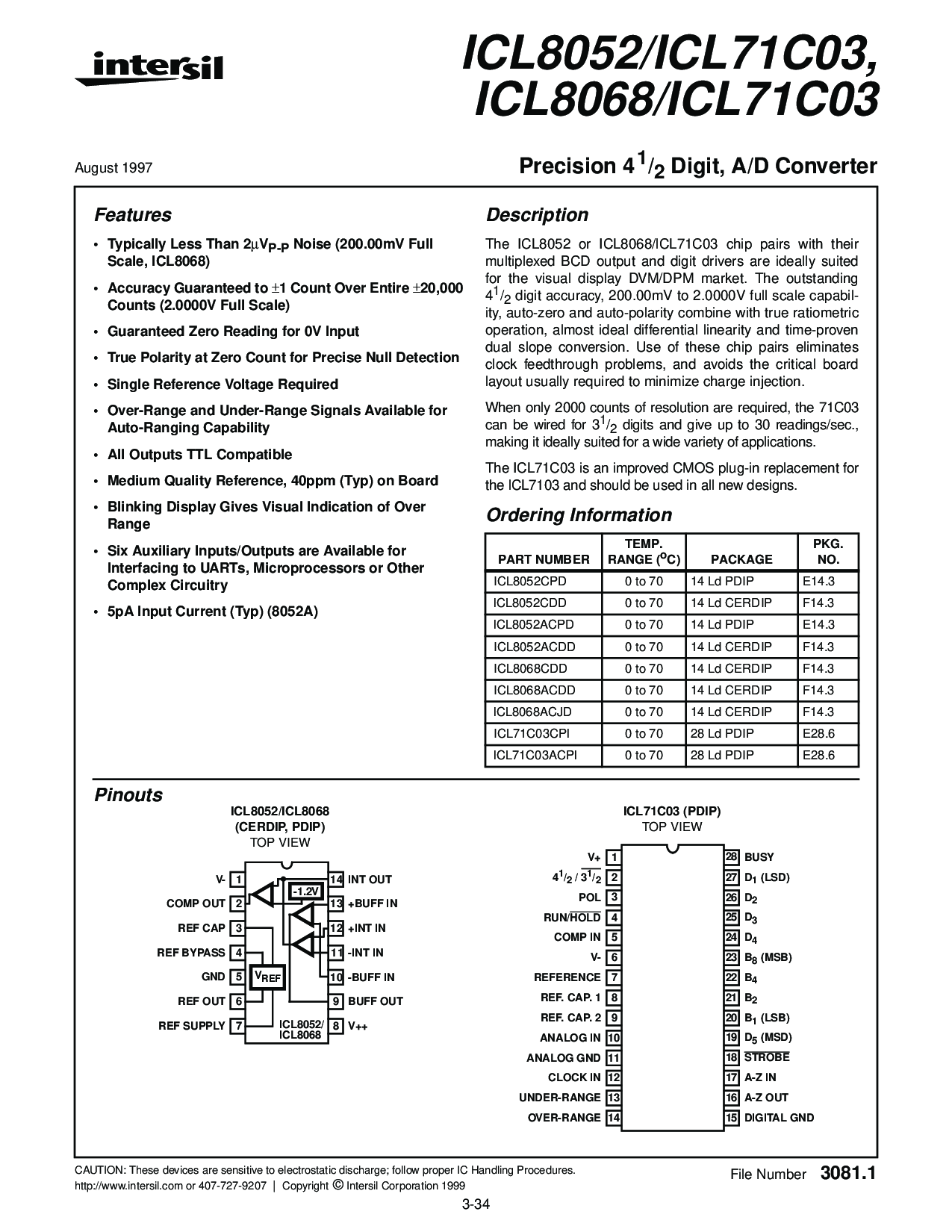

icl71c03 (pdip)

顶部 查看

v-

比较 出点

参考 盖

参考 旁路

地

参考 出点

参考 供应

智力 出点

+buff 入点

+int 入点

-智力 入点

-buff 入点

buff 出点

V++

1

2

3

4

5

6

7

14

13

12

11

10

9

8

-1.2v

v

参考

icl8052/

ICL8068

V+

4

1

/

2

/ 3

1

/

2

pol

运行/

保持

比较 入点

v-

参考

参考. 盖. 1

参考. 盖. 2

模拟 入点

模拟 地

时钟 入点

下-范围

超范围

忙

d

2

d

3

d

4

B

8

(msb)

B

2

d

5

(msd)

频闪

一个-z 入点

一个-z 出点

数字 地

d

1

(lsd)

B

4

B

1

(lsb)

28

27

26

25

24

23

22

21

20

19

18

17

16

15

1

2

3

4

5

6

7

8

9

10

11

12

13

14

8月 1997

icl8052/icl71c03,

icl8068/icl71c03

精度 4

1

/

2

数字, 一个/d 变频器

文件 号码

3081.1

注意事项: 这些 设备 是 敏感 至 静电 放电; 跟着 适当的 集成电路 搬运 程序.

http://www.intersil.com 或 407-727-9207

|

版权

©

intersil 公司 1999