www.latticesemi.com

1

clk5600_01

十一月 2004 初步 数据 工作表

© 2004 lattice 半导体 corp. 全部 lattice 商标, 已注册 商标, 专利, 和 免责声明 是 作为 已列出 在 www.latticesemi.com/legal. 全部 其他 品牌

或 产品 姓名 是 商标 或 已注册 商标 的 他们的 各自 持有人. 这 规格

fi

阳离子 和 信息 此处 是 主题 至 变更 无 通知.

ispclock 5600 家庭

在系统内 可编程, 零-延迟 时钟 发电机

与 通用 扇出 缓冲区

™

特点

■

10mhz 至 320mhz 输入/输出 操作

■

低 输出 至 输出 偏斜 (&指示灯;50ps)

■

低 抖动 峰峰值 (&指示灯;60ps)

■

向上 至 20 可编程 扇出 缓冲区

• 可编程 输出 标准 和 个人

启用 控件

-lvttl, lvcmos, hstl, sstl, lvds,

LVPECL

• 可编程 输出 阻抗

- 40 至 70

Ω

入点 5

Ω

增量

• 可编程 回转 费率

• 向上 至 10 银行 与 个人 v

CCO

和 地

- 1.5v, 1.8v, 2.5v, 3.3v

■

完全 综合 高性能 pll

• 可编程 锁 检测

• 相乘 和 除法 比率 受控 由

- 输入 分隔器 (5 比特)

-feedback 分隔器 (5 比特)

- 五个 输出 分隔器 (5 比特)

• 可编程 片上 回路 过滤器

■

精度 可编程 相位 调整

(偏斜) 按 输出

• 16 设置; 最小值 步骤 尺寸 195ps

- 已锁定 至 vco 频率

• 向上 至 +/- 12ns 偏斜 范围

• 粗 和

fi

ne 调整 模式

■

向上 至 五个 时钟 频率 域

■

灵活 时钟 参考 和 外部

反馈 输入

• 可编程 输入 标准

-lvttl, lvcmos, sstl, hstl, lvds,

LVPECL

• 时钟 一个/b 选择 多路复用器

•Feedback 一个/b 选择 多路复用器

• 可编程 终止

■

四 用户可编程 专业版

fi

莱斯 已存储 入点

e?

2

CMOS

®

记忆

• 支架 两者都有 测试一下 和 多个 操作

con

fi

测量

■

已满 jtag 边界 扫描 测试一下 在系统内

编程 支持

■

例外 电源 供应 噪声 免疫

■

商业 (0 至 70°c) 和 工业

(-40 至 85°c) 温度 范围

■

100-管脚 和 48-管脚 tqfp 软件包

■

应用程序

• 电路 板 普通 时钟 世代 和

分布

• pll-基于 频率 世代

• 高 扇出 时钟 缓冲区

• 零-延迟 时钟 缓冲区

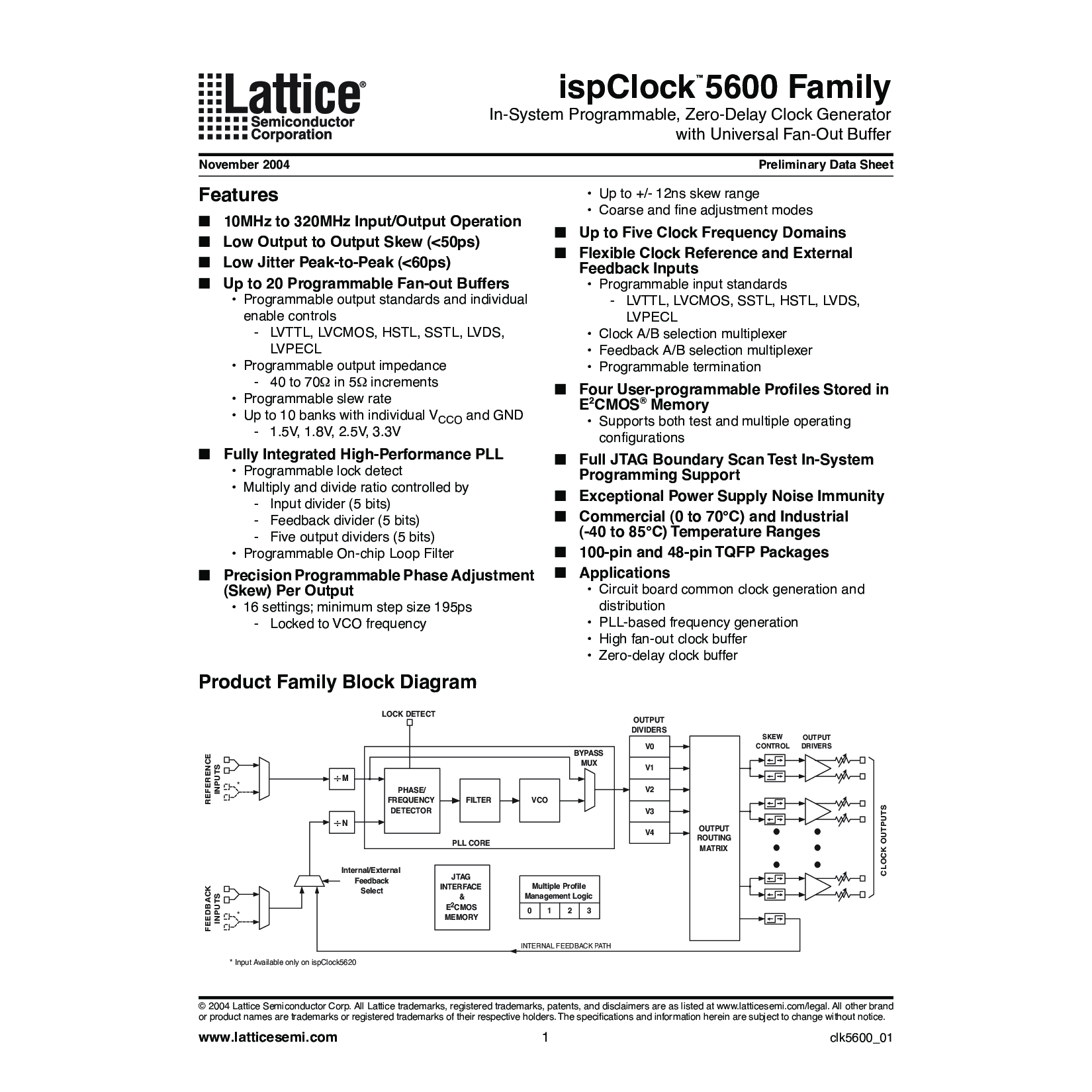

产品 家庭 块 图表

VCO

输出

驱动程序

偏斜

控制

时钟 产出

参考

inputs

JTAG

接口

&放大器;

e?

2

CMOS

记忆

锁 检测

过滤器

相位/

频率

检测器

1023

多个 配置文件

管理 逻辑

内部 反馈 路径

pll 核心

输出

routing

矩阵

V0

V1

V2

V3

V4

输出

分隔器

*

*

* 输入 可用 仅 开启 ispclock5620

旁路

mux

反馈

inputs

内部/外部

反馈

选择

m

n