Pentium

®

处理器 兼容

时钟 合成器/驾驶员

CY2254A

柏树 半导体 公司

•

3901 北 第一 街道

•

San Jose

•

ca 95134

•

408-943-2600

文件 #: 38-07203 rev. *a 修订 12月 14, 2002

4A

特点

• 多个 时钟 产出 至 满足 要求 的 大多数

Pentium

®

motherboards

—

四 引脚可选 cpu 时钟 @ 66.66 mhz, 60.0

mhz, 和 50.0 mhz 用于 支持 的 英特尔 triton

™

PCIset

基于 pc

—

55.0 mhz 引脚可选 cpu 时钟 也 可用 (

−

2

选项 仅)

—

六个 pci 时钟 在 1/2 cpu 时钟 频率

—

一个 我/o 时钟 @ 24 mhz

—

一个 键盘 控制器 时钟 @ 12 mhz (

−

1 选项)

或 一个 通用 串行 总线 时钟 @ 48 mhz

(

−

2 选项)

—

两个 参考. 时钟 @ 14.318 mhz

—

参考. 14.318 mhz xtal 振荡器 输入

•

cpu 时钟 抖动 &指示灯;

200 ps 循环到循环

•

低 偏斜 产出

—

&指示灯;

250 ps 之间 cpu 时钟

—

&指示灯;250 ps 之间 pci 时钟

—

&指示灯;

500 ps 之间 cpu 和 pci 时钟 (

−

2 选项)

—

cpu 时钟 导联 pci 时钟 由 +1 ns 最小值 至 +4 ns

最大值 (

−

1 选项)

•

频率. 稳定性 = 0.01% (最大值.)

•

输出 职责 循环 45% 最小值 至 55% 最大值

•

测试一下 模式 支持 (

−

1 选项 仅)

•

3.3v 或 5.0v 操作

•

内部 上拉 电阻 开启 s0, s1, 和 oe 输入

功能 描述

这 cy2254a 是 一个 时钟 合成器/驾驶员 那 提供 这

多个 时钟 必填项 用于 一个 pentium-基于 pc. 这

cy2254a 有 低偏斜 产出 (&指示灯;

250 ps 之间 这 cpu

时钟, &指示灯;

250 ps 之间 这 pci 时钟). 入点 加法, 这

cy2254a cpu 时钟 产出 有 较少 比 200 ps cy-

cle-至-循环 抖动. 最后, 两者都有 这 pci 和 cpu 时钟 产出

满足 这 1 v/ns 回转 费率 要求 的 一个 pentium 进程-

sor-基于 系统.

这 cy2254a 接受 一个 14.318 mhz 参考 信号 作为 其

输入. 这 cy2254a 有 2 plls, 一个 的 哪个 生成 这

cpu 和 pci 时钟, 和 这 其他 生成 这 我/o 和 钥匙-

板 控制器 或 usb 时钟. 这 cy2254a 运行 关 要么

一个 3.3v 或 5v 供应.

这 cy2254a 是 可用 入点 两个 选项. 这

−

1 选项 sup-

端口 这 英特尔 triton pciset 和 提供 一个 12 mhz 键盘

时钟 开启 管脚 25. 这

−

2 选项 提供 一个 48 mhz usb 时钟

开启 管脚 25 和 支架 这 cyrix

®

m1 处理器.

英特尔 和 pentium 是 已注册 商标 的 英特尔 公司.

triton 是 一个 商标 的 英特尔 公司.

cyrix 是 一个 已注册 商标 的 cyrix 公司.

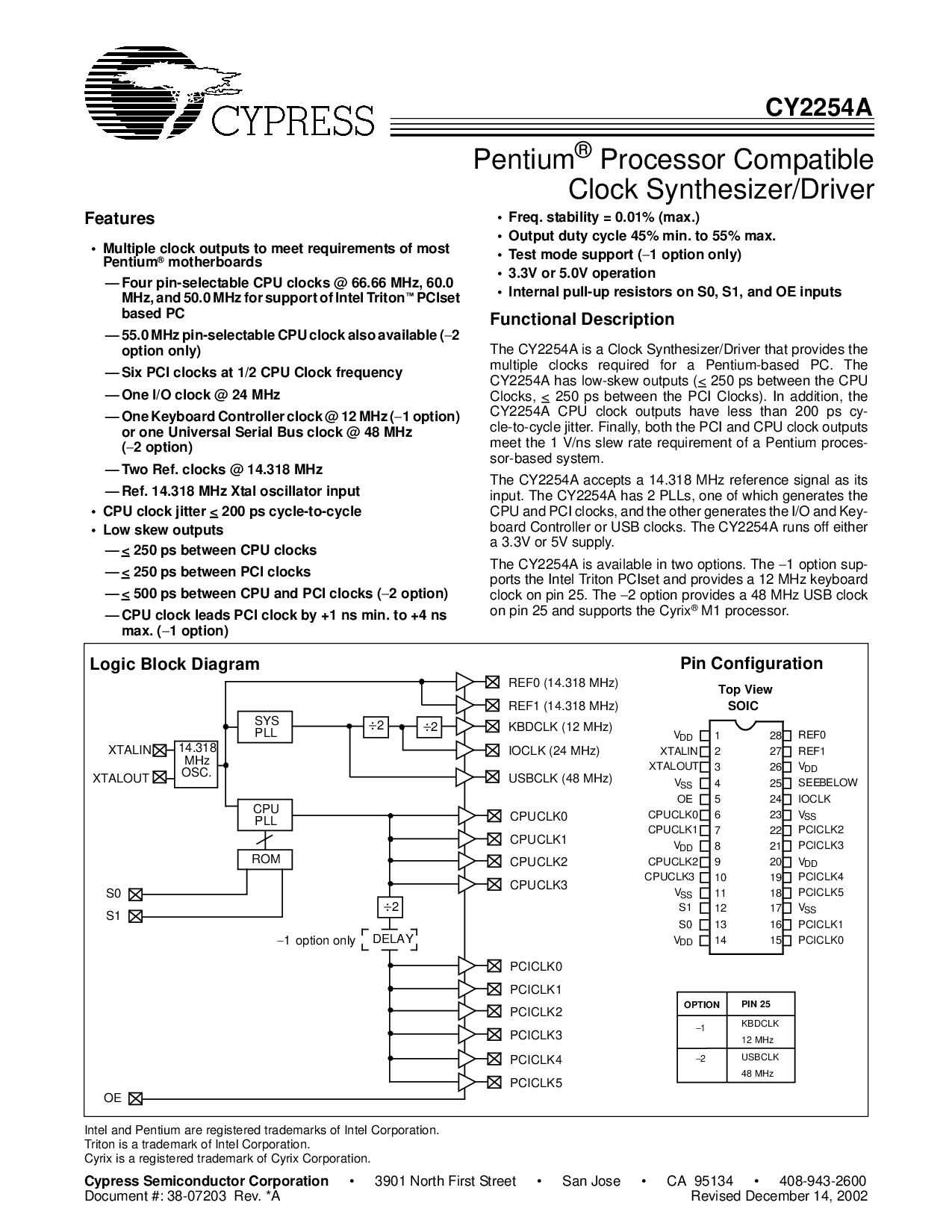

管脚 配置

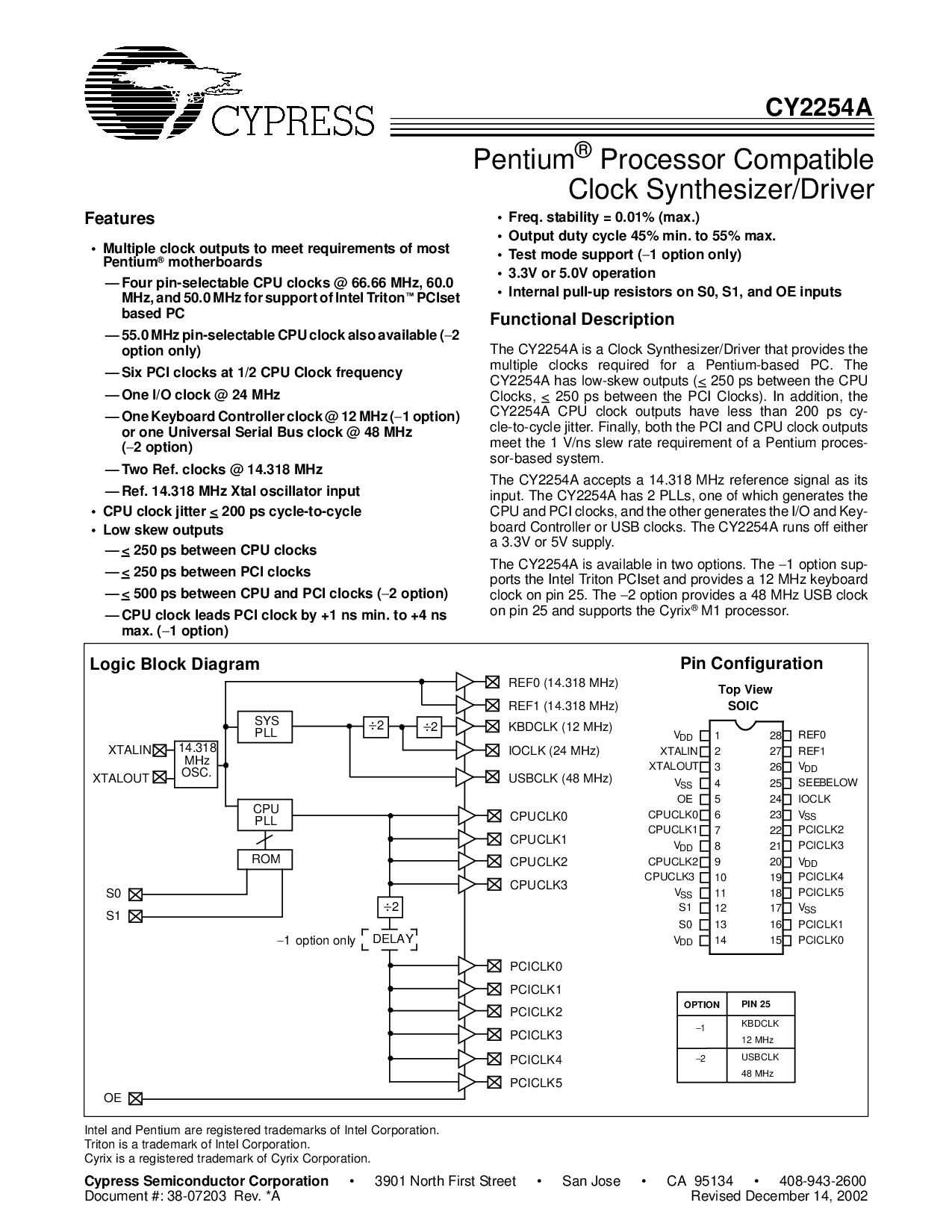

逻辑 块 图表

XTALOUT

XTALIN

ref0 (14.318 mhz)

14.318

MHz

osc.

1

2

3

4

5

6

7

8

9

10

11

12

15

16

17

18

19

20

24

23

22

21

13

14

25

28

27

26

顶部 查看

v

dd

XTALIN

XTALOUT

v

ss

oe

CPUCLK0

CPUCLK1

v

dd

CPUCLK2

CPUCLK3

v

ss

S1

S0

v

dd

REF0

REF1

v

dd

SEEBELOW

IOCLK

v

ss

PCICLK2

PCICLK3

v

dd

PCICLK4

PCICLK5

v

ss

PCICLK1

PCICLK0

ref1 (14.318 mhz)

ioclk (24 mhz)

CPUCLK0

CPUCLK1

CPUCLK2

CPUCLK3

PCICLK0

系统

PLL

CPU

PLL

rom

S0

S1

oe

÷

2

延迟

PCICLK1

PCICLK2

PCICLK3

PCICLK4

PCICLK5

SOIC

usbclk (48 mhz)

kbdclk (12 mhz)

÷

2

÷

2

−

1

−

2

选项

管脚 25

KBDCLK

12 MHz

USBCLK

48 MHz

−

1 选项 仅