eroflex 电路 技术 - 高级 多芯片 模块 © scd3369-1 rev c 5/31/00

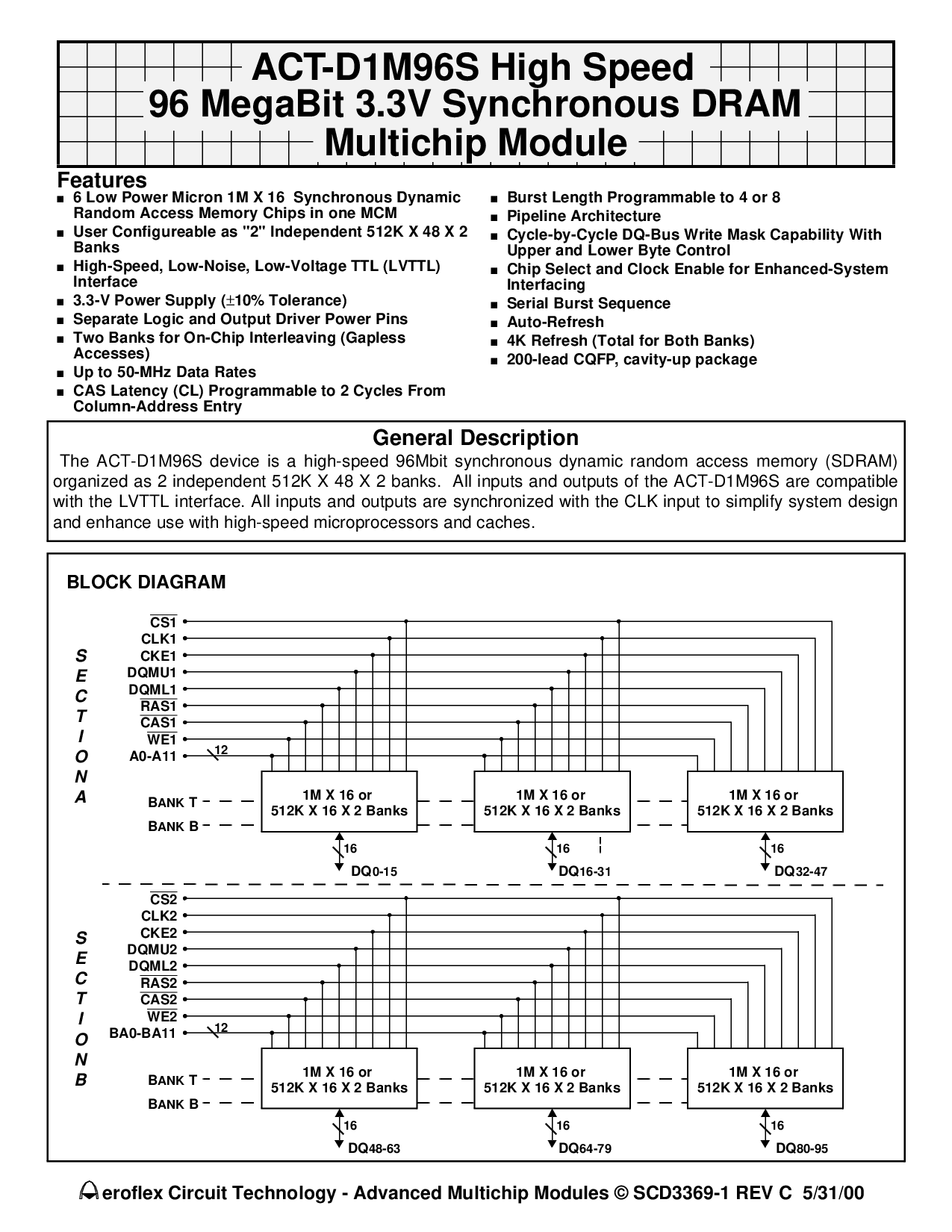

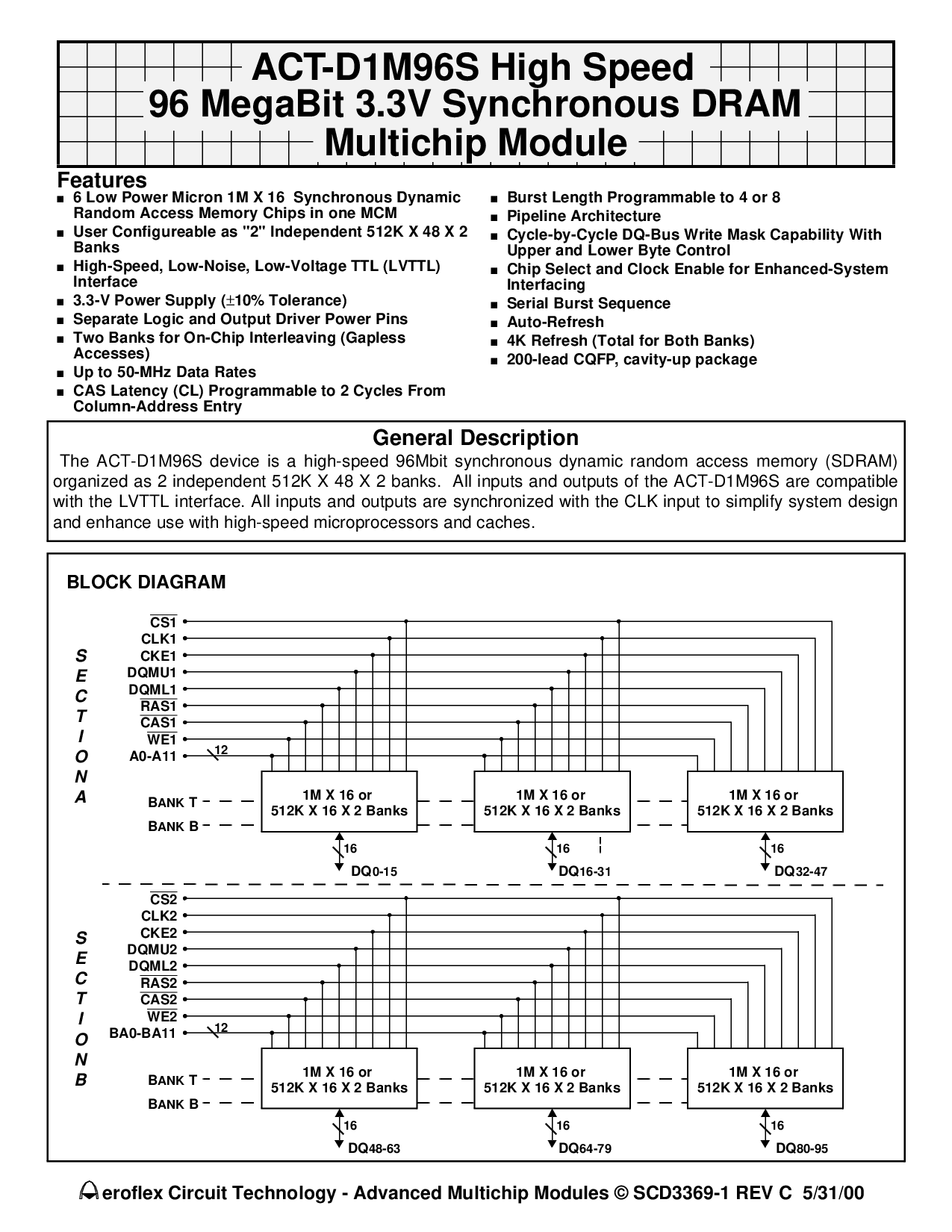

块 图表

■

6 低 电源 微米 1m x 16 同步 动态

随机 访问权限 记忆 芯片 入点 一个 mcm

■

用户 configureable 作为 "2" 独立 512k x 48 x 2

银行

■

高-速度, 低-噪声, 低电压 ttl (lvttl)

接口

■

3.3-v 电源 供应 (

±

10% 公差)

■

分开 逻辑 和 输出 驾驶员 电源 针脚

■

两个 银行 用于 片上 交错 (无间隙

访问权限)

■

向上 至 50-mhz 数据 费率

■

cas 延迟 (cl) 可编程 至 2 循环次数 从

列地址 进入

■

突发 长度 可编程 至 4 或 8

■

管道 体系结构

■

逐周期 dq-总线 写 面具 能力 与

上部 和 下部 字节 控制

■

芯片 选择 和 时钟 启用 用于 增强型-系统

接口

■

串行 突发 顺序

■

自动刷新

■

4k 刷新 (合计 用于 两者都有 银行)

■

200-铅 cqfp, 空腔-向上 包装

交流电t-d1m96s 高 速度

多芯片 模块

特点

概述 描述

这 act-d1m96s 设备 是 一个 高速 96mbit 同步 动态 随机 访问权限 记忆 (sdram)

有组织的 作为 2 独立 512k x 48 x 2 银行. 全部 输入 和 产出 的 这 act-d1m96s 是 兼容

与 这 lvttl 接口. 全部 输入 和 产出 是 已同步 与 这 clk 输入 至 简化 系统 设计

和 增强 使用 与 高速 微处理器 和 缓存.

96 兆位 3.3v 同步 dram

B

ank

B

DQ

16-31

16

DQ

0-15

DQ

32-47

CS1

CLK1

CKE1

DQMU1

DQML1

RAS1

CAS1

WE1

a0-a11

1616

DQ

64-79

16

DQ

48-63

DQ

80-95

CS2

CLK2

CKE2

DQMU2

DQML2

RAS2

CAS2

WE2

ba0-ba11

1616

B

ank

t

1m x 16 或

512k x 16 x 2 银行

1m x 16 或

512k x 16 x 2 银行

1m x 16 或

512k x 16 x 2 银行

B

ank

B

B

ank

t

1m x 16 或

512k x 16 x 2 银行

1m x 16 或

512k x 16 x 2 银行

1m x 16 或

512k x 16 x 2 银行

12

12

s

e?

c

t

我

o

n

一个

s

e?

c

t

我

o

n

B