rev. 0

信息 提供的 由 模拟 设备 是 相信 至 是 准确 和

可靠. 然而, 否 责任 是 假设 由 模拟 设备 用于 其

使用, 也没有 用于 任何 侵权 的 专利 或 其他 权利 的 第三 缔约方

哪个 将 结果 从 其 使用. 否 许可证 是 授予 由 蕴涵 或

否则 下 任何 专利 或 专利 权利 的 模拟 设备.

一个

ad5332/ad5333/ad5342/ad5343

*

一个 技术 方式, p.o. 框 9106, norwood, ma 02062-9106, 美国

电话: 781/329-4700 世界 宽 web 现场: http://www.模拟.com

传真: 781/326-8703 © 模拟 设备, 股份有限公司., 2000

2.5 v 至 5.5 v, 230

一个, 平行 接口

双 电压-输出 8-/10-/12-有点 dacs

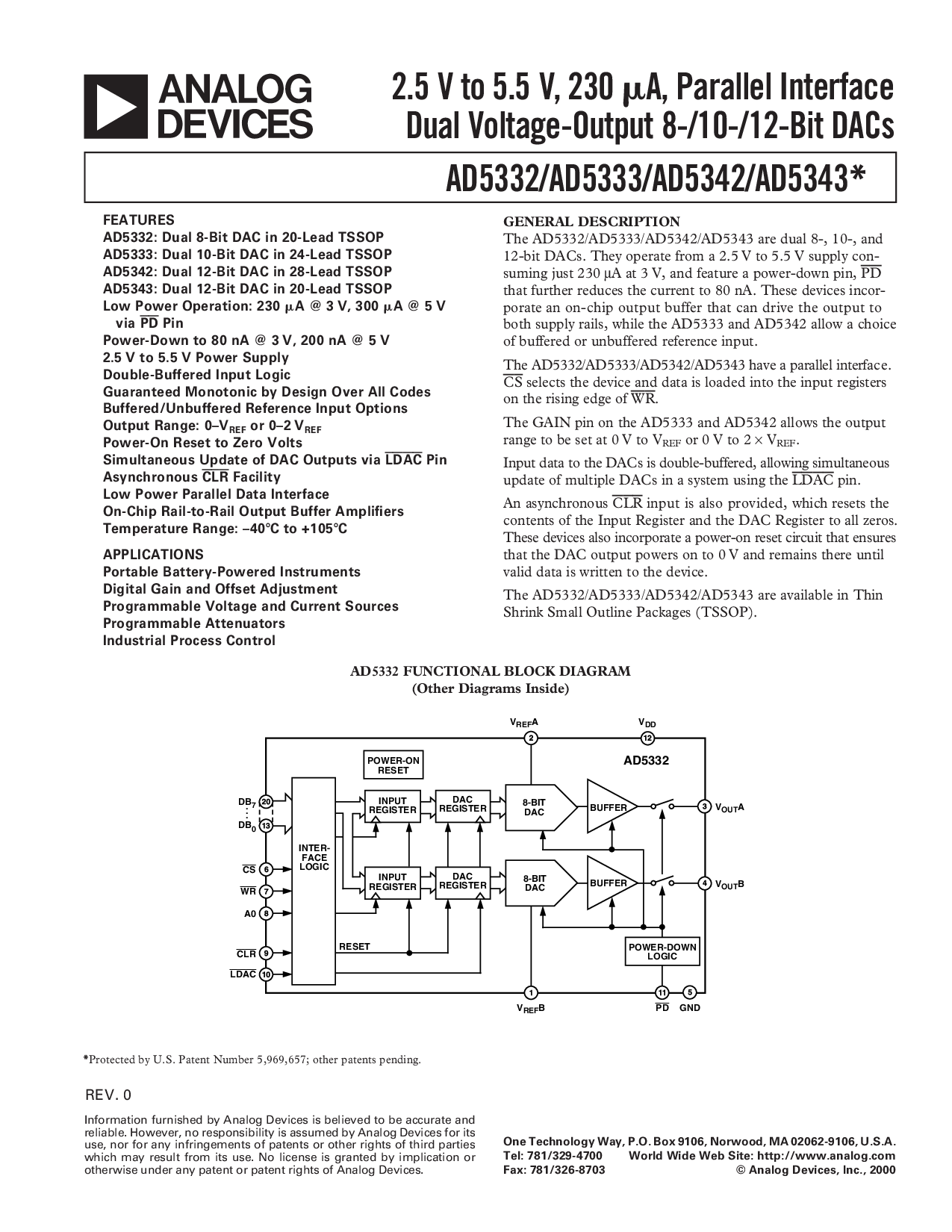

ad5332 功能 块 图表

(其他 图表 内部)

通电

重置

dac

注册

dac

注册

输入

注册

输入

注册

国际米兰-

面部

逻辑

db

7

db

0

cs

wr

A0

clr

LDAC

.

.

.

v

参考

一个

重置

v

参考

B

v

出点

一个

缓冲区

AD5332

v

出点

B

缓冲区

v

dd

掉电

逻辑

pd

地

8-有点

dac

8-有点

dac

特点

ad5332: 双 8-有点 dac 入点 20-铅 tssop

ad5333: 双 10-有点 dac 入点 24-铅 tssop

ad5342: 双 12-有点 dac 入点 28-铅 tssop

ad5343: 双 12-有点 dac 入点 20-铅 tssop

低 电源 操作: 230

一个 @ 3 v, 300

一个 @ 5 v

通过

pd

管脚

掉电 至 80 不适用 @ 3 v, 200 不适用 @ 5 v

2.5 v 至 5.5 v 电源 供应

双缓冲 输入 逻辑

保证 单调 由 设计 结束 全部 代码

缓冲/无缓冲 参考 输入 选项

输出 范围: 0–v

参考

或 0–2 v

参考

通电 重置 至 零 伏特

同时 更新 的 dac 产出 通过

LDAC

管脚

异步

clr

设施

低 电源 平行 数据 接口

片上 轨到轨 输出 缓冲区 放大器

温度 范围: –40

c 至 +105

c

应用程序

便携式 电池供电 仪器仪表

数字 增益 和 偏移量 调整

可编程 电压 和 电流 来源

可编程 衰减器

工业 流程 控制

概述 描述

这 ad5332/ad5333/ad5342/ad5343 是 双 8-, 10-, 和

12-有点 dacs. 他们 操作 从 一个 2.5 v 至 5.5 v 供应 con-

suming 只是 230

µ

一个 在 3 v, 和 功能 一个 掉电 管脚,

pd

那 进一步 减少 这 电流 至 80 不适用. 这些 设备 incor-

porate 一个 开启-芯片 输出 缓冲区 那 可以 驱动器 这 输出 至

两者都有 供应 铁轨, 同时 这 ad5333 和 ad5342 允许 一个 选择

的 缓冲 或 无缓冲 参考 输入.

这 ad5332/ad5333/ad5342/ad5343 有 一个 平行 接口.

cs

选择 这 设备 和 数据 是 已加载 进入 这 输入 寄存器

开启 这 上升 边缘 的

wr

.

这 增益 管脚 开启 这 ad5333 和 ad5342 允许 这 输出

范围 至 是 设置 在 0 v 至 v

参考

或 0 v 至 2

×

v

参考

.

输入 数据 至 这 dacs 是 双-缓冲, 允许 同时

更新 的 多个 dacs 入点 一个 系统 使用 这

LDAC

管脚.

一个 异步

clr

输入 是 也 提供,哪个 重置 这

内容 的 这 输入 注册 和 这 dac 注册 至 全部 零.

这些 设备 也 合并 一个 通电 重置 电路 那 确保

那 这 dac 输出 权力 开启 至 0 v 和 遗迹 那里 直到

有效 数据 是 书面 至 这 设备.

这 ad5332/ad5333/ad5342/ad5343 是 可用 入点 薄

收缩 小 大纲 软件包 (tssop).

*

保护 由 u.s. 专利 号码 5,969,657; 其他 专利 待定.