14-有点, 80 msps, 一个/d 变频器

AD9444

rev.

0

信息 提供的 由 模拟 设备 是相信 至 是 准确 和 可靠.

然而, 否 责任 是 假设 由 模拟 设备 用于 其 使用, 也没有 用于 任何

侵权 的 专利 或 其他 权利 的第三 缔约方 那 将 结果 从 其 使用.

规格 主题 至 变更 无 通知. 否 许可证 是 授予 由 蕴涵

或 否则 下 任何 专利 或 专利 ri干旱 的 模拟 设备. 商标 和

已注册 商标 是 这 财产 的 他们的 各自 业主.

一个 技术 方式, p.o. 框 9106,norwood, ma 02062-9106, 美国

电话: 781.329.4700

www.模拟.com

传真: 781.326.8703 © 2004 模拟 设备, 公司 全部 权利 保留.

特点

80 msps 保证 取样 费率

100 db 双音 sfdr 与 69.3 mhz 和 70.3 mhz

73.1 db snr 与 70 mhz 输入

97 dbc sfdr 与 70 mhz 输入

优秀 线性度

dnl = ±0.4 lsb 典型

inl = ±0.6 lsb 典型

1.2 w 电源 耗散

3.3 v 和 5 v 供应 操作

2.0 v p-p 差速器 满量程 输入

lvds 产出 (ansi-644 兼容)

数据 格式 选择

输出 时钟 可用

应用程序

多载波, 多模 细胞 接收器

天线 阵列 定位

电源 放大器 线性化

宽带 无线

雷达, infared 成像

通信 仪器仪表

概述 描述

这 ad9444 是 一个 14-有点 单片, 取样 模数转换

变频器 (adc) 与 一个 开启-芯片, 跟踪和保持 电路 和 是

优化 用于 电源, 小 尺寸, 和 轻松 的 使用. 这 产品

操作 在 向上 至 一个 80 msps 换算 费率 和 是 优化

用于 多载波, 多模 接收器, 这样的 作为 那些 已找到 入点

细胞 基础设施 设备.

这 adc 需要 3.3 v 和 5.0 v 电源 供应品 和 一个 低

电压 差速器 输入 时钟 用于 已满 业绩 操作.

否 外部 参考 或 驾驶员 组件 是 必填项 用于

许多 应用程序. 数据 产出 是 lvds-兼容 (ansi-

644) 或 cmos-兼容 和 包括 这 手段 至 减少

这 总体 电流 需要 用于 短 跟踪 距离.

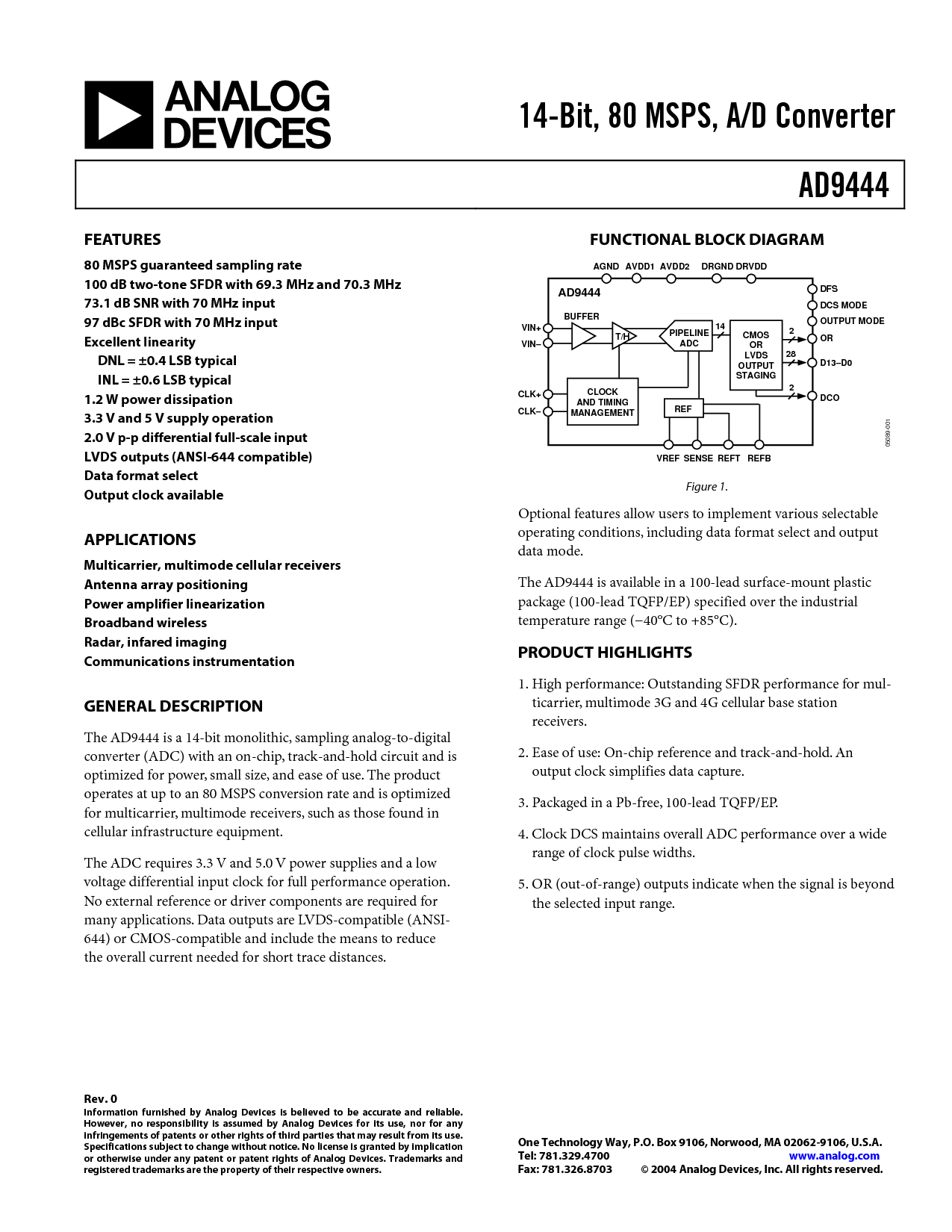

功能 块 图表

CMOS

或

LVDS

输出

STAGING

时钟

和 计时

管理

AGND DRGND DRVDD

VREF

CLK+

VIN+

AD9444

VIN–

CLK–

DCO

05089-001

AVDD1 AVDD2

dcs 模式

DFS

输出 模式

t/h

缓冲区

14

管道

adc

2

28

2

或

D13–D0

参考

REFBSENSE REFT

图 1.

可选 特点 允许 用户 至 实施 各种 可选择

操作 条件, 包括 数据 格式 选择 和 输出

数据 模式.

这 ad9444 是 可用 入点 一个 100-铅 表面贴装 塑料

包装 (100-铅 tqfp/ep) 指定 结束 这 工业

温度 范围 (−40°c 至 +85°c).

产品 亮点

1.

高 业绩: 未结清 sfdr 业绩 用于 mul-

ticarrier, 多模 3g 和 4g 细胞 底座 车站

接收器.

2.

轻松 的 使用: 片上 参考 和 轨道-和-保持. 一个

输出 时钟 简化了 数据 捕获.

3.

已打包 入点 一个 铅-免费, 100-铅 tqfp/ep.

4.

时钟 dcs 维护 总体 adc 业绩 结束 一个 宽

范围 的 时钟 脉冲 宽度.

5.

或 (出点-的-范围) 产出 指示 当 这 信号 是 超越

这 已选择 输入 范围.