rev. 0

信息 提供的 由 模拟 设备 是 相信 至 是 准确 和

可靠. 然而, 否 责任 是 假设 由 模拟 设备 用于 其

使用, 也没有 用于 任何 侵权 的 专利 或 其他 权利 的 第三 缔约方

哪个 将 结果 从 其 使用. 否 许可证 是 授予 由 蕴涵 或

否则 下 任何 专利 或 专利 权利 的 模拟 设备.

一个

AD9772

一个 技术 方式, p.o. 框 9106, norwood, ma 02062-9106, 美国

电话: 781/329-4700 世界 宽 web 现场: http://www.模拟.com

传真: 781/326-8703 © 模拟 设备, 股份有限公司., 1999

14-有点, 150 msps txdac+

™

与 2

插值 过滤器

特点

单独 2.7 v 至 3.6 v 供应

14-有点 dac 分辨率 和 输入 数据 宽度

150 msps 输入 数据 费率

63.3 mhz 重建 通带 @ 150 msps

75 dbc sfdr @ 25 mhz

2

插值 过滤器 与 高 或 低 通过 响应

73 db 图像 拒收 与 0.005 db通带 波纹

“zero-stuffing” 选项 用于 增强型 直接 如果

业绩

内部 2

/4

时钟 乘数

205 mw 电源 耗散; 13 mw 与 掉电

模式

48-铅 lqfp 包装

应用程序

通信 发送 频道

wcdma 底座 车站, 多载波 底座 车站,

直接 如果 合成

仪器仪表

产品 描述

这 ad9772 是 一个 单独 供应, 过采样, 14-有点 数字-至-

模拟 变频器 (dac) 优化 用于 基带 或 如果 波形

重建 应用程序 要求 例外 动态 范围.

已制造 开启 一个 高级 cmos 流程, 它 集成 一个

完成, 低 失真 14-有点 dac 与 一个 2

×

数字 interpola-

操作 过滤器 和 时钟 乘数. 这 片上 pll 时钟 多-

钳子 provides 全部 这 必要的 时钟 用于 这 数字 过滤器 和 这

14-有点 dac. 一个 灵活 差速器 时钟 输入 允许 用于 一个 单独-

已结束 或 差速器时钟 驾驶员 用于 最佳 抖动 业绩.

用于 基带 应用程序, 这 2

×

数字 插值 过滤器

提供 一个 低 通过 响应, 因此 提供 向上 至 一个 三个-fold

减少 入点 这 复杂性 的 这 模拟 重建 过滤器. 它

是否 所以 由 乘法 这 输入 数据 费率 由 一个 因素 的 两个

同时 同时 抑制 这 原件 上部 inband

图像 由 更多 比 73 db. 用于 直接 如果 应用程序, 这 2

×

数字 插值 过滤器 响应 可以 是 重新配置 至 选择

这 上部 inband 图像 (我.e?., 高 通过 响应) 同时 sup-

按压 这 原件 基带 图像. 至 增加 这 信号

水平 的 这 较高 如果 图像 和 他们的 通带 平整度 入点 di-

矩形 如果 应用程序, 这 ad9772 也 特点 一个 “zero stuffing”

选项 入点哪个 这 数据 以下内容 这 2

×

插值 过滤器 是

上采样 由 一个因素 的 两个 由 插入 中档 数据 样品.

这 ad9772 可以 重建 满量程 波形 与 乐队-

宽度 作为 高 作为 63.3 mhz 同时 操作 在 一个 输入 数据 费率 的

150 msps. 这 14-有点 dac 提供 差速器 电流 出点-

看跌期权 至 支持 差速器 或 单端 应用程序. 一个

seg已结成 电流 来源 体系结构 是 合并 与 一个具有-

电子 开关 技术 至 减少 杂散 组件 和

增强 动态 业绩. 匹配 之间 这 两个

电流 产出 确保 增强型 动态 业绩 入点 一个

差速器 输出 配置. 这 差速器 电流 出点-

看跌期权 将 是 美联储 进入 一个 变压器 或 一个 差速器 op 放大器

拓扑 至 获取 一个 单端 输出 电压 使用 一个 ap-

适当的 电阻 荷载.

这 片上 带隙 参考 和 控制 放大器 是 配置-

已确定 用于 最大值 准确度 和 灵活性. 这 ad9772 可以 是

驱动 由 这 片上 参考 或 由 一个 品种 的 外部 参考-

ence 电压. 这 满量程 电流 的 这 ad9772 可以 是

已调整 结束 一个 2 ma 至 20 ma 范围, 因此 提供 附加

增益 测距 能力.

这 ad9772 是 可用 入点 一个 48-铅 lqfp 包装 和 规格-

已确定 用于 操作 结束 这 工业 温度 范围 的 –40

°

c

至 +85

°

c.

产品 亮点

1. 一个 灵活, 低 电源 2

×

插值 过滤器 支撑 re-

施工 带宽 的 向上 至 63.3 mhz 可以 是 配置-

已确定 用于 一个 低 或 高 通过 响应 与 73 db 的 图像

拒收 用于 传统 基带 或 直接 如果 应用程序.

2. 一个 “zero-stuffing” 选项 增强 直接 如果 应用程序.

3. 一个 低 毛刺, 快 沉降 14-有点 dac 提供 例外

动态 范围 用于 两者都有 基带 和 直接 如果 waveform

重建 应用程序.

4. 这 ad9772 数字 接口, 由 的 边沿触发

锁扣 和 一个 灵活 差速器 或 单端 时钟 输入,

可以 支持 输入 数据 费率 向上 至 150 msps.

5. 片上pll 时钟 乘数 生成 全部 的 这 内部 高

速度 时钟 必填项 由这 插值 过滤器 和 dac.

6. 这 电流 输出(s) 的 这 ad9772 可以 很容易 是 已配置

用于 各种 单端 或 差速器 电路 拓扑.

txdac+ 是 一个 商标 的 模拟 设备, 公司

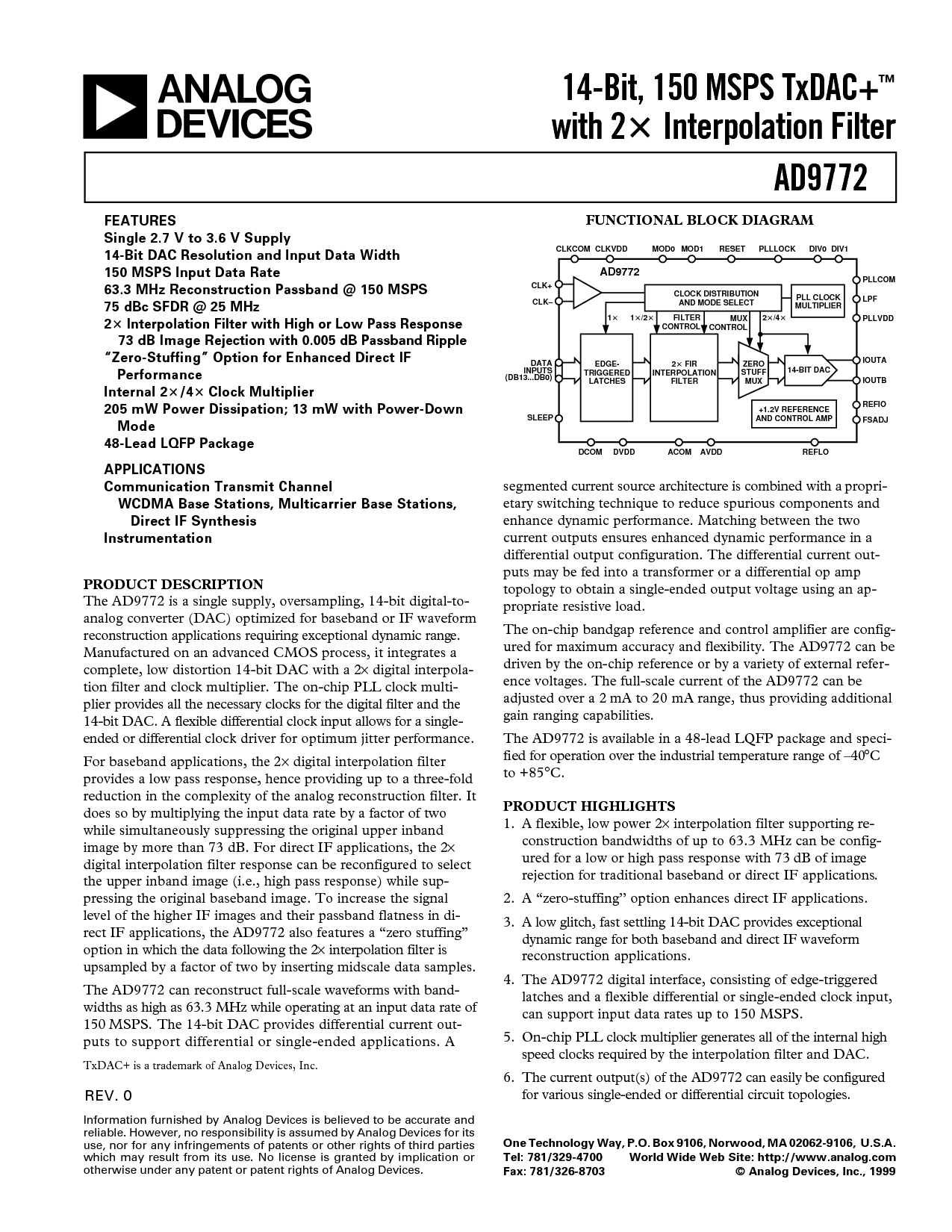

功能 块 图表

14-有点 dac

零

东西

mux

2

FIR

插值

过滤器

边缘-

已触发

锁扣

时钟 分布

和 模式 选择

2

/4

mux

控制

过滤器

控制

1

/2

1

pll 时钟

乘数

+1.2v 参考

和 控制 放大器

AD9772

CLKCOM CLKVDD MOD0 MOD1 重置 PLLLOCK DIV0 DIV1

CLK+

CLK–

数据

输入

(db13...db0)

睡眠

DCOM DVDD ACOM AVDD REFLO

PLLCOM

LPF

PLLVDD

IOUTA

IOUTB

REFIO

FSADJ