ispLSI

®

3256E

在系统内 可编程 高 密度 pld

3256e_08

1

特点

• 高密度 可编程 逻辑

— 256 我/o 针脚

— 12000 pld 盖茨

— 512 寄存器

— 高 速度 全球 互连

— 宽 输入 浇口 用于 快 计数器, 州

机器, 地址 解码器, 等

— 小 逻辑 块 尺寸 用于 随机 逻辑

• 高 业绩 e?

2

CMOS

®

技术

—

f

最大值

= 100 mhz 最大值 操作 频率

—

t

pd

= 10 ns 传播 延迟

— ttl 兼容 输入 和 产出

— 电气 可擦除 和 可重新编程

— 非挥发性

— 100% 已测试 在 时间 的 制造

— 未使用 产品 期限 停机 保存 电源

• 在系统内 可编程

— 5v 在系统内 可编程 (isp™) 使用 lattice

isp 或 边界 扫描 测试一下 (ieee 1149.1) 协议

— 增加 制造业 收益率, 减少 时间-至-

市场, 和 改进 产品 质量

— 重新编程 焊接 设备 用于 更快 调试

• 100% ieee 1149.1 边界 扫描 兼容

• 优惠 这 轻松 的 使用 和 快 系统

速度 的 plds 与 这 密度 和 灵活性

的 字段 可编程 闸门 阵列

— 完成 可编程 设备 可以 联合收割机 胶水

逻辑 和 结构化 设计

— 五个 专用 时钟 输入 针脚

— 同步 和 异步 时钟

— 可编程 输出 回转 费率 控制 至 迷你-

米泽 开关 噪声

— 灵活 管脚 放置位置

— 优化 全球 路由 游泳池 提供 全球

Interconnectivity

• ispdesignexpert™ – 逻辑 编译器 和 com-

完整 isp 设备 设计 系统 从 hdl

合成 通过 在系统内 编程

— 上级 质量 的 结果

— 紧紧地 综合 与 领先 cae 供应商 工具

— productivity 增强 计时 分析仪, explore

工具, 计时 模拟器 和 ispanalyzer™

— pc 和 unix platforms

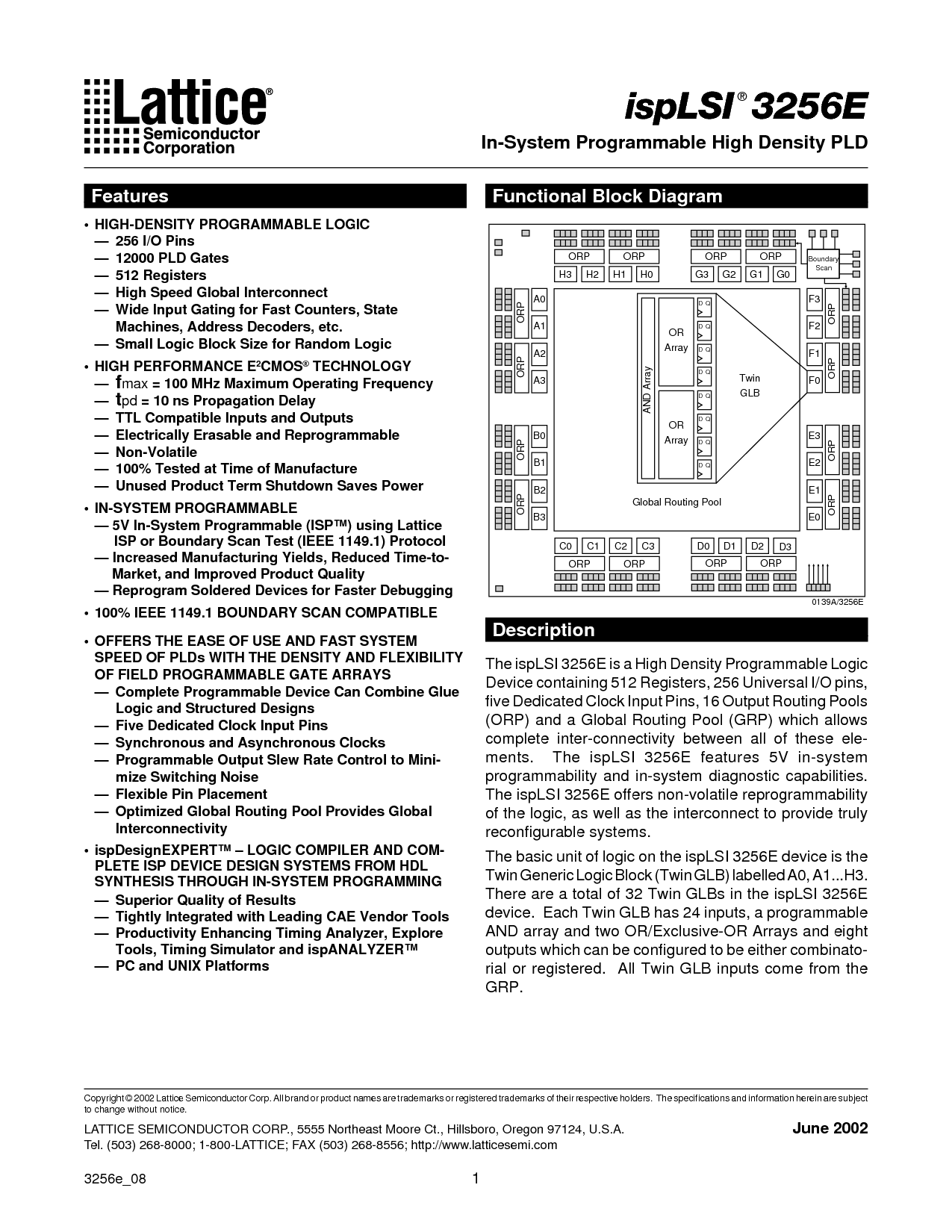

功能 块 图表

C0 C1 C2 C3

ORP

ORP

全球 路由 游泳池

ORP

D0

D1 D2

D3

H3 H2 H1 H0

G3

G2 G1 G0

B0

B1

B2

B3

边界

扫描

或

阵列

DQ

DQ

DQ

DQ

双胞胎

GLB

或

阵列

DQ

DQ

DQ

DQ

和 阵列

ORP

A0

A1

A2

A3

E3

E2

E1

E0

F3

F2

F1

F0

0139a/3256e

ORP

ORP

ORP

ORP

ORP

ORP

ORP ORP

ORP ORP

ORP ORP

描述

这 isplsi 3256e 是 一个 高 密度 可编程 逻辑

设备 包含 512 寄存器, 256 通用 我/o 针脚,

五个 专用 时钟 输入 针脚, 16 输出 路由 pools

(orp) 和 一个 全球 路由 游泳池 (grp) 哪个 允许

完成 国际米兰-连通性 之间 全部 的 这些 电子乐-

部分. 这 isplsi 3256e 特点 5v 在系统内

可编程性 和 在系统内 诊断 能力.

这 isplsi 3256e 优惠 非挥发性 可重新编程性

的 这 逻辑, 作为 井 作为 这 互连 至 提供 真的

可重构 系统.

这 基本 单位 的 逻辑 开启 这 isplsi 3256e 设备 是 这

双胞胎 通用 逻辑 块 (双胞胎 glb) 已标记 a0, a1...h3.

那里 是 一个 合计 的 32 双胞胎 glbs 入点 这 isplsi 3256e

设备. 每个 双胞胎 glb 有 24 输入, 一个 可编程

和 阵列 和 两个 或/独占-或 阵列 和 八

产出 哪个 可以 是 已配置 至 是 要么 组合-

里亚尔 或 已注册. 全部 双胞胎 glb 输入 来 从 这

grp.

版权 © 2002 lattice 半导体 corp. 全部 品牌 或 产品 姓名 是 商标 或 已注册 商标 的 他们的 分别活动 持有人. 这 规格 和 信息 此处 是 主题

至 变更 无 通知.

lattice 半导体 corp., 5555 northeast moore ct., hillsboro, oregon 97124, 美国

六月 2002

tel. (503) 268-8000; 1-800-lattice; 传真 (503) 268-8556; http://www.latticesemi.com