文件 否. e0443e40 (ver. 4.0)

日期 已发布 october 2005 (k) 日本

已打印 入点 日本

url: http://www.elpida.com

elpida 记忆, 公司 2003-2005

数据 工作表

128m 比特 ddr sdram

edd1216aata-5 (8m 字词

×

16 比特, ddr400)

描述

这 edd1216aata 是 一个 128m 比特 双 数据 费率

(ddr) sdram 有组织的 作为 2,097,154 字词

×

16 比特

×

4 银行. 阅读 和 写 o性能 是 执行 在

这 十字形 点数 的 这 ck 和 这 /ck. 这个 高-

速度 数据 转让 是 realized 由 这 2 比特 预取-

流水线 体系结构. 数据 频闪 (dqs) 两者都有 用于

阅读 和 写 是 可用 用于 高 速度 和 可靠

数据 总线 设计. 由 设置 扩展 模式 注册,

这 片上 延迟 已锁定 回路 (dll) 可以 是 设置

启用 或 禁用. 它 是 已打包 入点 66-管脚 塑料

tsop (二).

特点

•

电源 供应: vdd ,vddq = 2.6v

±

0.1v

•

数据 费率: 400mbps (最大值.)

•

双 数据 费率体系结构; 两个 数据 转让 按

时钟 循环

•

bi-定向, 数据 频闪 (dqs) 是 已传输

/已收到 与 数据, 至 是已使用 入点 捕获 数据 在

这 接收器

•

数据 输入, 产出, 和dm 是 已同步 与

DQS

•

4 内部 银行 用于 并发 操作

•

dqs 是 边缘 对齐 与 数据 用于 读取; 中心

对齐 与 数据 用于 写入

•

差速器 时钟 输入 (ck 和 /ck)

•

dll 对齐 dq 和 dqs 过渡 与 ck

过渡

•

命令 已输入 开启 每个 正 ck 边缘; 数据

和 数据 面具 引用 至 两者都有 边缘 的 dqs

•

数据 面具 (dm) 用于 写 数据

•

自动 预充电 选项 用于 每个 突发 访问权限

•

sstl_2 兼容 我/o

•

可编程 突发 长度 (bl): 2, 4, 8

•

可编程 /cas 延迟 (cl): 3

•

可编程 输出 驾驶员强度: 正常/弱

•

刷新 循环次数: 4096 刷新 循环次数/64ms

15.6

µ

s 最大值 平均值 周期性 刷新 时间间隔

•

2 变化 的 刷新

自动 刷新

自我 刷新

•

tsop (二) 包装 与 铅 免费 焊料 (sn-bi)

rohs 符合

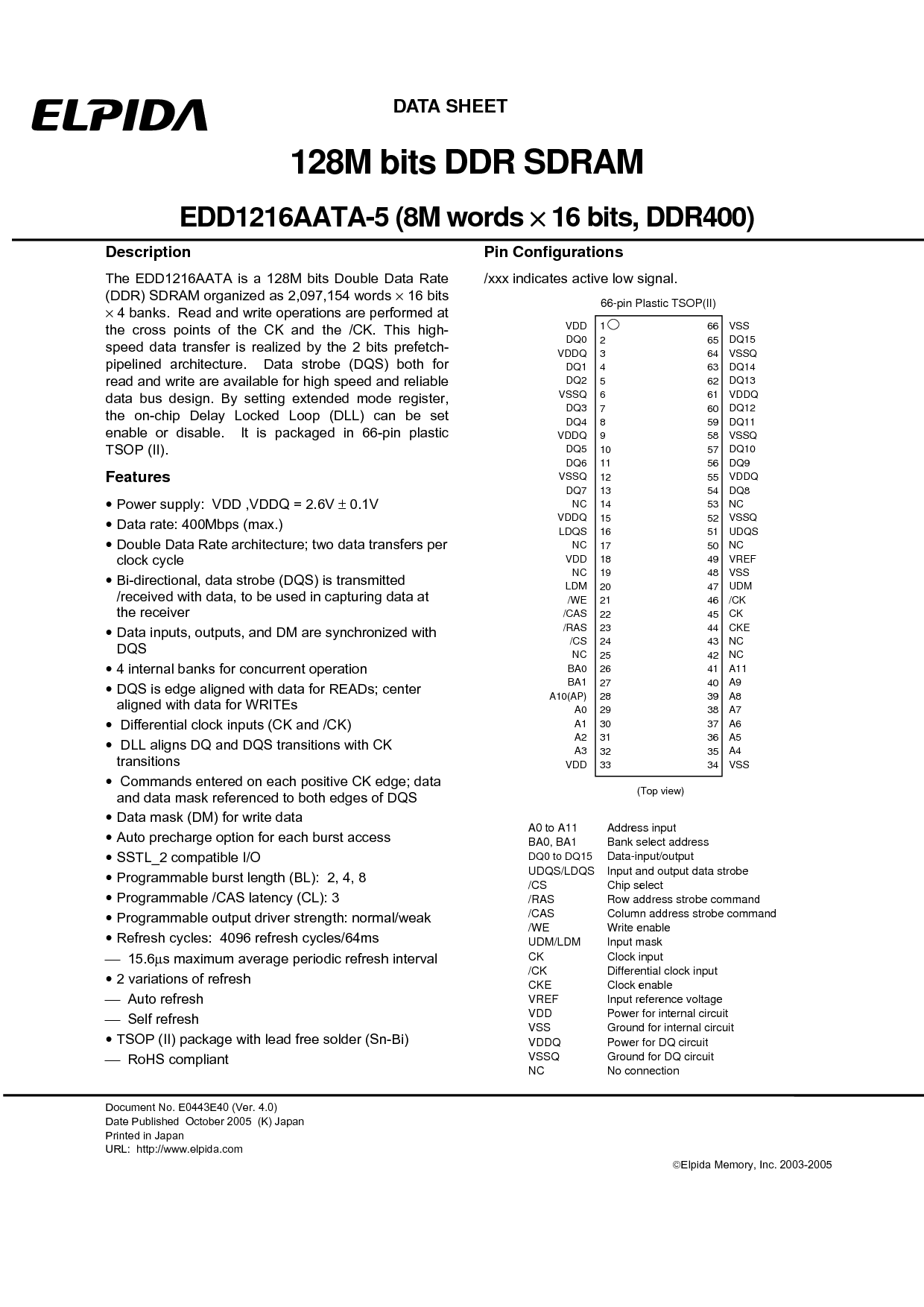

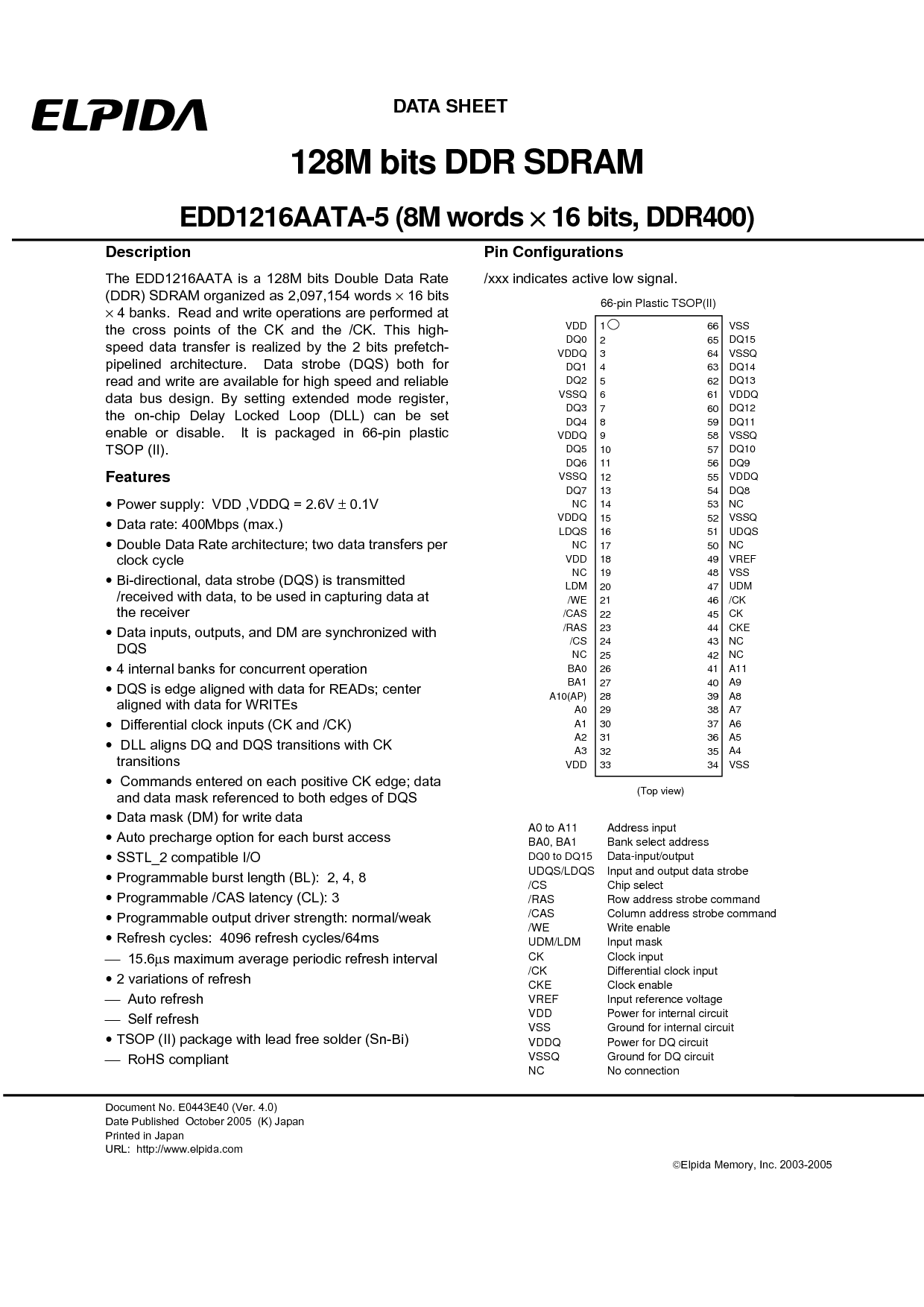

管脚 配置

/xxx 表示 活动 低 信号.

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

(顶部 查看)

VDD

DQ0

VDDQ

DQ1

DQ2

VSSQ

DQ3

DQ4

VDDQ

DQ5

DQ6

VSSQ

DQ7

nc

VDDQ

LDQS

nc

VDD

nc

LDM

/我们

/cas

/ras

/cs

nc

BA0

BA1

a10(ap)

A0

A1

A2

A3

VDD

vss

DQ15

VSSQ

DQ14

DQ13

VDDQ

DQ12

DQ11

VSSQ

DQ10

DQ9

VDDQ

DQ8

nc

VSSQ

UDQS

nc

VREF

vss

UDM

/ck

ck

CKE

nc

nc

A11

A9

A8

A7

A6

A5

A4

vss

地址 输入

银行 选择 地址

数据-输入/输出

输入 和 输出 数据 频闪

芯片 选择

行 地址 频闪 命令

色谱柱 地址 频闪 命令

写 启用

输入 面具

时钟 输入

差速器 时钟 输入

时钟 启用

输入 参考 电压

电源 用于 内部 电路

接地 用于 内部 电路

电源 用于 dq 电路

接地 用于 dq 电路

否 连接

a0 至 a11

ba0, ba1

dq0 至 dq15

udqs/ldqs

/cs

/ras

/cas

/我们

udm/ldm

ck

/ck

CKE

VREF

VDD

vss

VDDQ

VSSQ

nc

66-管脚 塑料 tsop(二)