1 pll 在系统内 可编程 时钟 generat或

与 个人 16k eeprom

CY27EE16Ze?

柏树 半导体 公司

• 3901 北 第一 街道 • San Jose

,

ca 95134 • 408-943-2600

文件 #: 38-07440 rev. *b 修订 六月 30, 2003

特点 好处

• 18 kbits 的 可擦可编程只读存储器

16 kbits 独立 划痕

2 kbits 专用 至 时钟 功能

较高 水平 的 集成 和 减少 组件 计数 由

组合 可擦可编程只读存储器 和 pll. 独立 可擦可编程只读存储器 将 是 已使用

用于 划痕 记忆, 或 至 商店 向上 至 八 时钟 配置

• 综合, 锁相 回路 与 可编程 p

和 q 计数器, 输出 分隔器, 和 可选

模拟 vcxo, 数字 vcxo, 传播 光谱 用于

emi 减少

高性能 pll 启用 控制 的 输出 频率 那 是

customizable 至 支持 一个 宽 范围 的 应用程序

• 入点 系统 可编程 通过 我

2

c 串行

编程 接口 (spi). 两者都有 这 sram 和

非挥发性 可擦可编程只读存储器 记忆 比特 是 程序-

mable 与 这 3.3v 供应

熟悉 行业 标准 缓解 编程 努力 和 启用

更新 的 数据 已存储 入点 16k 可擦可编程只读存储器 便签簿 和 2k 可擦可编程只读存储器

时钟 控制 块 同时 cy27ee16ze 是 已安装 入点 系统

• 低-抖动, 高精度 产出

满足 关键 计时 要求 入点 复杂 系统 设计

• vcxo 与 模拟 调整

写 保护 (wp 管脚) 可以 是 编程 至 服务 作为 一个 模拟

控制 电压 用于 一个 vcxo.这 vcxo 功能 是 仍然 可用 与

一个 dcxo, 或 d

igitally c控制 (通过 spi) 水晶 oscillator 如果 这

管脚 是 运作 作为 wp

• 3.3v 操作 (可选 2.5v 产出)

满足 行业标准 电压 platforms

• 20-铅 暴露 衬垫, ep-tssop

行业 标准 包装 保存 开启 板 空间

零件 号码 产出 输入 频率 范围 输出 频率 范围

CY27EE16ZE 6 1 – 167 mhz (驱动 时钟 输入) {commercial}

1 –150 mhz (驱动 时钟 输入) {industrial}

8 – 30 mhz (水晶 参考) {comm. 或 指示.}

80 khz – 200 mhz (3.3v) {commercial}

80 khz –167 mhz (3.3v) {industrial}

80 khz –167 mhz (2.5v) {commercial}

80 khz – 150 mhz (2.5v) {industrial}

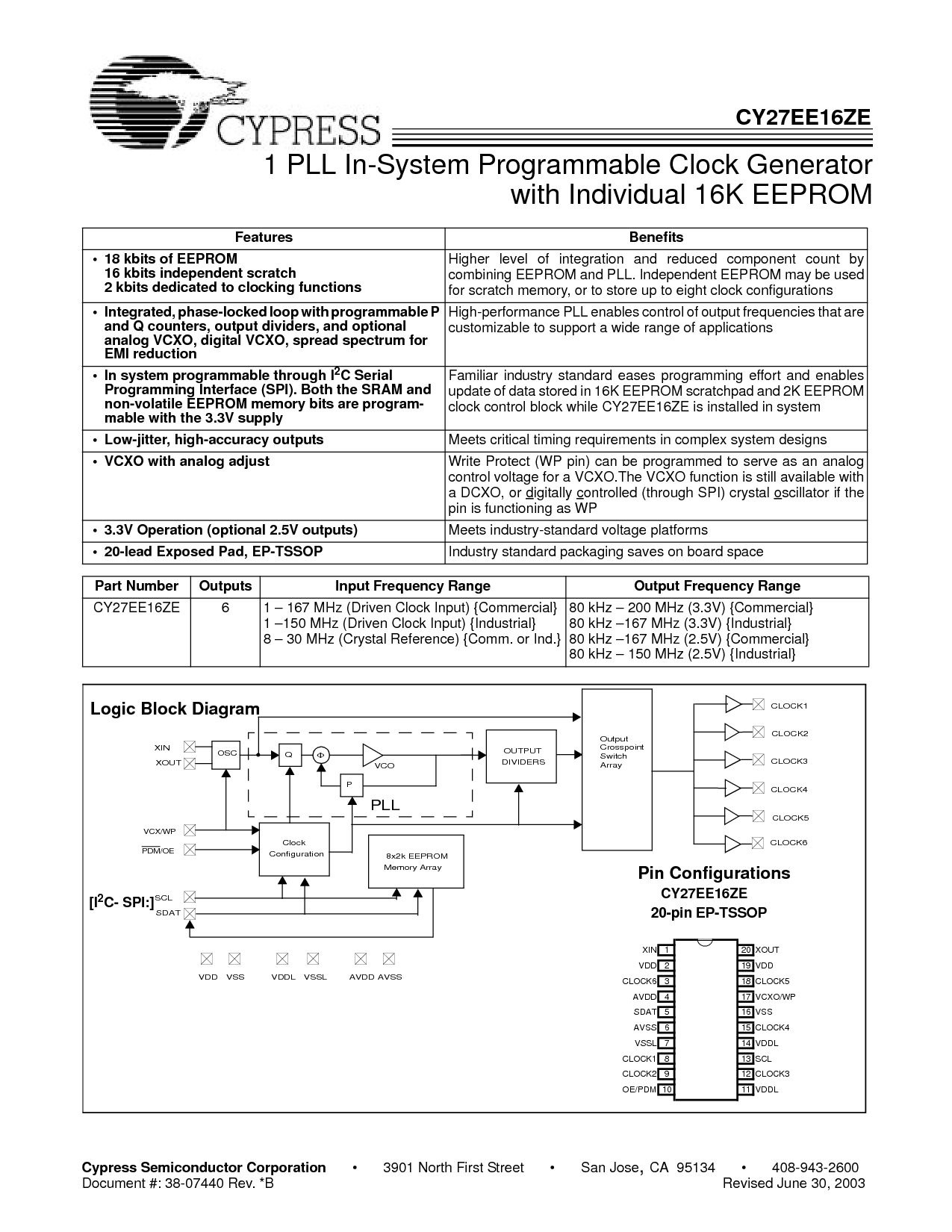

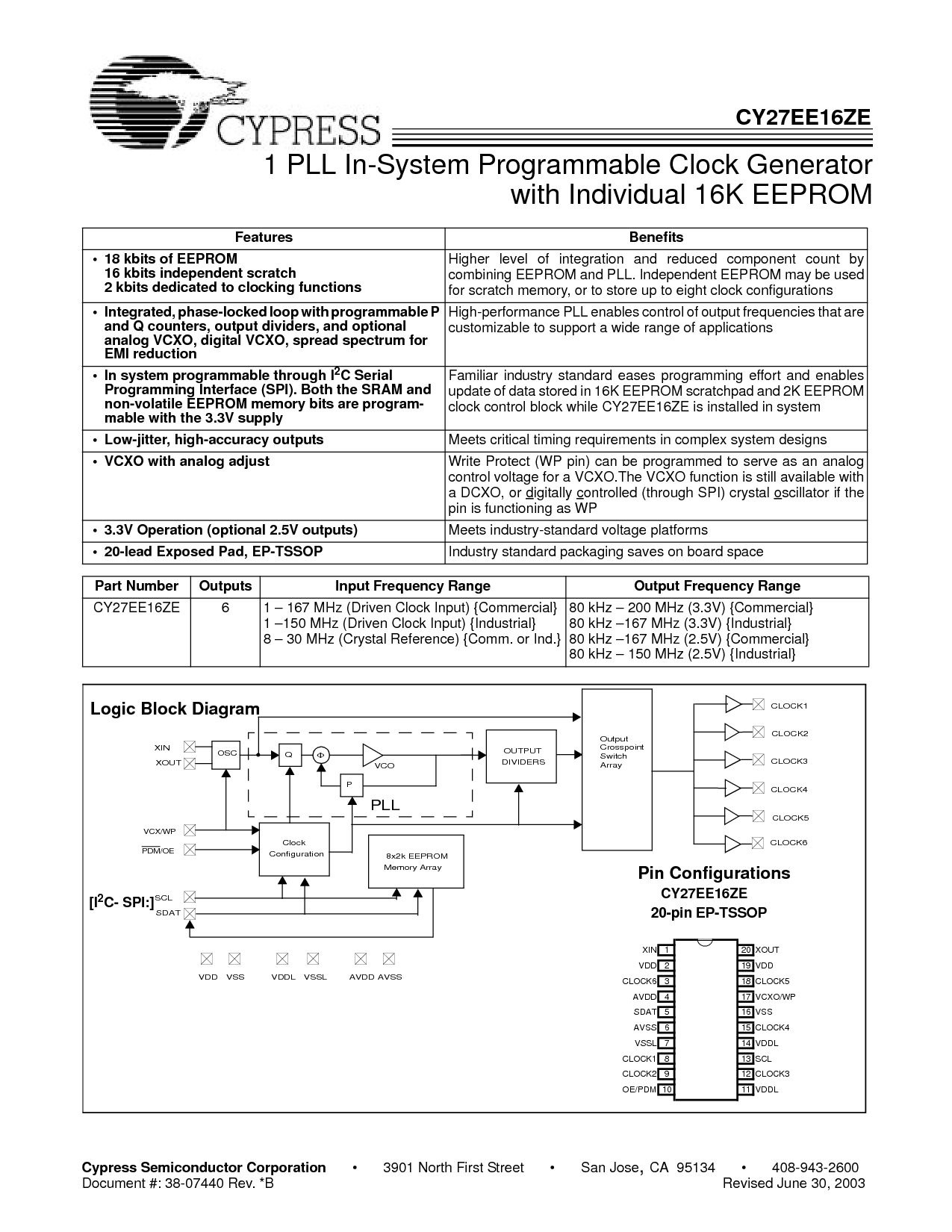

逻辑 块 图表

新

XOUT

CLOCK2

输出

分隔器

PLL

osc

CLOCK1

q

VCO

VDD vss

Φ

CLOCK3

p

管脚 配置

scl

SDAT

8x2k 可擦可编程只读存储器

记忆 阵列

时钟

配置

输出

交叉点

开关

阵列

CLOCK5

CLOCK4

CLOCK6

[I

2

c- spi:]

20-管脚 ep-tssop

AVDD AVSSVDDL VSSL

CY27EE16ZE

PDM/oe

新 1 20 XOUT

VDD 2 19 VDD

CLOCK6 3 18 CLOCK5

AVDD 4 17 vcxo/wp

SDAT 5 16 vss

AVSS 6 15 CLOCK4

VSSL 7 14 VDDL

CLOCK1 8 13 scl

CLOCK2 9 12 CLOCK3

oe/pdm 10 11 VDDL

vcx/wp