hy57v161610et-我

2 银行 x 512k x 16 有点 同步 dram

这个 文件 是 一个 概述 产品 描述 和 是 主题 至 变更 无 通知. hynix 半导体 是否 不 假设 任何责任 用于

使用 的 电路 已描述. 否专利 许可证 是 默示

rev. 0.1 / 十一月 20031

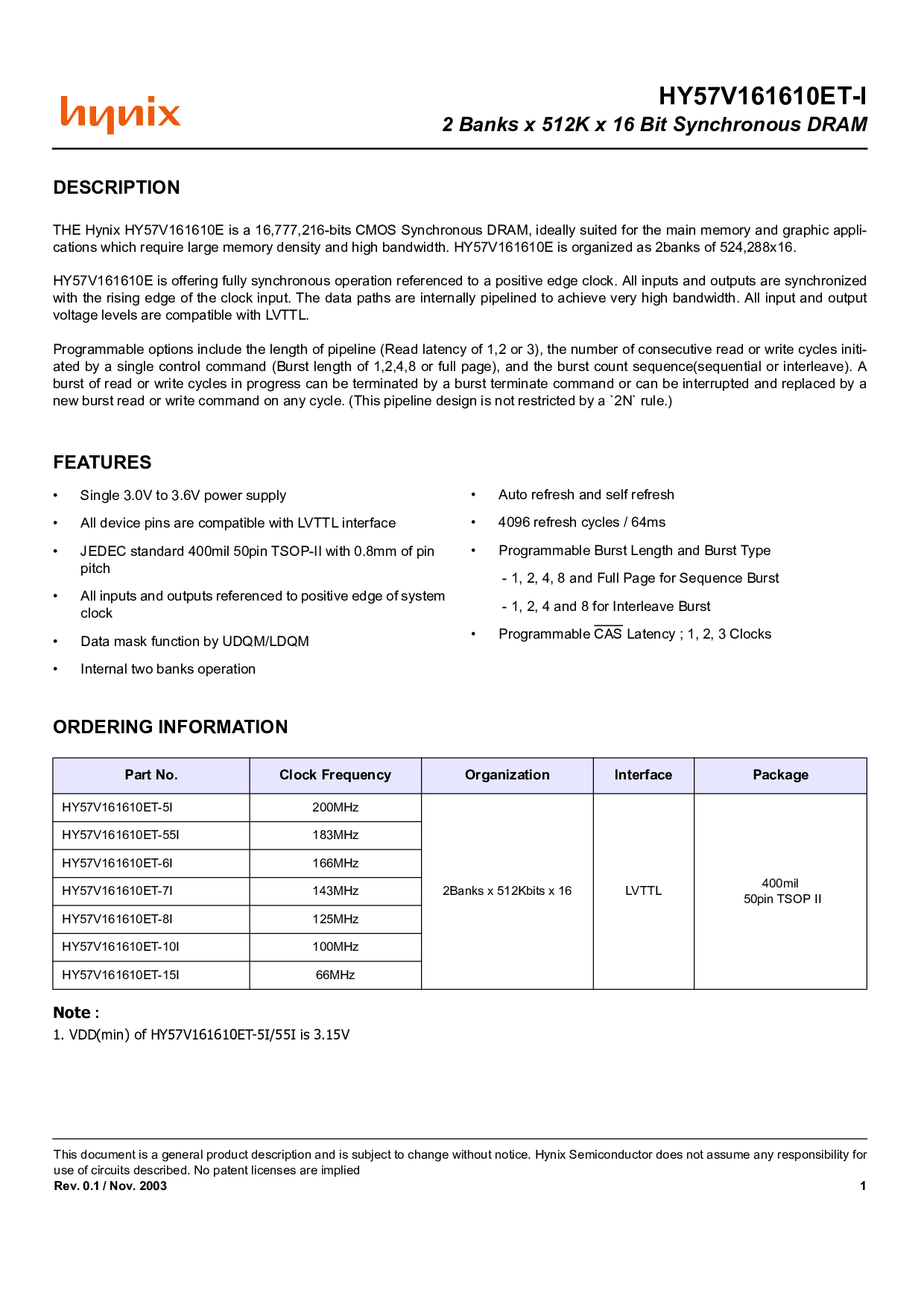

描述

这 hynix hy57v161610e 是 一个 16,777,216-bits cmos 同步 dram, 理想情况下 适合 用于 这 主 记忆 和 图形 应用程序-

阳离子 哪个 需要 大型 记忆 密度 和 高 bandwidth. hy57v161610e 是 organized 作为 2banks 的 524,288x16.

hy57v161610e 是 提供 完全 同步 操作 引用 至一个 正 边缘 时钟. 全部 输入 和 产出 是 synchronized

与 这 上升 边缘 的 这 时钟 输入. 这 数据 路径 是 内部 流水线 至 实现 很 高 带宽. 全部 输入 和输出

电压 级别 是 兼容 与 lvttl.

可编程 选项 包括 这 长度 的 管道 (阅读 延迟 的 1,2 或 3), 这 号码 的 连续的 阅读 或 写 循环次数initi-

已测试 由 一个 单独 控制 命令 (突发 长度 的 1,2,4,8 或已满 第页), 和 这 突发 计数 顺序(顺序 或 交错). 一个

突发 的 阅读 或 写 循环次数 入点 进度 可以 是 已终止 由 一个突发 终止 命令 或 可以 是 已中断 和 已更换 由一个

新建 突发 阅读 或 写 一氧化碳mmand 开启 任何 循环. (这个 pipeline 设计 是 不 restricted 由 一个 `2n` 规则.)

特点

• 单独 3.0v 至 3.6v 电源 供应

• 全部 设备 针脚 是 兼容 与 lvttl 接口

• 电子元件工业联合会 标准 400mil 50pin tsop-二 与 0.8mm 的 管脚

变桨

• 全部 输入 和 产出 referenced 至 正 边缘 的 系统

时钟

• 数据 面具 功能 由 udqm/ldqm

• 内部 两个 银行 操作

• 自动 刷新 和 自我 刷新

• 4096 刷新 循环次数 / 64ms

• 可编程 突发 长度 和 突发 类型

- 1, 2, 4, 8 和 已满 第页 用于 顺序 突发

- 1, 2, 4 和 8 用于 交错 突发

• 可编程 cas

延迟 ; 1, 2, 3 时钟

订购 信息

零件 否. 时钟 频率 组织机构 接口 包装

hy57v161610et-5i 200MHz

2banks x 512kbits x 16 LVTTL

400mil

50pin tsop 二

hy57v161610et-55i 183MHz

hy57v161610et-6i 166MHz

hy57v161610et-7i 143MHz

hy57v161610et-8i 125MHz

hy57v161610et-10i 100MHz

hy57v161610et-15i 66MHz

备注

:

1. vdd(最小) 的 hy57v161610et-5i/55i 是 3.15v