4-209

快 和 ls ttl 数据

双 1-的-4 解码器

与 3-州 产出

这MC54/74f539 包含 两个 独立 解码器. 每个 接受 两个

地址(一个

0

–一个

1

) 输入 信号 和 解码 他们 至 选择 一个 的 四

相互独占 产出. 一个 极性 控制 输入 (p) 确定 是否 这

产出是 活动 高 (p = l) 或 活动 低 (p = h). 一个 活动 低 输入

启用 (e?

) 是 可用 用于 数据 解复用; 数据 是 已布线至 这 已选择

输出入点 非倒置 窗体 入点 这 活动 低 模式 或 入点 倒置 窗体 入点 这

活动高 模式. 一个 高 信号 开启 这 活动 低 输出 启用 (oe

)

输入 力 这 3-州 产出 至 这 高 阻抗 州.

•

解复用 能力

•

3-州 产出

•

两个 完全 独立 1-的-4 解码器

•

输入 卡箍 二极管 限制 高 速度 终止 效果

•

esd 保护 > 4000 伏特

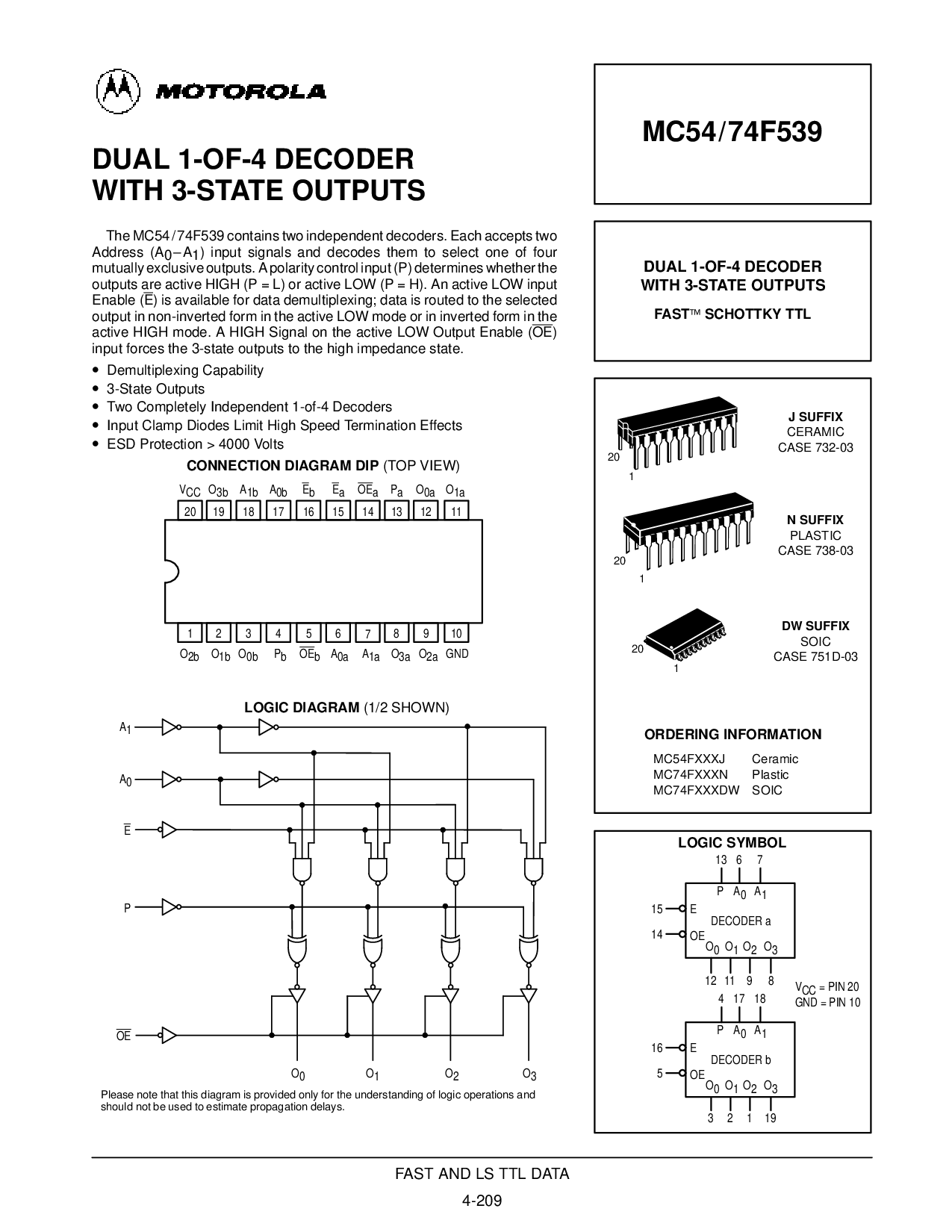

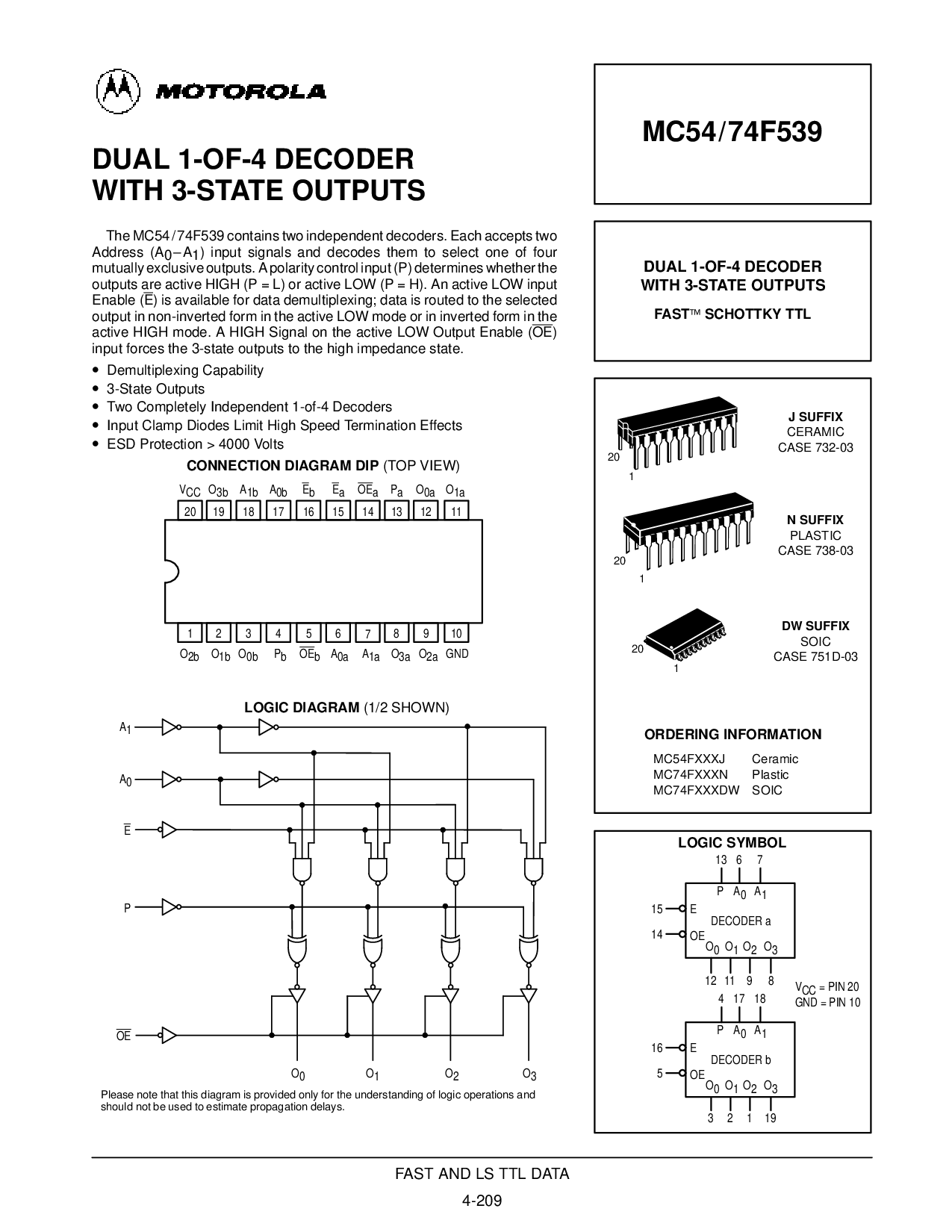

连接 图表 倾角

(顶部 查看)

18 17 16 15 14 13

1 2 3 4 5 6

7

20 19

8

v

抄送

o

2b

o

3b

一个

1b

一个

0b

e?

b

oe

一个

e?

一个

p

一个

o

1b

o

0b

oe

b

一个

0a

一个

1a

o

3a

o

2a

9 10

地

12 11

o

1a

p

b

o

0a

MC54/74F539

双 1-的-4 解码器

与 3-州 产出

快

肖特基 ttl

订购 信息

MC54FXXXJ 陶瓷

MC74FXXXN 塑料

MC74FXXXDW SOIC

20

1

j 后缀

陶瓷

案例 732-03

20

1

n 后缀

塑料

案例 738-03

20

1

dw 后缀

SOIC

案例 751d-03

逻辑 符号

v

抄送

= 管脚 20

地 = 管脚 10

一个

0

一个

1

p

o

0

o

1

o

2

o

3

e?

oe

解码器 一个

一个

0

一个

1

p

o

0

o

1

o

2

o

3

e?

oe

解码器 b

13 6 7

15

14

12 11 9 8

4 17 18

16

5

3 2 1 19

逻辑 图表

(1/2 显示)

一个

1

一个

0

e?

p

oe

o

0

o

1

o

2

o

3

请备注 那 这个 图表 是 提供 仅 用于 这 理解 的 逻辑 运营 和

应该 不 是 已使用 至 估算 传播 延误.