1

ispGDX

tm

160v/va

在系统内 可编程

3.3v 通用 数字 交叉点

tm

功能 块 图表特点

• 在系统内 可编程 通用 数字

交叉点 家庭

— 高级 体系结构 地址 可编程

pcb 互连, 总线 接口 集成 和

跳线/开关 更换

— “any 输入 至 任何 output” 路由

— 固定 高 或 低 输出 选项 用于 跳线/倾角

开关 仿真

— 节省空间 pqfp 和 bga 包装

— 专用 ieee 1149.1-符合 边界 扫描

测试一下

• 高 业绩 e?

2

CMOS

®

技术

— 3.3v 核心 电源 供应

— 3.5ns 输入-至-输出/3.5ns 时钟到输出 delay*

— 250mhz 最大值 时钟 frequency*

— ttl/3.3v/2.5v 兼容 输入 阈值 和

输出 级别 (单独 可编程)*

— 低-电源: 16.5ma 静态 icc*

— 24ma 我

ol

驱动器 与 可编程 回转 费率

控制 选项

— pci 兼容 驱动器 capability*

— 施密特 触发器 输入 用于 噪声 免疫

— 电气 可擦除 和 可重新编程

— 非挥发性 e?

2

cmos 技术

• ispgdxv™ 优惠 这 以下内容 优点

— 3.3v 在系统内 可编程 使用 边界 扫描

测试一下 访问权限 港口 (轻敲)

— 变更 互连 入点 秒

• 灵活 体系结构

— 组合/锁定/已注册 输入 或 产出

— 个人 我/o 三态 控制 与 极性 控制

— 专用 时钟/时钟 启用 输入 针脚 (四) 或

可编程 时钟/时钟 启用 从 我/o 针脚

(40)

— 单独 水平 4:1 动态 路径 选择(tpd = 3.5ns)

— 可编程 宽-mux 级联 功能

支架 向上 至 16:1 mux

— 可编程 拉-ups, 总线 保持 门闩 和 打开

排水管 开启 我/o 针脚

— 产出 三态 期间 通电 (“live insertion”

友好)

• 设计 支持 通过 lattice’s ispgdx

发展 软件

— ms 窗户 或 nt / pc-基于 或 太阳 o/s

— 容易 文本-基于 设计 进入

— 自动 信号 路由

— 程序 向上 至 100 isp 设备 同时

— 模拟器 网表 世代 用于 容易 板级

仿真

* “va” 版本 仅

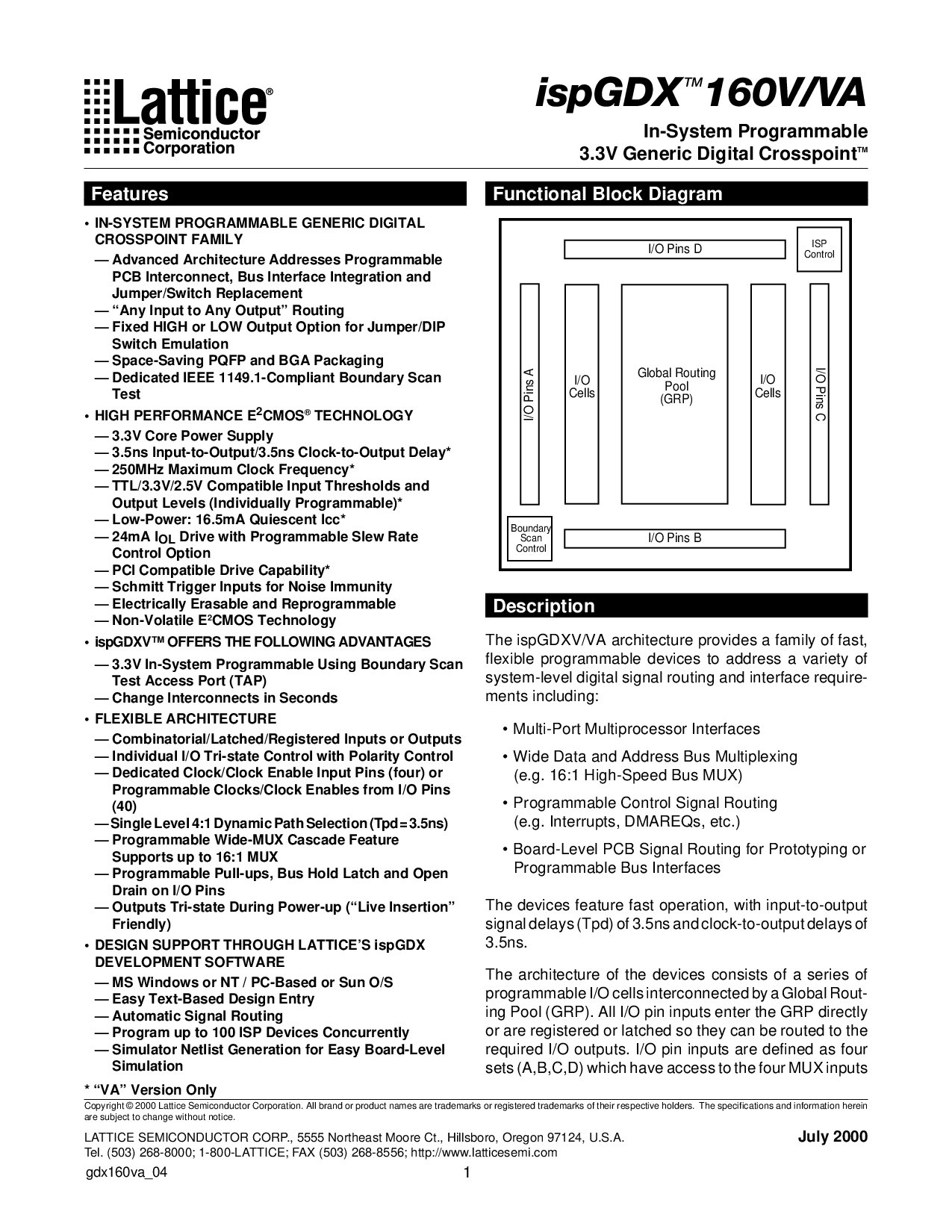

全球 路由

游泳池

(grp)

我/o

细胞

我/o 针脚 b

边界

扫描

控制

我/o

细胞

ISP

控制

我/o 针脚 一个

我/o 针脚 c

我/o 针脚 d

描述

这 ispgdxv/va 体系结构 提供 一个 家庭 的 快,

灵活 可编程 设备 至 地址 一个 品种 的

系统级 数字 信号 路由 和 接口 需要-

部分 包括:

• 多-港口 多处理机 接口

• 宽 数据 和 地址 总线 多路复用

(e?.g. 16:1 高速 总线 mux)

• 可编程 控制 信号 路由

(e?.g. 中断, dmareqs, 等等.)

• 板级 pcb 信号 路由 用于 原型设计 或

可编程 总线 接口

这 设备 功能 快 操作, 与 输入-输出

信号 延误 (tpd) 的 3.5ns 和 时钟到输出 延误 的

3.5ns.

这 体系结构 的 这 设备 由 的 一个 系列 的

可编程 我/o 细胞 互联互通 由 一个 全球 溃败-

ing 游泳池 (grp). 全部 我/o 管脚 输入 输入 这 grp 直接

或 是 已注册 或 锁定 所以 他们 可以 是 已布线 至 这

必填项 我/o 产出. 我/o 管脚 输入 是 已定义 作为 四

集 (一个,b,c,d) 哪个 有 访问权限 至 这 四 mux 输入

gdx160va_04

版权 © 2000 lattice 半导体 公司. 全部 品牌 或 产品 姓名 是 商标 或 已注册 商标 的 他们的 各自 持有人. 这 规格 和 信息 此处

是 主题 至 变更 无 通知.

lattice 半导体 corp., 5555 northeast moore ct., hillsboro, oregon 97124, 美国

july 2000

电话. (503) 268-8000; 1-800-lattice; 传真 (503) 268-8556; http://www.latticesemi.com